## **General Description**

TheEC9223 is an integrated power supply solution optimized for small to medium size thin- film transistor (TFT) liquid crystal displays (LCD's). The boost converter operates at a fixed frequency of 1.2MHz. The integrated N-channel FET has a current limit of 1.8A. The positive and negative charge pumps provide regulated TFT LCD gate-on and gate-off supplies. Both outputs can be adjusted by external resistive voltage dividers.

The integrated operational amplifier is typically used for LCD VCOM driving; the output can sink or source up to 150mA short-circuit current. A built-in voltage detector generates a reset signal when the input voltage drops below 2.6V. The reset signal is active low and has a 123ms blanking time during power-on. The EC9223 is available in a thin 16-pin 3x3 mm WQFN green package.

## **Features**

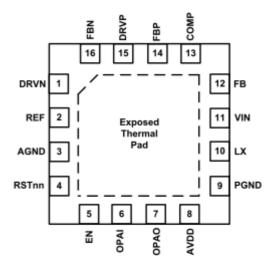

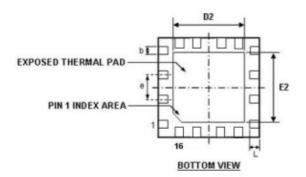

## **QFN-16 Pin Configuration**

- ♦ 2.5V to 5.5V input supply

- Active-high Enable Control

- ◆ Current-mode boost regulator

- 1.2MHz switching frequency

- Integrated 20V/1.8A 700m $\Omega$  FET

- Fast transient response to pulsed load

- High efficiency up to 90%

- Adjustable high-accuracy output voltage(±1%)

- ◆ VGH positive charge pump

- VGL negative charge pump

- ◆ Integrated unity-gain Vсом buffer

- ±150mA output current limit

- 12V/us slew rate

- 12MHz Bandwidth

- Low-voltage detection circuit

- ♦ Soft-start and timed delay fault latch for all outputs

- Thermal shutdown

- Thin 3x3 mm 16-lead WQFN package

# **Applications**

- ♦ TFT LCD for Notebooks

- Tablet Personal Computer Display

- Car Navigation Display

- Portable equipment

## **PIN DESCRIPTION**

| Number | Name  | Pin Description                                                             |  |  |  |

|--------|-------|-----------------------------------------------------------------------------|--|--|--|

| 1      | DRVN  | Negative charge pump driver output.                                         |  |  |  |

| 2      | REF   | Reference output. All power outputs are disabled until REF exceeds its UVLO |  |  |  |

| 3      | AGND  | Analog ground.                                                              |  |  |  |

| 4      | RSTnn | Voltage detector output. RSTnn is an active-low open-drain output.          |  |  |  |

| 5      | EN    | Enable control input pin. This pin has a 4uA pull-down current source.      |  |  |  |

| 6      | OPAI  | Unity-gain buffer input pin.                                                |  |  |  |

| 7      | OPAO  | Unity-gain buffer output pin.                                               |  |  |  |

| 8      | AVDD  | Charge pump and unity-gain buffer supply.                                   |  |  |  |

| 9      | PGND  | Boost converter power ground (source of the internal NMOS switch).          |  |  |  |

| 10     | LX    | Boost converter switching node (drain of the internal NMOS switch).         |  |  |  |

| 11     | VIN   | Supply for PWM, reference and other circuits.                               |  |  |  |

| 12     | FB    | Boost converter feedback voltage input.                                     |  |  |  |

| 13     | COMP  | Boost converter error amplifier compensation node.                          |  |  |  |

| 14     | FBP   | Positive charge pump feedback input.                                        |  |  |  |

| 15     | DRVP  | Positive charge pump driver output.                                         |  |  |  |

| 16     | FBN   | Negative charge pump feedback input.                                        |  |  |  |

| -      | TP    | Thermal Pad, connect to AGND.                                               |  |  |  |

# **Ordering Information**

| Part Number | Package  | Marking       | Marking Information |

|-------------|----------|---------------|---------------------|

| EC9223NNQ1R | WQFN 16L | 9223<br>LLLLL | 1. LLLLL : Lot No   |

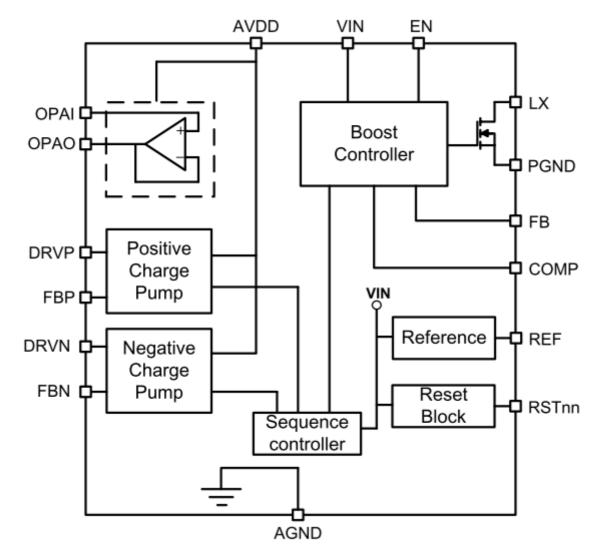

# **Function Block Diagram**

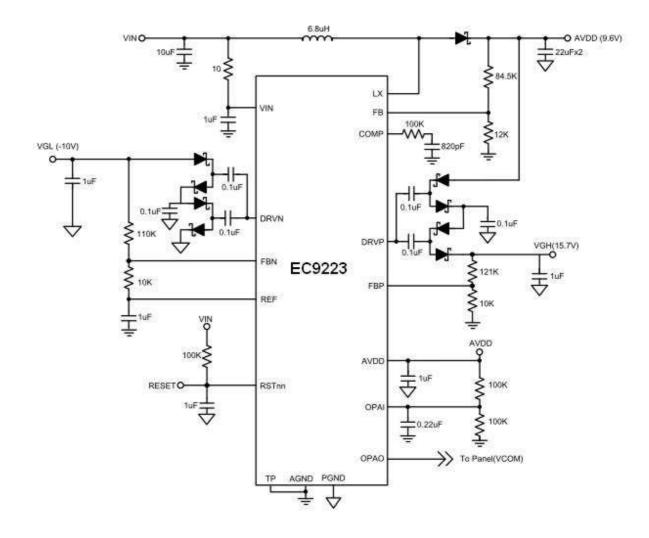

# **Typical Application Diagram**

# **Absolute Maximum Ratings**

| Input Supply Voltage, VIN                 | -0.3V to 6.5V        |

|-------------------------------------------|----------------------|

| Voltages on EN, RSTnn                     | -0.3V to 6.5V        |

| Voltages on AVDD, LX                      | -0.3V to 22V         |

| Voltages on FB, FBP, FBN, COMP, REF       | -0.3V to (VIN+0.3V)  |

| Voltages on DRVP, DRVN, OPAI, OPAO        | -0.3V to (AVDD+0.3V) |

| Storage temperature range                 | -65℃ to 150℃         |

| Lead temperature (soldering, 10s maximum) | 260°C                |

| ESD, Human body mode                      | 2kV                  |

| ESD, Machine mode                         | 200V                 |

Note1: All voltages are referenced to ground with PGND and AGND pins grounded.

Note2: "ABSOLUTE MAXIMUM RATINGS" indicate limits beyond which permanent damage to the device may occur. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. For guaranteed specifications and test conditions, see the "ELECTRICAL SPECIFICATIONS".

# **Recommended Operation Conditions**

| Junction temperature range | -40℃ to 125℃ |

|----------------------------|--------------|

| Ambient temperature range  | -40℃ to 85℃  |

# **Power Dissipation Ratings**

| Package   | Thermal Resistance, | Power Rating | Power Rating       | Power Rating |

|-----------|---------------------|--------------|--------------------|--------------|

|           | OJA                 | (TA < 25 ℃ ) | (25 < TA < 85 ℃ )  | (TA = 85℃)   |

| 16-ld QFN | 103℃ /W             | 1.25W        | (125 - TA) / 103 W | 0.39W        |

# **Electrical Specifications**

(VIN=3.3V, AVDD = 8.5V, TA=25°C, unless otherwise specified)

| Parameter                              | Symbol | Test Conditions                                                            | Min   | Тур  | Мах   | Units |

|----------------------------------------|--------|----------------------------------------------------------------------------|-------|------|-------|-------|

|                                        |        | System Supply                                                              |       |      |       |       |

| Input Supply Voltage                   | Vin    |                                                                            | 2.5   |      | 5.5   | V     |

| VIN Under Voltage Lockout              | Vuvlo  | VIN rising                                                                 | 1.8   | 2.0  | 2.2   | V     |

| VIN Under Voltage Lockout              | Vuvlo  | Hysteresis                                                                 |       | 0.1  |       | V     |

| VIN Quiescent current                  | lq     | VFB = 1.35V, LX no switching                                               |       | 0.3  |       | mA    |

| VIN Quiescent current                  | lq     | VFB = 1.15V, LX switching                                                  |       | 0.8  |       | mA    |

| EN Threshold                           | Vін    |                                                                            | 2     |      |       |       |

| EN Threshold                           | VIL    |                                                                            |       |      | 0.8   | V     |

| Thermal shutdown                       | TSHDN  |                                                                            |       | 150  |       | °C    |

|                                        |        | Main Boost Regulator                                                       |       |      |       |       |

| FB Regulation Voltage                  | Vfb    |                                                                            | 1.188 | 1.2  | 1.212 | V     |

| FB Fault Trip Level                    |        | Falling edge                                                               |       | 0.95 |       | V     |

| FB Load Regulation                     |        | 0< Iload < full                                                            |       | -1   |       | %     |

| FB Line Regulation                     |        | VIN = 2.5 to 5.5V                                                          |       | 0.15 | 0.25  | %/V   |

| FB Input Bias Current                  |        | VFB = 1.25V                                                                | -40   | 0    | 40    | nA    |

| FB Transconductance                    | Gm     | $\Delta I=\pm 5uA$ at COMP, FB = COMP                                      |       | 70   |       | uA/V  |

| FB Voltage Gain                        | Av     | FB to COMP                                                                 |       | 1500 |       | V/V   |

| LX Current Limit                       |        | VFB =1.1V, duty cycle = 75%                                                | 1.4   | 1.8  | 2.2   | А     |

| LX On-Resistance                       | Rds_LX | ILX = 200mA                                                                |       | 0.7  |       | Ω     |

| LX Leakage Current                     |        | VLX = 19V, TA = +25℃                                                       |       | 0.1  | 10    | uA    |

| Current-Sense Transresistance          |        |                                                                            |       | 0.35 |       | V/A   |

| Maximum Duty Cycle                     | DUTY   |                                                                            | 85    | 90   | 94    | %     |

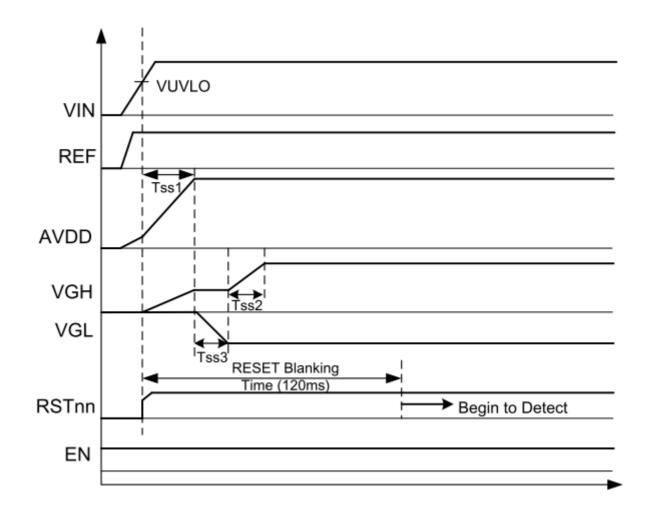

| Soft-Start Period                      | Tss1   |                                                                            |       | 7    |       | ms    |

|                                        |        | Reference                                                                  | 1     |      |       | 1     |

| REF OUTPUT Voltage                     | Vref   | IREF=50uA                                                                  | 1.176 | 1.20 | 1.224 | V     |

| REF Load Regulation                    | IREF   | 0 <iload <100ua<="" td=""><td></td><td>1</td><td>5</td><td>mV</td></iload> |       | 1    | 5     | mV    |

| REF Line Regulation                    |        | IREF = 100uA<br>VIN=2.5V to 5.5V                                           |       | 2    | 5     | mV    |

|                                        |        | Oscillator and Timing                                                      |       |      | 1     |       |

| Frequency                              | Fosc   |                                                                            | 900   | 1200 | 1500  | KHz   |

| Duration to Trigger Fault<br>Condition |        | FB or FBP or FBN below<br>threshold                                        |       | 100  |       | ms    |

# Multi-Channel TFT LCD Supply

|                                    | Posi      | tive Charge-Pump Regulator                        |                | 1              |       |      |

|------------------------------------|-----------|---------------------------------------------------|----------------|----------------|-------|------|

| AVDD Supply Range                  | Vavdd     |                                                   | 6              |                | 16    | V    |

| Operating Frequency                | Fosc_cp   |                                                   |                | 600            |       | KHz  |

| FBP Regulation Voltage             | Vfbp      |                                                   | 1.176          | 1.2            | 1.224 | V    |

| FBP Input Bias Current             | IFBP_BIAS | Vfbp =1.5V, Ta = +25℃                             | -40            | -              | 40    | nA   |

| DRVP P-Ch On-Resistance            | Rdrvpp    |                                                   |                | 20             |       | Ω    |

| DRVP N-Ch On-Resistance            | Rdrvpn    | VAVDD=10V,IDRVP=20mA                              |                | 20             |       | Ω    |

| FBP Fault Trip Level               |           | Falling edge                                      |                | 0.95           |       | V    |

| Soft-Start Period                  | TSS2      |                                                   |                | 5              |       | ms   |

|                                    | Nega      | tive Charge-Pump Regulator                        | -              |                |       |      |

| AVDD Supply Range                  | Vavdd     |                                                   | 6              |                | 16    | V    |

| Operating Frequency                | Fosc_cp   |                                                   |                | 600            |       | KHz  |

| FBN Regulation Voltage             | Vfbn      |                                                   | 210            | 240            | 270   | mV   |

| FBN Input Bias Current             | IFBN_BIAS | Vfbn = 0V, Ta = +25℃                              | -40            | -              | 40    | nA   |

| DRVN P-Ch On-Resistance            | Rdrvnp    |                                                   |                | 20             |       | Ω    |

| DRVN N-Ch On-Resistance            | Rdrvnn    | VAVDD=10V,IDRVN=20mA                              |                | 20             |       | Ω    |

| FBN Fault Trip Level               |           | Rising edge                                       |                | 0.45           |       | V    |

| Soft-Start Period                  | Tss3      |                                                   |                | 5              |       | ms   |

|                                    |           | Operational Amplifier                             |                |                |       |      |

| AVDD Supply Range                  | Vavdd     |                                                   | 6              |                | 16    | V    |

| AVDD Supply Current                | Iavdd     | VOPAI= VAVDD/2, no load                           |                | 0.6            | 1.2   | mA   |

| Input Offset Voltage               | Vos       | Vopai =Vavdd/2, Ta = +25℃                         | -15            | 0              | 15    | mV   |

| Input Bias Current                 | IBIAS     | Vopai =Vavdd/2, Ta = +25℃                         | -100           |                | 100   | nA   |

| Input Common-Mode Voltage<br>Range |           |                                                   | 0              |                | VAVDD | V    |

|                                    |           | ΟΡΑΟ Ιουτ = 100μΑ                                 | Vavdd -<br>20  | Vavdd -<br>5   |       | mV   |

| Output-Voltage-Swing High          | VOH       | OPAO lout = 5 mA                                  | Vavdd -<br>200 | Vavdd -<br>150 |       | mV   |

|                                    |           | ΟΡΑΟ Ιουτ = -100μΑ                                |                | 5              | 20    | mV   |

| Output-Voltage-Swing Low           | VOL       | OPAO IOUT = -5 mA                                 |                | 150            | 200   | mV   |

| Slew Rate                          | SR        | VOPAO 20% to 80% with<br>CL=10pF, RL=10k          | 8              | 12             |       | V/us |

| -3dB Bandwidth                     | BW        | CL=10pF, RL=10k                                   |                | 12             |       | MHz  |

|                                    |           | VOPAI=VAVDD/2 , short output to<br>GND (sourcing) | 100            | 150            |       | mA   |

| Short-Circuit Current              | ISCC      | VOPAI=VAVDD/2 , short output to<br>AVDD (sinking) | 100            | 150            |       | mA   |

| Low-Voltage Detector |           |                     |  |     |     |    |

|----------------------|-----------|---------------------|--|-----|-----|----|

| Reset Threshold      | Vrst_th   | Falling edge at VIN |  | 2.6 |     | V  |

| Reset mieshold       | Vrst_hyst |                     |  | 100 |     | mV |

| RSTnn Output Voltage | Vrst      | ISINK = 1mA         |  |     | 0.4 | V  |

| Reset Blanking Time  | TBLK      |                     |  | 120 |     | ms |

#### **Application Information**

The EC9223 offers an all-in-one solution for TFT LCD. The chip includes a high-efficiency boost converter with a 20V/1.8A on-chip N-channel transistor for biasing of the LCD, a regulated positive charge pump, a regulated negative charge pump, and a unity-gain VCOM buffer. A voltage detector circuit generates a reset signal when the input voltage falls below 2.6V.

#### TFT LCD Boost Converter (AVDD)

The LCD panel AVDD supply is generated from a high-efficiency PWM boost converter operating with current mode control, and the switching frequency is 1.2MHz. During the on-period, TON, the synchronous FET connects one end of the inductor to ground, therefore increasing the inductor current. After the FET turns off, the inductor switching node, LX, is charged to a positive voltage by the inductor current. The freewheeling diode turns on and the inductor current flows to the output capacitor. The converter operates in the continuous conduction mode (CCM) when the average input current IIN is at least one-half of the inductor peak- to-peak ripple current, ΔlLPP.

$$I_{IN} \ge \frac{\Delta I_{LPP}}{2}$$

$$\Delta I_{LPP} = \frac{(AVDD - V_{IN}) \times V_{IN}}{L \times F_{OSC} \times AVDD}$$

The output voltage, AVDD, is determined by the duty cycle, D, of the power FET on-time and the input voltage,  $V_{IN}$ .

$$AVDD = \frac{V_{IN}}{1 - D}$$

The average load current, ILOAD, can be calculated from the power conservation law.

$$\eta \times V_{\text{IN}} \times I_{\text{IN}} = AVDD \times I_{\text{LOAD}}$$

where  $\eta$  is the power conversion efficiency. For a lower load current, the inductor current would decay to zero during the freewheeling period and the output node would be disconnected from the inductor for the remaining portion of the switching period. The converter would operate in the discontinuous conduction mode (DCM). Current mode control is well known for its robustness and fast transient response. An inner current feedback loop sets the on-time and the duty cycle such that the current through the inductor equals to the current computed by the compensator. This loop acts within one switching cycle. A slope compensation ramp is added to suppress sub-harmonic oscillations. An outer voltage feedback loop subtracts the voltage on the FB pin from the internal reference voltage and feeds the difference to the compensator operational transconductance (Gm) amplifier. This amplifier is compensated by an external R-C network to allow the user to optimize the transient response and loop stability for the specific application conditions.

#### Compensation

This current mode boost converter has a current sense loop and a voltage feedback loop. The current sense loop does not need any compensation. The voltage feedback loop is compensated by an external series R-C network RCOMP and CCOMP from COMP pin to ground. RCOMP sets the high-frequency loop gain and the unity gain bandwidth of the loop which determines the transient response. CCOMP together with RCOMP determine the phase margin which relates to loop stability.

#### **Output Capacitor Selection**

The output voltage ripple due to converter switching is determined by the output capacitor total capacitance, Cout, and the output capacitor total effective series resistance, ESR.

$$AVDD_{RIPPLE} = \frac{D \times I_{LOAD}}{F_{OSC} \times C_{OUT}} + I_{PK} \times ESR$$

$$I_{PK} = I_{IN} + \frac{\Delta I_{LPP}}{2}$$

The first ripple component can be reduced by increasing Cout. Changing Cout may require adjustment of compensation R and C in order to provide adequate phase margin and loop bandwidth. The second ripple component can be reduced by selecting low-ESR ceramic capacitors and using several smaller capacitors in parallel instead of just one large capacitor.

#### **Inductor Selection**

To prevent magnetic saturation of the inductor core the inductor has to be rated for a maximum current larger than IPK in a given application. Since the chip provides current limit protection of 1.8A (typ) it is generally recommended that the inductor be rated at least for 1.8A. Selection of the inductor requires trade-off between the physical size (footprint x height) and its electrical properties (current rating, inductance, resistance). Within a given footprint and height, an inductor with larger inductance typically comes with lower current rating and often larger series resistance. Larger inductance typically requires more turns on the winding, a smaller core gap or a core material with a larger relative permeability. An inductor with a larger physical size has better electrical properties than a smaller inductor.

It is desirable to reduce the ripple current  $\Delta$ ILPP in order to reduce voltage noise on the input and output capacitors. In practice, the inductor is often much larger than the capacitors and it is easier and cheaper to increase the size of the capacitors. The ripple current  $\Delta$ ILPP is then chosen the largest possible while at the same time not degrading the maximum input and output current that the converter can operate with before reaching the current limit of the chip or the rated current of the inductor.

$$I_{PK} = I_{IN} + \frac{\Delta I_{LPP}}{2} \le I_{MAX}$$

For example,  $\Delta I_{LPP}$  could be set to 20% of IMAX.

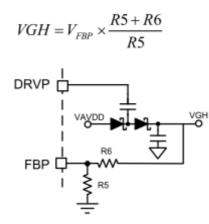

#### Positive Charge Pump (VGH)

The positive charge pump is used to generate the TFT LCD gate on voltage. The output voltage, VGH, can be set by an external resistive divider. Voltage V<sub>FBP</sub> is 1.2V. A single stage charge pump can produce an output voltage less than approximately twice the charge pump input voltage AVDD. The output voltage VGH is regulated as the following equation.

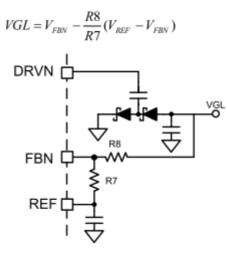

The negative charge pump is used to generate the TFT LCD gate off voltage. The output voltage, VGL, is set with an external resistive divider from its output to REF with the midpoint connected to FBN. The error amplifier compares the feedback signal from FBN with an internal reference 240mV. The output voltage VGL is regulated as the following equation. VREF is 1.2V.

#### **VCOM Buffer**

The Vcom buffer generates the bias supply for the back plane of an LCD screen which is capacitively coupled to the pixel drive voltage. The purpose of the Vcom buffer is to hold the bias voltage steady while pixel voltage changes dynamically. The buffer is designed to sustain up to  $\pm 75$ mA of output current. In transients, it can deliver up to 150mA at which point the over current protection circuit limits the output current. Excessive current draw over a period of time may cause the chip temperature to rise and set off the over temperature protection circuit.

#### Under Voltage Protection

During normal operation (after completing the soft start sequence) EC9223 constantly monitors feedback pins FB, FBP and FBN. A fault condition occurs if FB falls below 0.95V or FBP falls below 0.95V or FBN rises above 0.45V. If any of the fault conditions persist for longer than 100ms, the chip sets a fault latch and shuts down. To turn the power supplies back on requires cycling of VIN supply below the UVLO level or toggling the EN pin low and high. This will clear the fault latch and restore normal operation.

#### **Over Current Protection**

The EC9223 has Over-Current Protection (OCP) that limits the peak inductor current in every switching cycle. It prevents large current from damaging the inductor and diode. Once the inductor current exceeds the current limit, the internal switch turns off immediately and shortens the duty cycle. The output voltage drops if the over-current condition occurs. Current limit is affected by the input voltage, duty cycle, and inductor value.

#### **Thermal-Overload Protection**

The EC9223 boost converter provides Thermal-overload Protection to prevents excessive power dissipation from overheating the IC. When the junction temperature exceeds  $T_J = 150$ °C, a thermal sensor activates the fault protection, which shuts down all outputs. To resume normal operation the chip internal temperature must drop at least by 15°C. In addition, either the input supply must be cycled below the UVLO level or the EN pin must be toggled low and high to clear the fault latch.

#### **Voltage Detector Circuit**

The internal voltage detector circuit monitors the chip input voltage VIN. The chip can either drive RSTnn pin low or leave it floating. While floating, RSTnn is pulled high by an external pull up resistor. When VIN drops below 2.6V the chip pulls RSTnn pin low. In order to release RSTnn the VIN voltage must rise above 2.7V. The voltage detector circuit is disabled and RSTnn is floating while the chip is disabled and for 123ms from the time the chip is enabled (VIN>UVLO and EN is high).

#### Start-Up and Power-Off Control

The EC9223 employs EN pin to control the whole chip. Pulling EN high enables this device. When EN goes high, once reference voltage is ready, the boost convertor starts operating. To limit the supply inrush current during start up conditions, an internal soft-start circuitry is implemented. The soft-start circuitry will slowly ramp up the output voltage during soft-start period, the soft-start period is 7ms for AVDD and 5ms for VGH and VGL. The EC9223 shuts down to reduce the supply current when EN is low. In this mode, all the internal blocks turn off, and the n-channel MOSFET is turned off as well. The boost convertor's output is connected to VIN by the external inductor and rectifier diode.

# **Startup Sequence**

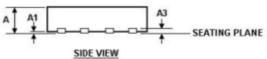

# Package Information (WQFN-16 3x3 mm)

| DIMENSION | MIN (mm)  | MAX (mm) |  |  |

|-----------|-----------|----------|--|--|

| A         | 0.70      | 0.80     |  |  |

| A1        | 0.00      | 0.05     |  |  |

| A3        | 0.20 REF  |          |  |  |

| b         | 0.18 0.30 |          |  |  |

| D         | 3.00 BSC  |          |  |  |

| D2        | 1.60      | 1.80     |  |  |

| E         | 3.00 BSC  |          |  |  |

| E2        | 1.60      | 1.80     |  |  |

| е         | 0.50 BSC  |          |  |  |

| L         | 0.30 0.45 |          |  |  |

Notes:

1) All dimensions are in millimeters.