#### **Features**

- Precision supply-voltage monitor

- 4.63V (PT7A7511, 7521, 7531)

- 4.38V (PT7A7512, 7522, 7532)

- 3.08V (PT7A7513, 7523, 7533)

- 2.93V (PT7A7514, 7524, 7534)

- 2.63V (PT7A7515, 7525, 7535)

- 200ms reset pulse width

- Debounced TTL/CMOS-compatible manualreset input

- Independent watchdog timer 1.6sec time-out (not available for PT7A7531 - 7535)

- Reset output signal:

- Active-low only (PT7A7511 7515)

- Active-high only (PT7A7521 7525)

- Active-high and active-low (PT7A7531 7535)

- Voltage monitor for power-fail or low battery warning

- Guaranteed RESET/RESET valid at V<sub>CC</sub>=1.2V

### **Description**

The PT7A751X/752X/753X family microprocessor (μP) supervisory circuits are targeted to improve reliability and accuracy of power-supply circuitry in μP's systems. These devices reduce the complexity and number of components required to monitor powersupply and battery functions.

The main functions are:

- 1. Asserting reset output during power-up, powerdown and brownout conditions for µP system.

- 2. Detecting power failure or low-battery conditions with a 1.25V threshold detector.

- 3. Watchdog functions (not for PT7A753x)

# **Applications**

• Power-supply circuitry in µP systems

**Ordering Information**

| Part Number | Package         | Part Number | Package                    |

|-------------|-----------------|-------------|----------------------------|

| PT7A751xPE  | Lead free DIP-8 | PT7A751xWE  | Lead free and Green SOIC-8 |

| PT7A752xPE  | Lead free DIP-8 | PT7A752xWE  | Lead free and Green SOIC-8 |

| PT7A753xPE  | Lead free DIP-8 | PT7A753xWE  | Lead free and Green SOIC-8 |

Note: "X" refers to voltage range, see below table.

Suffix: X—Monitored Voltage and Function Comparison

| Suma. A—Montored voltage and runction comparison |           |              |                            |                      |                |             |  |  |

|--------------------------------------------------|-----------|--------------|----------------------------|----------------------|----------------|-------------|--|--|

| Part No.                                         | Reset     | Reset Active | Nom. Reset                 | Nom. Watch dog       | Power Fail     | Manual      |  |  |

|                                                  | Threshold | Low or High  | Time (ms), t <sub>RS</sub> | Time (sec), $t_{WD}$ | Comp.          | Reset Input |  |  |

| PT7A7511                                         | 4.63V     | LOW          | 200                        | 1.6                  | 1.25V detector | Yes         |  |  |

| PT7A7521                                         | 4.63V     | HIGH         | 200                        | 1.6                  | 1.25V detector | Yes         |  |  |

| PT7A7531                                         | 4.63V     | LOW, HIGH    | 200                        | unavailable          | 1.25V detector | Yes         |  |  |

| PT7A7512                                         | 4.38V     | LOW          | 200                        | 1.6                  | 1.25V detector | Yes         |  |  |

| PT7A7522                                         | 4.38V     | HIGH         | 200                        | 1.6                  | 1.25V detector | Yes         |  |  |

| PT7A7532                                         | 4.38V     | LOW, HIGH    | 200                        | unavailable          | 1.25V detector | Yes         |  |  |

| PT7A7513                                         | 3.08V     | LOW          | 200                        | 1.6                  | 1.25V detector | Yes         |  |  |

| PT7A7523                                         | 3.08V     | HIGH         | 200                        | 1.6                  | 1.25V detector | Yes         |  |  |

| PT7A7533                                         | 3.08V     | LOW, HIGH    | 200                        | unavailable          | 1.25V detector | Yes         |  |  |

| PT7A7514                                         | 2.93V     | LOW          | 200                        | 1.6                  | 1.25V detector | Yes         |  |  |

| PT7A7524                                         | 2.93V     | HIGH         | 200                        | 1.6                  | 1.25V detector | Yes         |  |  |

| PT7A7534                                         | 2.93V     | LOW, HIGH    | 200                        | unavailable          | 1.25V detector | Yes         |  |  |

| PT7A7515                                         | 2.63V     | LOW          | 200                        | 1.6                  | 1.25V detector | Yes         |  |  |

| PT7A7525                                         | 2.63V     | HIGH         | 200                        | 1.6                  | 1.25V detector | Yes         |  |  |

| PT7A7535                                         | 2.63V     | LOW, HIGH    | 200                        | unavailable          | 1.25V detector | Yes         |  |  |

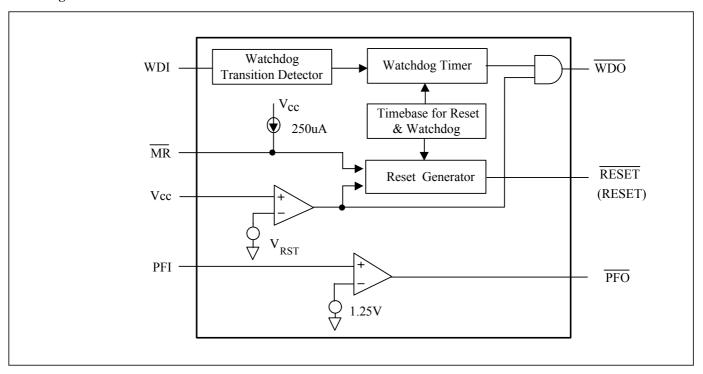

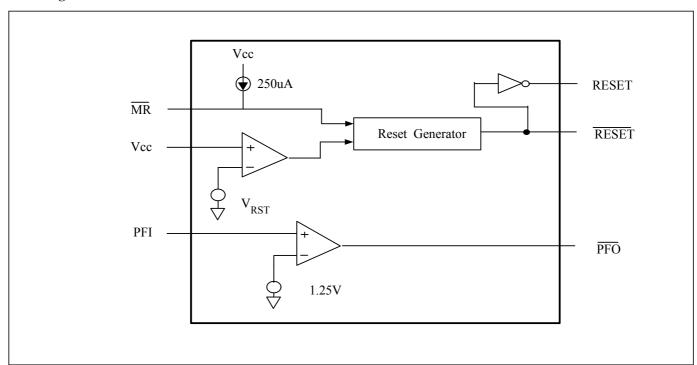

# **Block Diagram**

#### Block Diagram of PT7A7511-7515/7521-7525

### **Block Diagram of PT7A7531-35**

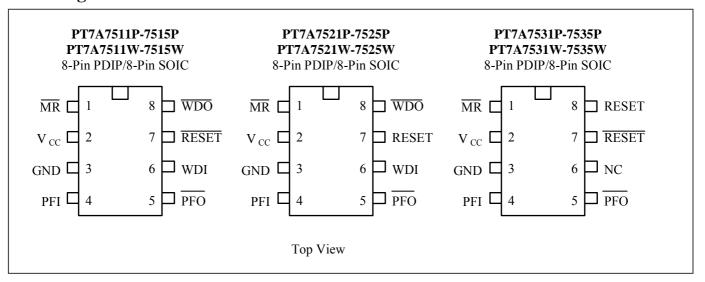

# **Pin Configuration**

Pin Description

| Pin Des         | cription |                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin             | Type     | Description                                                                                                                                                                                                                                                                                                                                                                                        |

| MR              | I        | <b>Manual-Reset:</b> triggers a reset pulse when pulled below 0.8V, active low. It has an internal 250mA pullup current and be driven from a TTL or CMOS logic line as well as shorted to ground with a switch.                                                                                                                                                                                    |

| V <sub>CC</sub> | Power    | Supply Voltage.                                                                                                                                                                                                                                                                                                                                                                                    |

| GND             | Ground   | Ground Reference for all signals.                                                                                                                                                                                                                                                                                                                                                                  |

| PFI             | I        | <b>Power-Fail Voltage Monitor Input.</b> When PFI is less than 1.25V, PFO goes low. Connect PFI to GND or Vcc when not used.                                                                                                                                                                                                                                                                       |

| PFO             | О        | <b>Power-Fail Output:</b> it gets low and sinks current when PFI is less than 1.25V; otherwise PFO stays high.                                                                                                                                                                                                                                                                                     |

| WDI             | I        | Watchdog Input: If WDI remains high or low for 1.6sec, the internal watchdog timer runs out and WDO goes low. Floating WDI or connecting WDI to a high-impedance three-state buffer disables the watchdog feature. The internal watchdog timer clears whenever reset is asserted. WDI is three-stated, or WDI sees a rising or falling edge.                                                       |

| RESET           | О        | <b>Reset Output pulses:</b> low for 200ms when triggered, and stays low whenever Vcc is below the reset threshold. It remains low for 200ms after Vcc rises above the reset threshold or $\overline{\text{MR}}$ goes from low to high. A watchdog timeout will not trigger RESET unless WDO is connected to MR.                                                                                    |

| WDO             | О        | Watchdog Output: pulls low when the internal watchdog timer finishes its 1.6sec count and does not go high again until the watchdog is cleared. WDO also goes low during low-line conditions. Whenever Vcc is below the reset threshold, WDO stays low; however, unlike RESET, WDO does not have minimum pulse width. As soon as Vcc rises above the reset threshold, WDO goes high with no delay. |

| RESET           | О        | The inverse of RESET, active high. Whenever RESET is high, RESET is low.                                                                                                                                                                                                                                                                                                                           |

### **Functional Description**

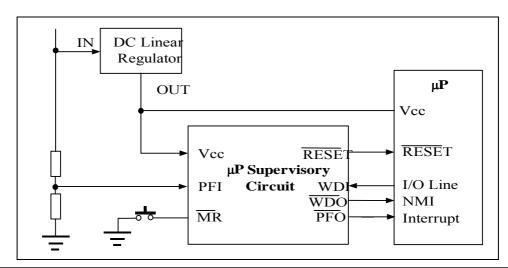

The PT75xx family can assert reset output during power-up, power-down and brownout conditions for  $\mu P$  system, detect power failure or low-battery conditions with a 1.25V threshold detector and have watchdog functions. Refer to Function Table of PT7A75xx Family for their individual features. The typical application see Figure 4.

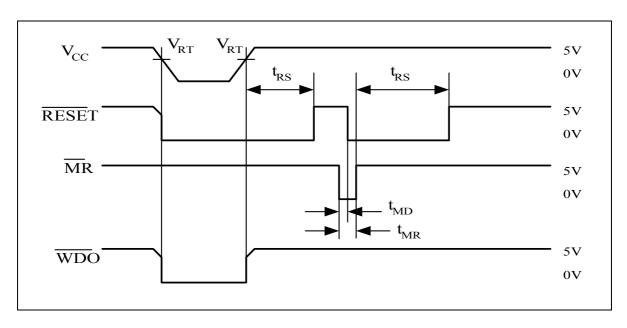

#### **Reset Output**

The supervisory circuits can assert reset for a microprocessor during power-up, power-down and brownout to prevent code execution errors.

On power-up, once Vcc reaches about 1.2V, RESET is a guaranteed logic low of 0.4V or less. As Vcc rises, RESET stays low. When Vcc rises above the reset threshold, an internal timer releases RESET after about 200ms. RESET pulses low whenever Vcc drops below the reset threshold, i.e. brownout condition. If brownout occurs in the middle of a previously initiated reset pulse, the pulse continues for at least another 140ms. On power-down, once Vcc falls below the reset threshold, RESET stays low and is guaranteed to be 0.4V or less until Vcc drops below 1.0V.

The PT7A752x and PT7A753x active-high RESET output is simply the inverse of the  $\overline{RESET}$  output, and is guaranteed to be valid with Vcc down to 1.2V. Some  $\mu$ Ps, such as Intel's 80C51, require an active-high reset pulse.

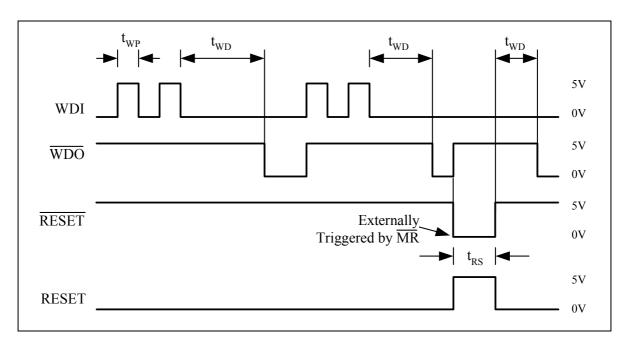

#### **Watchdog Timer**

The watchdog circuit monitors the  $\mu P$  activity. If the  $\mu P$  does not toggle the watchdog input (WDI) within 1.6sec and WDI is not in high impedance,  $\overline{WDO}$  goes low. As long as  $\overline{RESET}$  is asserted or the WDI input is in high impedance, the watchdog timer will stay cleared and will not count. As soon as reset is released and WDI is driven high or low, the timer will start counting. Pulses as short as 50ns can be detected.

Typically,  $\overline{WDO}$  will be connected to the non-maskable interrupt input (NMI) of a  $\mu P$ . When  $V_{CC}$  drops below the reset threshold,  $\overline{WDO}$  will go low whether or not the watchdog timer has timed out yet. Normally this would trigger an NMI interrupt, but  $\overline{RESET}$  goes low simultaneously, and thus overrides the NMI interrupt. If WDI is left unconnected,  $\overline{WDO}$  can be used as a low-line output. Since floating WDI disables the internal timer,  $\overline{WDO}$  goes low only when  $V_{CC}$  falls below the reset threshold, thus functioning as a low-line output.

#### **Manual Reset**

The manual-reset input  $(\overline{MR})$  allows reset to be triggered by a push button switch. The switch is effectively debounced by the 140ms minimum reset pulse width.  $\overline{MR}$  is  $\overline{TTL/CMOS}$  logic compatible, so it can be driven by any logic reset output.

#### **Power-Fail Comparator**

The power-fail comparator will send out a Low signal once detects a voltage lowered than 1.25V. It can be used for various purposes because its output and non-inverting input are not internally connected. The inverting input is internally connected to a 1.25V reference..

#### **Typical Application Circuit**

### **Maximum Ratings**

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

**Recommended Operation Conditions**

| Sym              | Description                  | Test Conditions          | Min         | Тур | Max         | Unit |

|------------------|------------------------------|--------------------------|-------------|-----|-------------|------|

|                  | Supply Voltage for 75x1,75x2 | -                        | 4.5         | 5.0 | 5.5         | V    |

| $V_{CC}$         | Supply Voltage for 75x3,75x4 | -                        | 3.0         | 3.3 | 5.5         | V    |

|                  | Supply Voltage for 75x5      |                          | 2.7         | 3.0 | 5.5         |      |

| $V_{\rm IH1}$    | MR Input High Voltage        | $V_{CC} > 4.0V$          | 2.0         | 2.4 | -           | V    |

| V IH1            |                              | $V_{CC} \le 4.0V$        | $0.7V_{CC}$ | -   | -           | V    |

| $V_{IH2}$        | WDI Input High Voltage       | -                        | $0.7V_{CC}$ | -   | -           | V    |

| V <sub>IL1</sub> | MR Input Low Voltage         | $V_{\rm CC} > 4.0 \rm V$ | -           | -   | 0.8         | V    |

|                  |                              | $V_{CC} \le 4.0V$        | -           | -   | $0.2V_{CC}$ | V    |

| $V_{IL2}$        | WDI Input Low Voltage        | -                        | -           | -   | $0.3V_{CC}$ | V    |

| T <sub>A</sub>   | Operating Temperature        | -                        | -40         | -   | 85          |      |

## **DC Electrical Characteristics**

$(V_{CC} = V_{RN} + 5\% \text{ to } 5.5\text{V}, T_A = -40 \sim 85^{\circ}\text{C}, \text{ unless otherwise noted.})$ (Note 1)

| Symbol            | Description                      | <b>Test Conditions</b>                                                                                  | Min                    | Typ      | Max                   | Unit |  |

|-------------------|----------------------------------|---------------------------------------------------------------------------------------------------------|------------------------|----------|-----------------------|------|--|

| $I_{CC}$          | Supply Current                   | 75x1/x2 Vcc = 5V,<br>75x3/x4 Vcc = 3.3V,<br>75x5 Vcc = 3.0V, Left WDI un-<br>connected (No output load) | -                      | 30       | 200                   | μΑ   |  |

| $V_{\mathrm{IH}}$ | Input High Voltage               | Pin: MR, WDI                                                                                            | 0.7V <sub>CC</sub>     | -        | -                     | V    |  |

| $V_{\mathrm{IL}}$ | Input Low Voltage                | Pin: MR, WDI                                                                                            | -                      | -        | $0.3V_{CC}$           | V    |  |

|                   |                                  | T <sub>A</sub> = 25°C                                                                                   | V <sub>RN</sub> - 1.5% | $V_{RN}$ | V <sub>RN</sub> +1.5% |      |  |

|                   |                                  | 75x1                                                                                                    | 4.560                  | 4.630    | 4.699                 |      |  |

|                   | D (T) 1 11 V 1                   | 75x2                                                                                                    | 4.314                  | 4.380    | 4.446                 |      |  |

| $V_{\text{RST}}$  | Reset Threshold Voltage (Note 2) | 75x3                                                                                                    | 3.034                  | 3.080    | 3.126                 | V    |  |

|                   |                                  | 75x4                                                                                                    | 2.886                  | 2.930    | 2.974                 |      |  |

|                   |                                  | 75x5                                                                                                    | 2.590                  | 2.630    | 2.669                 |      |  |

| $V_{RTH+}$        | Reset Threshold Voltage (Note 2) | V <sub>CC</sub> Varies between V <sub>RN</sub> - 5%                                                     | -                      | 70       | -                     | mV   |  |

|                   | Output High Voltage              | Vcc ≥ 4.5V Isource=800μA                                                                                | Vcc-1.5                | -        | -                     |      |  |

| $V_{\mathrm{OH}}$ |                                  | Vcc ≥ 2.7V Isource=500μA                                                                                | 0.8×Vcc                | -        | -                     | V    |  |

|                   |                                  | Vcc ≥ 1.8V Isource=150μA                                                                                | 0.8×Vcc                | -        | -                     |      |  |

|                   | Output Low Voltage               | Vcc ≥ 4.5V Isink=3.2mA                                                                                  | -                      | -        | 0.4                   |      |  |

| $V_{\mathrm{OL}}$ |                                  | Vcc ≥ 2.7V Isink=1.2mA                                                                                  | -                      | -        | 0.3                   | V    |  |

|                   |                                  | Vcc ≥ 1.2V Isink=100μA                                                                                  | -                      | -        | 0.3                   |      |  |

| 17                | PFI Input Threshold              | V <sub>PFI</sub> varies from 1.0V to 1.5V                                                               | 1.23                   | 1.25     | 1.27                  | V    |  |

| $V_{PFT}$         |                                  | V <sub>PFI</sub> varies from 0V to 1.0V                                                                 | 1.20                   | 1.25     | 1.30                  |      |  |

| ī                 | DEL Innut Current                | PFI connected to Vcc                                                                                    | -                      | -        | 2.00                  | μА   |  |

| $I_{PFI}$         | PFI Input Current                | PFI connected to GND                                                                                    | -2.00                  | -        | -                     |      |  |

| ī                 | Average WDI Input                | WDI connected to V <sub>CC</sub>                                                                        | -                      | 30       | 100                   | μА   |  |

| $I_{WDI}$         | Current (Note 3)                 | WDI connected to GND                                                                                    | -100                   | -30      | -                     |      |  |

| $I_{MR}$          | MR input Current                 | $\overline{MR}$ =0, Vcc = 5V                                                                            | -600                   | -250     | -100                  | μA   |  |

Note: 1. Parameters of room temperature guaranteed by production test and parameters of full-temperature guaranteed by design. 2. Valid for both  $\overline{RESET}$  and RESET.  $V_{RST}$  is the Reset threshold voltage when  $V_{CC}$  from high to low level,  $V_{RN}$  is nominal

reset threshold voltage.

<sup>3.</sup> WDI is internally serviced within the watchdog period if WDI is left unconnected.

### **AC Electrical Characteristics**

| Symbol            | Description             | Test Conditions                                                      | Min | Тур | Max  | Unit |

|-------------------|-------------------------|----------------------------------------------------------------------|-----|-----|------|------|

| $t_{RS}$          | Reset Pulse Width       | $\overline{\text{MR}}$ from low to High, T <sub>A</sub> =25          | 160 | 200 | 280  | ms   |

| $t_{ m WD}$       | Watchdog Timeout Period | WDI, $\overline{MR}$ tied to Vcc, Vcc>V <sub>RN</sub> +5%, $T_A$ =25 | 1.2 | 1.6 | 2.25 | S    |

| $t_{MR}$          | MR Pulse Width          | -                                                                    | 200 | -   | -    | ns   |

| $t_{ m MD}$       | MR to RESET Delay       | Vcc=5V                                                               | ı   | -   | 250  | ns   |

| $t_{\mathrm{WP}}$ | WDI Pulse Width         | -                                                                    | 150 | -   | -    | ns   |

### **Watchdog Timing Diagram**

### **Watchdog Timing Diagram**

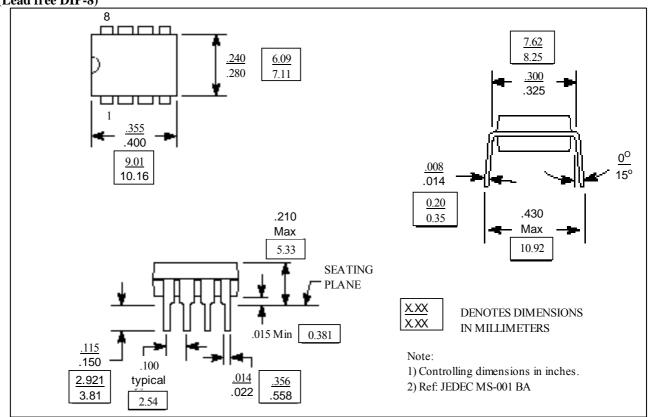

#### **Mechanical Information**

WE (Lead free and Green SOIC-8) .0099 0.25 x 45° .0196 .149 3.78 <u>0.1</u>9 .0075 0-8° .157 3.99 0.25 .0098 .016 <u>0.40</u> .050 1.27 .2284 .2440 .189 4.80 5.80 .196 5.00 6.20 X.XXDENOTES DIMENSIONS .016 .053 1.35 .026 IN MILLIMETERS 1.75 .068 0.406 0.660 **SEATING PLANE** Note: REF 1) Controlling dimensions in millimeters. 2) Ref: JEDEC MS-012 AA .050 .0040 0.10 BSC .0098 0.25 1.27 <u>.013</u> 0.330

#### PE (Lead free DIP-8)

.020

0.508

### **Notes**

# Pericom Technology Inc.

Email: support@pti.com.cn Web Site: www.pti.com.cn, www.pti-ic.com

China: No. 20 Building, 3/F, 481 Guiping Road, Shanghai, 200233, China

> Tel: (86)-21-6485 0576 Fax: (86)-21-6485 2181

Asia Pacific: Unit 1517, 15/F, Chevalier Commercial Centre, 8 Wang Hoi Rd, Kowloon Bay, Hongkong

Tel: (852)-2243 3660 Fax: (852)- 2243 3667

U.S.A.: 3545 North First Street, San Jose, California 95134, USA

Fax: (1)-408-435 1100 Tel: (1)-408-435 0800

Pericom Technology Incorporation reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. Pericom Technology does not assume any responsibility for use of any circuitry described other than the circuitry embodied in Pericom Technology product. The company makes no representations that circuitry described herein is free from patent infringement or other rights, of Pericom Technology Incorporation.