# **Hard Disk Pulse Detector**

## **GENERAL DESCRIPTION**

The XR-541 is a disk drive Pulse detector designed for use with RLL and MFM coding schemes. Signals from the read/write preamplifier are qualified by an amplitude verifying gating threshold before constant width pulses are output.

The XR-541 is available in 24 Pin Plastic DIP, JEDEC S.O., and 28 Pin PLCC packages. It employs +5V and +12V supplies.

#### **FEATURES**

RLL and MFM Decoding

High Performance AGC Preamplifier

Adjustable Detection Threshold

Wide Dynamic Range

Compatible with Embedded Servo

Separate Analog and Digital Grounds

TTL Level Output and Control

Replaces SS1541 Read Data Processor

# APPLICATIONS

Winchester Disk Drives Removable Cartridge Disk Drives

# **ABSOLUTE MAXIMUM RATINGS**

| 6.5V           |

|----------------|

| 14.0V          |

| -65°C to 150°C |

| 150°C          |

|                |

| 1W             |

| 8mW/°C         |

| 1W             |

| 8mW/°C         |

| 1W             |

| 8mW/°C         |

| -0.3V to 5.5V  |

| +/-3.3V        |

|                |

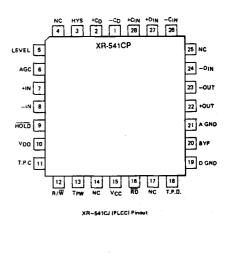

#### PIN ASSIGNMENT

#### **ORDERING INFORMATION**

| Part Number | Package         | <b>Operating Temperature</b> |

|-------------|-----------------|------------------------------|

| XR-541-1CP  | 24 Pin DIP/1ns  | 0°C to 70°C                  |

| XR-541-1CJ  | 28 Pin PLCC/1r  | ns 0°C to 70°C               |

| XR-541-1D   | 24 Pin S.O./1ns | 0°C to 70°C                  |

| XR-541-3CP  | 24 Pin DIP/3ns  | 0°C to 70°C                  |

| XR-541-3CJ  | 28 Pin PLCC/3r  | ns 0°C to 70°C               |

| XR-541-3D   | 24 Pin S.O./3ns | 0°C to 70°C                  |

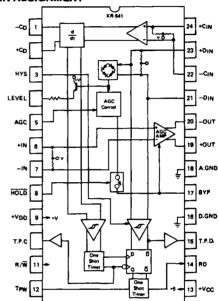

## SYSTEM DESCRIPTION

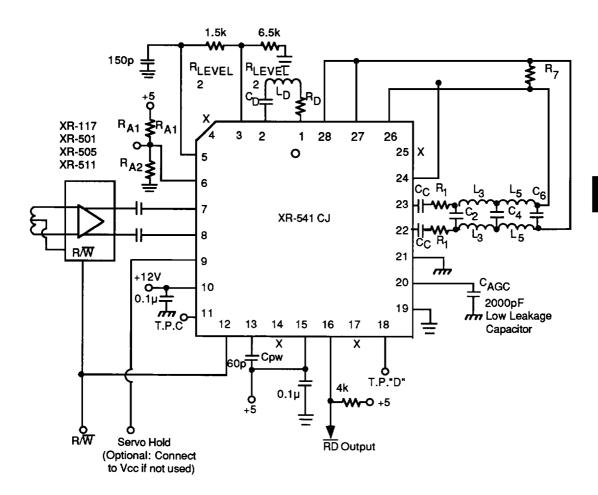

Signal from the disk head preamplifier are A.C. coupled into the XR-541. A low pass filter may be employed here to reduce system bandwidth and noise. The input amplifier is AGC controlled, allowing reliable operation with signal levels ranging from 20 mV to 660 mV p-p. A low pass filter removes unwanted components as the signal enters the differentiator and level detection threshold circuitry. Only when the signal rises above this user adjustable threshold is the output one-shot timer enabled.

Detection threshold is set by the voltage on the HYS Pin. Test points are provided for alignment of the delays from the clock input and the gating flip-flop. Dual grounds reduce coupling between the digital sections and the low level signal inputs.

# DC ELECTRICAL CHARACTERISTICS

**Test Conditions:**  $T_A = 25^\circ$ ,  $V_{CC} = 5V$ ,  $V_{DD} = 12V$ ,  $R/\overline{W} = High$  (>2.0V). Unless otherwise specified.

| SYMBOL             | PARAMETER                               | MIN  | TYP  | MAX      | UNIT       | CONDITIONS                                                                |

|--------------------|-----------------------------------------|------|------|----------|------------|---------------------------------------------------------------------------|

| lcc                | Supply Current                          |      | 4    | 14       | mA         | V <sub>CC</sub> = 5.5V                                                    |

| IDD                | Supply Current                          | İ    | 50   | 70       | mA         | $V_{DD} = 13.2V$                                                          |

| PD                 | Power Dissipation                       |      | 600  | 730      | mW         | VDD = 1922                                                                |

| DIGITAL SI         | GNALS                                   |      |      |          |            |                                                                           |

| V <sub>H</sub>     | Input "Low" Voltage                     |      | _    | 0.8      | ٧          |                                                                           |

| ViH                | Input "High" Voltage                    | 2.0  |      | "        | v          |                                                                           |

| l <sub>IL</sub>    | Input "Low" Current                     | -0.4 |      |          | m <b>A</b> | V <sub>II</sub> = 0.4V                                                    |

| l <sub>iH</sub>    | Input "High" Current                    | 1    |      | 100      | μА         | V <sub>IH</sub> =2.4V                                                     |

| VOL                | Output "Low" Voltage                    | i    |      | 0.4      | v          | I <sub>OL</sub> = 4mA RD Output                                           |

| V <sub>OH</sub>    | Output "High" Voltage                   | 2.4  |      |          | ٧          | I <sub>OH</sub> =-0.4mA RD Output                                         |

| AGC AMPL           | IFIER                                   |      |      |          |            | <u> </u>                                                                  |

| A <sub>V</sub> min | Minimum Gain                            |      | 0.1  | 4        | V/V        | Differential V <sub>OUT</sub> from 1.0V                                   |

| A <sub>Vmax</sub>  | Maximum Gain                            | 83   | 250  |          | V/V        | to 2.5Vp-p                                                                |

| R <sub>IN</sub>    | Differential Input Resistance           |      | 5    |          | ΚΩ         | , F                                                                       |

| C <sub>IN</sub>    | Differential Input Capacitance          |      |      | 10       | рF         |                                                                           |

| Z <sub>IN</sub>    | Common Mode Input Impedance             |      | 1.8  |          | ΚΩ         | R/W ≥ 2.4V BothSides                                                      |

|                    |                                         | į    | 250  | 500      | Ω          | R/W ≤ 0.8V Both Sides                                                     |

| e <sub>ni</sub>    | Input Noise Voltage                     | j    |      | 30       | nV/√Hz     | Az=maximum:15MHz bandwidth                                                |

| BW                 | Preamplifier Bandwidth                  | 30   | 60   |          | MHz        | Av = maximum: -3dB point                                                  |

| CMRR               | Common Mode Rejection Ratio             | 40   | 60   |          | dB .       | V <sub>IN</sub> = 100mVp-p at 5 MHz. Av =<br>Max.                         |

| PSRR               | Power Supply Rejection Ratio            | 30   | 40   |          | dB         | ΔV <sub>CC</sub> or ΔV <sub>DD</sub> = 100mV                              |

| Vout               | Outros Malana Outra                     | 1    | l _  |          |            | Vp-p at 5 MHz. Av = Max                                                   |

| Voul               | Output Voltage Swing                    | 3.0  | 6    | l i      | Vp-p       | R <sub>L</sub> ≥600Ω Differential.                                        |

| lout               | Output Courses Code                     |      |      |          |            | V <sub>AGC</sub> = 5.5V                                                   |

| R <sub>o</sub>     | Output Current Swing Output Resistance  | 13.2 | 14   | 32       | mA         |                                                                           |

| c <sub>o</sub>     | Output Capacitance                      |      |      | 32<br>15 | Ω<br>pF    |                                                                           |

| V <sub>DIN</sub>   | V(DIN+) - V(DIN-) Voltage Swing         | 370  | 480  | 560      | mVpp/      | \\                                                                        |

| VAGC               | -vs-Vage                                | 3,0  | 460  | 300      | V V        | V <sub>IN</sub> From 30mVp-p to 550mVp-p<br>V(DIN+) -V(DIN-) From 500Vp-p |

| - AGC              | TAGC                                    |      |      |          | •          | to 1.5Vp-p                                                                |

| ΔVDIN              | V(DIN+) - V(DIN-) Change                |      | 1    | 8        | %          | VAGC = constant. V <sub>CC</sub> 110%,                                    |

| VAGC               | , , , , , , , , , , , , , , , , , , , , |      | •    | -        |            | V <sub>DD</sub> ±10%. T <sub>A</sub> From 0°C to 70°C.                    |

| AGC                | AGC Fast Charge Current                 | 1.3  | 1.6  | 2.0      | mA         | V(DIN+) - V(DIN-) = 1.6V                                                  |

| AGC                | AGC Slow Charge Current                 | 140  | 180  | 220      | μA         | V(DIN+) - V(DIN-) = 1.6V. VAGC                                            |

|                    | Fast to Slow Attack                     |      | 1.25 |          |            | V <sub>DIN</sub> (initial)                                                |

|                    | Switching Point                         |      |      |          |            | V <sub>DIN</sub> (Final)                                                  |

|                    | AGC Capacitor Discharge                 |      |      |          |            | · Dist /- · · · · · · ·                                                   |

| ľ                  | Current                                 |      | 4.5  | ľ        | μΑ         | Operate (HOLD="High")V <sub>DIN</sub> =0                                  |

|                    |                                         | -200 | -    | 200      | nA .       | Hold (HOLD="Low")VDIN=0                                                   |

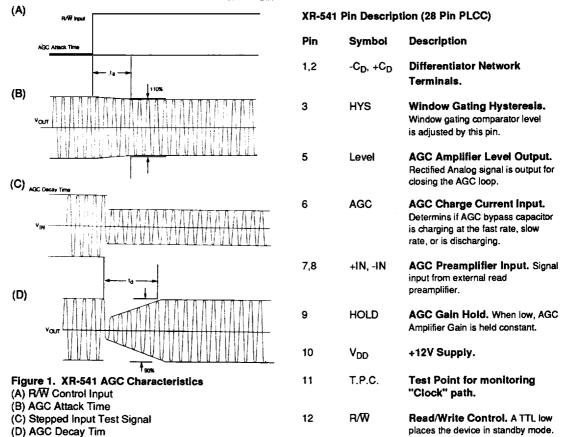

| t <sub>A</sub>     | AGC Attack Time                         |      | 4    |          | μs         | Note 1.                                                                   |

|                    | AGC Decay Tym                           | 1    | 50   | 1        |            |                                                                           |

| SYMBOL             | PARAMETER                                                                                                                                    | MIN                     | TYP                  | MAX                     | UNIT           | CONDITIONS                                                                |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------|-------------------------|----------------|---------------------------------------------------------------------------|

| WINDOW:            | THRESHOLD COMPARATOR                                                                                                                         |                         |                      |                         |                | <u> </u>                                                                  |

| R <sub>IN</sub>    | Differential Input Resistance                                                                                                                | 5                       |                      | 11                      | ΚΩ             | 1                                                                         |

| C <sub>IN</sub>    | Differential Input Caparitance                                                                                                               |                         |                      | 6                       | pF             |                                                                           |

| Z <sub>IN</sub>    | Common Mode Input Impedance                                                                                                                  |                         | 2                    |                         | ΚΩ             | $V_{HYS} = 0V$ . $R(DIN+ to DIN-) \le 1.5K\Omega$                         |

| Vos                | Threshold Comparator Offset Voltage                                                                                                          | -10                     |                      | 10                      | Mv             | 1                                                                         |

|                    | Peak Window Threshold Voltage<br>-vs-V <sub>HVS</sub>                                                                                        | 0.16                    | 0.22                 | 0.25                    | W <sub>V</sub> | V <sub>DIN</sub> Referred. V <sub>HYS</sub> From 1V to 3V.                |

| l <sub>HYS</sub>   | HYS Pin Input Current                                                                                                                        | -20                     |                      | 0                       | μΑ             | V <sub>HYS</sub> From 1V to 3V.                                           |

| V <sub>LEVEL</sub> | VLEVEL -VS- VDIN                                                                                                                             | 1.5                     | 2.0                  | 2.5                     | V/Vp-p         | V <sub>DIN</sub> From 0.6V to 1.3Vp-p 10KΩ<br>Load to Ground              |

| LEVEL              | LEVEL Maximum Output Current                                                                                                                 | 3.0                     |                      |                         | l mA           | Edat is cround                                                            |

| Ro(LEVEL)          | LEVEL Output Resistance                                                                                                                      |                         | 180                  |                         | Ω              | I <sub>LEVEL</sub> = 500mA                                                |

| VOLD               | Test Point D Output Low Voltage                                                                                                              | V <sub>DD</sub>         |                      | V <sub>DD</sub>         | v              | IOL ≤500mA                                                                |

|                    | ·                                                                                                                                            | -4                      | [ ]                  | -2.8                    | 1              | F = -,                                                                    |

| V <sub>ОНО</sub>   | Test Point D Output High Voltage                                                                                                             | V <sub>DD</sub><br>-2.5 |                      | V <sub>DD</sub><br>-1.8 | V              | il <sub>OH</sub> i≤ 500mA                                                 |

| DIFFEREN           | TIATOR                                                                                                                                       |                         |                      |                         | •              |                                                                           |

| R <sub>IN</sub>    | Differential Input Resistance                                                                                                                | 5.8                     |                      | 11                      | ΚΩ             | V <sub>CIN</sub>   = 100mVp-p at 2.5 MHz                                  |

| CIN                | Differential Input Capacitance                                                                                                               |                         |                      | 6                       | рF             | V <sub>CIN</sub>  = 100mVp-p at 2.5 MHz                                   |

| A <sub>VD</sub>    | Differentiator Preamp Gain                                                                                                                   | 1.7                     | 1.8                  | 22                      | V/V            | $V_{DIF}V_{CIN}$ : $R_{DIF} = 2k\Omega$                                   |

| Z <sub>IN</sub>    | Common Mode Input Impedance                                                                                                                  |                         | 2                    |                         | KΩ             |                                                                           |

| Vos                | Differentiator Offset Voltage                                                                                                                | -10                     |                      | 10                      | mV             | Capacitive Differentiator Network                                         |

| ь                  | Differentiator Drive Current                                                                                                                 | 11.3                    |                      |                         | mA             |                                                                           |

| Volc               | Test Point "C" Output Low Voltage                                                                                                            |                         | V <sub>DD</sub> -3.0 |                         | V              | I <sub>OL</sub> ≤500mA                                                    |

| Voc                | Test Point "C" Output                                                                                                                        |                         | 400                  |                         | mVp-p          | l <sub>OL</sub>  , l <sub>OH</sub>  ≤500mA                                |

| <u>د</u>           | Test Point "C" Pulse Width                                                                                                                   |                         | 30                   |                         | ns             | I <sub>OH</sub>  ≤500mA                                                   |

| CONTROL            | TIMING                                                                                                                                       |                         |                      |                         |                |                                                                           |

| TwR                | Write to Read Transition Time                                                                                                                | 1.2                     | 2                    | 3.0                     | μs             | Transition to High R <sub>IN</sub> .                                      |

| T <sub>R-W</sub>   | Read to Write Transition Time                                                                                                                |                         | 0.25                 | 1.0                     | μs             |                                                                           |

| TRH                | Read to Hold Transition Time                                                                                                                 |                         |                      | 1.0                     | jus<br>Pus     |                                                                           |

| DYNAMIC            | DATA CHARACTERISTICS                                                                                                                         |                         |                      |                         |                |                                                                           |

|                    | Additional Test Conditions:<br>V <sub>CIN</sub> ,V <sub>DIN</sub> =1.0Vp.p2.5MHz Sine Wave,\\ RD is loaded with 4KΩ to +V <sub>ce</sub> & 10 |                         |                      |                         |                | od Figuro 4                                                               |

|                    |                                                                                                                                              | TO CHAD.                | - IOIO IO FI         | 9ule 2, F               | iguie o at     | ru i igui e 4                                                             |

| T <sub>D1</sub>    | D Flip-Flop Set Up Time                                                                                                                      | 0                       |                      |                         | ns             | Delay from V <sub>DIN</sub> Passing threshold to V <sub>DIF</sub> Peaking |

| T <sub>D3</sub>    | Propagation Delay                                                                                                                            |                         | 65                   | 110                     | ns             | Delay from V <sub>DIN</sub> = V <sub>CIN</sub> Peaking                    |

| PP                 | Pulse Pairing                                                                                                                                |                         |                      |                         | ·              | to RD out.                                                                |

|                    | ruise raining                                                                                                                                |                         |                      | 1                       | ns<br>ns       | XR-541-1 (Note 3)<br>XR-541-3 (Note 3)                                    |

|                    |                                                                                                                                              |                         |                      | J                       | 113            | VU-041-9 (14016.9)                                                        |

| SYMBOL          | PARAMETER                            | MIN | TYP | MAX      | UNIT     | CONDITIONS                                                                                |

|-----------------|--------------------------------------|-----|-----|----------|----------|-------------------------------------------------------------------------------------------|

| T <sub>PW</sub> | Output Data Pulse Width<br>Accuracy  | -15 |     | 15       | %        | Error from T <sub>PW</sub> = 0.67 C <sub>PW</sub> :<br>C <sub>PW</sub> from 50pF to 200pF |

| T <sub>r</sub>  | Output Rise Time<br>Output Fall Time |     | 7   | 14<br>18 | ns<br>ns | To V <sub>OH</sub> = 2.4V<br>To V <sub>OI</sub> = 0.4V                                    |

NOTE 1: Time from Write to Read transition to V<sub>OUT</sub> reaching 110% of final value using 400mV<sub>p-p</sub> 2.5 MHz

sine wave.

(See Figure 1A, Figure 1B.)

NOTE 2: Time from Vin dropping from 300mV<sub>p-p</sub> to 150mV<sub>p-p</sub> to V<sub>OUT</sub> recovering within 90% of final value

using 2.5MHz sine wave.

Circuit is as shown in Figure 4. V<sub>CIN</sub> = V<sub>DIN</sub> = 1Vp-p 2.5 MHz sine wave.

| 13    | T <sub>PW</sub>                      | One Shot Timing Select. Output pulse time is set using a capacitor to +VCC. |

|-------|--------------------------------------|-----------------------------------------------------------------------------|

| 15    | $v_{cc}$                             | +5V Supply.                                                                 |

| 16    | RD                                   | Read Data Output. Active low digital output.                                |

| 18    | T.P.D.                               | Test Point for monitoring "Data" path.                                      |

| 19    | DGND                                 | Digital Ground.                                                             |

| 20    | BYP                                  | AGC Control Pin. A capacitor to ground sets AGC time constants.             |

| 21    | AGND                                 | Analog Ground.                                                              |

| 22,23 | +OUT,-OUT                            | AGC Amplifier Output.                                                       |

| 24,27 | - D <sub>IN</sub> , +D <sub>IN</sub> | "Data" path Input.                                                          |

| 26,28 | -C <sub>IN</sub> , +C <sub>IN</sub>  | "Clock" path Input.                                                         |

## **CIRCUIT OPERATION**

# Standby/Write Mode

During Data Write operations ( $R/\overline{W}$  low), the XR-541 AGC input impedance is lowered to reduce the time constant caused by the input coupling capacitors, which limits the speed of Write to Read recovery. The AGC is reset to maximum gain, and the digital circuitry is disabled.

#### Read Mode

### AGC

The analog head signal is A.C. coupled from the head preamplifier to the AGC inputs. The signal is amplified and output through low impedance drivers. Nominal peak output voltage is user-determinable by applying a voltage to the AGC Pin, according to the relationship:

Where V<sub>AGCOUT</sub> is the peak to peak pre-amplifier output voltage and V<sub>AGC</sub> is theDC control voltage on the AGC pin.

For most applications, a peak to peak output voltage of 2 volts is ideal.

AGC gain is held constant between pulses by the capacitor on the BYP Pin. Two rates of current charge this capacitor depending on the relative amplitude. A high level, 1.8mA, provides rapid attack characteristics needed for fast Write to Read recovery time. A low level, 180µA, allows slower gain tracking adjustment and reduces third order harmonic generation.

Preamplifier output is passed through a multiple order Bessel lowpass filter and applied to the Clock and Data inputs. For some applications, different delays are required for the Clock and Data inputs. For this reason, the XR-541 separates these inputs; many applications do not need separate timing and Clock Inputs and Data Inputs are directly connected. Internal path delays are carefully matched.

#### Hold

In the "Hold" mode, (Hold = low) no current charges  $C_{BYP}$  The constant voltage on  $C_{BYP}$  keeps the amplifier gain constant at the present valve. This feature is intended to facilitate embedded servo applications, where fixed gain is essential for amplitude comparison used in head positioning.

#### **Data Path**

Amplified signal output from the filter is applied to the  $+D_{IN}/-D_{IN}$  terminals to allow amplitude qualification of the signal and AGC loop closure. When this input amplitude exceeds the hysteresis threshold, the D flip-flop data inputs are toggled.

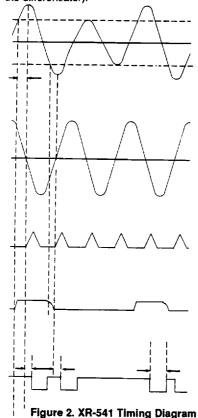

These inputs will not change state again until the signal changes direction and crosses the hysteresis threshold on the opposite side of 'zero'. See figures 2a, 2d. Hysteresis comparator output is buffered and appears at T.P.D. for testing or evaluation purposes.

#### **Clock Path**

Amplified signal output from the filter is applied to the  $+C_{IN}/-C_{IN}$  terminals to determine precise data peak timing. The clock path consists of a differentiator, a zero crossing comparator, and a one-shot timer.

The differentiator phase shifts the incoming waveform, converting data peaks into zero crossings. A capacitor, C<sub>D</sub>- typically 20pF to 150pF, determines the amount of

phase shift. Although a phase shift of 90° across all input frequencies would be ideal, this implies an infinte bandwidth. Noise considerations usually dictate adding a resistor, and occasionally an inductor, to limit the differentiator noise bandwidth. With a series RLC network, the differentiator transfer function becomes:

$$A_V = \frac{-2000 \text{ Cs}}{\text{LCs}^2 + (R + R_1) \text{ Cs} + 1}$$

where s = jw and  $R_1$  = 92 $\Omega$  (internal impedance of the differentiator).

- (A). AGC Amplifier Output (also  $V_{CIN} \ \& \ V_{DIN})$  showing ±window comparator thresholds.

- (B). Differentiator Circuit waveform (V<sub>CD</sub>).

- (C). Test Point "C" Output. Flip-flop clock input.

- (D). Test Point "D" Output. Flip-flop D input.

- (E). RD Output.

Differentiator output is applied to a zero crossing comparator. This comparator fires a bi-directionally triggered one-shot timer whose output is used as the clock of the D flip-flop. Buffered one-shot output appears at T.P.C. for alignment purposes.

# **Data Output**

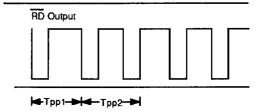

After the signal is time and amplitude qualified, the D flip-flop toggles. This fires a one shot timer which outputs constant width active low digital data pulse,  $\overline{\text{RD}}$ . The period of this pulse is programmed by a capacitor, Cpw, from pin Tpw to  $+V_{CC}$  and is proportioned to this capacitor by the formula:

$$Tpw = 0.67 Cpw$$

Where Tpw is in ns and Cpw is in pF.

Recommended Cpw values range from 50pF to 200 pf.

The active low RD output has a fan out of 1 TTL gate.

Figure 3. Pulse Pairing Definition

Figure 4. XR-541 Application Circuit