## 82378ZB SYSTEM I/O (SIO) AND 82379AB SYSTEM I/O APIC (SIO.A)

- Provides the Bridge Between the PCI Bus and ISA Bus

- 100% PCI and ISA Compatible

- PCI and ISA Master/Slave Interface - Directly Drives 10 PCI Loads and 6

- ISA Slots — PCI at 25 MHz and 33 MHz

- ISA from 6 MHz to 8.33 MHz

- Enhanced DMA Functions

- Scatter/Gather (S/G) (82378ZB)

Fast DMA Type A, B and F (82378ZB)

- Compatible DMA Transfere

- Compatible DMA Transfers

- 32-bit Addressability(82378ZB)

- 27-bit Addressability(82379AB)

- Seven Independently Programmable Channels

- Functionality of Two 82C37A DMA Controllers

- Data Buffers to Improve Performance

- 8-Byte DMA/ISA Master Line Buffer

32-bit Posted Memory Write Buffer to ISA

- Integrated 16-bit BIOS Timer

- Non-Maskable Interrupts (NMI)

- PCI System Errors

- ISA Parity Errors

- Arbitration for ISA Devices

- ISA Masters

- DMA and Refresh

- Four Dedicated PCI Interrupts

Level Sensitive

- Mapped to Any Unused Interrupt

- Arbitration for PCI Devices

Six PCI Masters Supported

Fixed, Rotating, or a Combination

- Utility Bus (X-Bus) Peripheral Support

- Provides Chip Select Decode

Controls Lower X-Bus Data Byte

- Transceiver

- Functionality of One 82C54 Timer

System Timer

- Refresh Request

- Speaker Tone Output

- Functionality of Two 82C59 Interrupt Controllers

- 14 Interrupts Supported

- Edge/Level Selectable Interrupts

- I/O APIC (Advanced Programmable Interrupt Controller (82379AB)

— Support for Multi-Processor Systems

- System Power Management (Intel SMM Support)

- Programmable System Management Interrupt (SMI)—Hardware Events, Software Events, EXTSMI#

- Programmable CPU Clock Control (STPCLK#)

Fast-On/Off Mode

- 208-Pin QFP Package

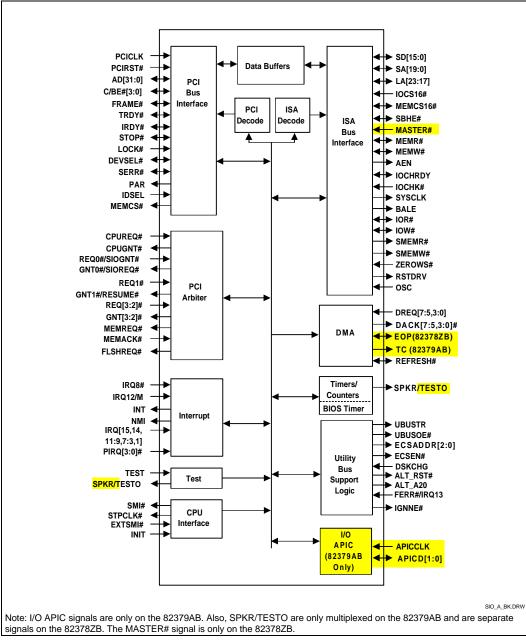

The 82378ZB System I/O (SIO) and 82379AB System I/O APIC (SIO.A) components are PCI-to-ISA Bus Bridge devices. These devices integrate many of the common I/O functions found in today's ISA-based PC systems—a seven channel DMA controller, two 82C59 interrupt controllers, an 8254 timer/counter, a BIOS timer, Intel SMM power management support, and logic for NMI generation. In addition, the SIO and SIO.A each support a total of six PCI Masters, and four PCI Interrupts. Decode is provided for peripheral devices such as the flash BIOS, real time clock, keyboard/mouse controller, floppy controller, two serial ports, one parallel port, and IDE hard disk drive.

For both the SIO and SIO.A, each DMA channel supports compatibility transfers. The SIO also supports types A, B, and F transfers and scatter/gather. In addition to the standard ISA-compatible interrupt controller that is in both the SIO and SIO.A, the SIO.A contains an Advance Programmable Interrupt Controller (IO APIC) for use in multi-processing systems.

This document describes both the 82378ZB (SIO) and 82379AB (SIO.A) components. Unshaded areas describe the 82378ZB. Shaded areas, like this one, describe differences between the 82379AB and 82378ZB.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata. Other brands and names are the property of their respective owners.

© INTEL CORPORATION 1996

March 1996

Order Number: 290571-001

82378ZB SIO and 82379AB SIO.A Component Block Diagram

## CONTENTS

PAGE

| 1.0. ARCHITECTURAL OVERVIEW                                    | 9    |

|----------------------------------------------------------------|------|

| 2.0. SIGNAL DESCRIPTION                                        | 12   |

| 2.1. PCI BUS INTERFACE SIGNALS                                 |      |

| 2.2. PCI ARBITER SIGNALS                                       | 14   |

| 2.3. ADDRESS DECODER SIGNAL                                    |      |

| 2.4. POWER MANAGEMENT SIGNALS                                  |      |

| 2.5. ISA INTERFACE SIGNALS                                     | 17   |

| 2.6. DMA SIGNALS                                               |      |

| 2.7. TIMER SIGNAL                                              |      |

| 2.8. INTERRUPT CONTROLLER SIGNALS                              |      |

| 2.9. APIC BUS SIGNALS (82379AB ONLY)                           |      |

| 2.10. UTILITY BUS SIGNALS                                      | 22   |

| 2.11. TEST SIGNALS                                             |      |

| 3.0. REGISTER DESCRIPTION                                      | 25   |

| 3.1. SIO CONFIGURATION REGISTER DESCRIPTION                    |      |

| 3.1.1. VID-VENDOR IDENTIFICATION REGISTER                      |      |

| 3.1.2. DID—DEVICE IDENTIFICATION REGISTER                      |      |

| 3.1.3. COM—COMMAND REGISTER                                    |      |

| 3.1.4. DS—DEVICE STATUS REGISTER                               |      |

| 3.1.5. RID-REVISION IDENTIFICATION REGISTER                    |      |

| 3.1.6. PCICON—PCI CONTROL REGISTER                             | 35   |

| 3.1.7. PAC—PCI ARBITER CONTROL REGISTER                        | 36   |

| 3.1.8. PAPC—PCI ARBITER PRIORITY CONTROL REGISTER              |      |

| 3.1.9. ARBPRIX—PCI ARBITER PRIORITY CONTROL EXTENSION REGISTER |      |

| 3.1.10. MCSCON-MEMCS# CONTROL REGISTER                         | 39   |

| 3.1.11. MCSBOH—MEMCS# BOTTOM OF HOLE REGISTER                  | -    |

| 3.1.12. MCSTOH—MEMCS# TOP OF HOLE REGISTER                     | 40   |

| 3.1.13. MCSTOM—MEMCS# TOP OF MEMORY REGISTER                   |      |

| 3.1.14. IADCON—ISA ADDRESS DECODER CONTROL REGISTER            |      |

| 3.1.15. IADRBE—ISA ADDRESS DECODER ROM BLOCK ENABLE REGISTER   |      |

| 3.1.16. IADBOH—ISA ADDRESS DECODER BOTTOM OF HOLE REGISTER     |      |

| 3.1.17. IADTOH—ISA ADDRESS DECODER TOP OF HOLE REGISTER        | 42   |

| 3.1.18. ICRT—ISA CONTROLLER RECOVERY TIMER REGISTER            | •••• |

| 3.1.19. ICD—ISA CLOCK DIVISOR REGISTER                         |      |

| 3.1.20. UBCSA—UTILITY BUS CHIP SELECT A REGISTER               |      |

| 3.1.21. UBCSB—UTILITY BUS CHIP SELECT B REGISTER               |      |

| 3.1.22. MAR1—MEMCS# ATTRIBUTE REGISTER #1                      | 47   |

|   | 3.1.23. MAR2-MEMCS# ATTRIBUTE REGISTER #2                                       | 47 |

|---|---------------------------------------------------------------------------------|----|

|   | 3.1.24. MAR3-MEMCS# ATTRIBUTE REGISTER #3                                       | 48 |

|   | 3.1.25. PIRQ[3:0]#—PIRQ ROUTE CONTROL REGISTERS                                 | 48 |

|   | 3.1.26. PACC—PIC/APIC CONFIGURATION CONTROL REGISTER (82379AB Only)             | 49 |

|   | 3.1.27. APICBASE—APIC BASE ADDRESS RELOCATION (82379AB Only)                    | 49 |

|   | 3.1.28. BIOS TIMER BASE ADDRESS REGISTER                                        | 50 |

|   | 3.1.29. SMICNTL—SMI CONTROL REGISTER                                            | 50 |

|   | 3.1.30. SMIEN—SMI ENABLE REGISTER                                               | 51 |

|   | 3.1.31. SEE—SYSTEM EVENT ENABLE REGISTER                                        | 51 |

|   | 3.1.32. FTMR—FAST OFF TIMER REGISTER                                            | 52 |

|   | 3.1.33. SMIREQ—SMI REQUEST REGISTER                                             | 53 |

|   | 3.1.34. CTLTMR—CLOCK SCALE STPCLK# LOW TIMER                                    | 54 |

|   | 3.1.35. CTLTMRH—CLOCK SCALE STPCLK# HIGH TIMER                                  | 54 |

| 3 | .2. DMA REGISTER DESCRIPTION                                                    | 55 |

|   | 3.2.1. DCOM—DMA COMMAND REGISTER                                                | 55 |

|   | 3.2.2. DCM—DMA CHANNEL MODE REGISTER                                            | 55 |

|   | 3.2.3. DCEM—DMA CHANNEL EXTENDED MODE REGISTER (82378ZB Only)                   | 56 |

|   | 3.2.4. DR-DMA REQUEST REGISTER                                                  | 59 |

|   | 3.2.5. MASK REGISTER-WRITE SINGLE MASK BIT                                      | 59 |

|   | 3.2.6. MASK REGISTER—WRITE ALL MASK BITS                                        | 60 |

|   | 3.2.7. DS-DMA STATUS REGISTER                                                   | 60 |

|   | 3.2.8. DMA BASE AND CURRENT ADDRESS REGISTERS (8237 COMPATIBLE SEGMENT)         | 61 |

|   | 3.2.9. DMA BASE AND CURRENT BYTE/WORD COUNT REGISTERS (8237 COMPATIBLE SEGMENT) | 61 |

|   | 3.2.10. DMA MEMORY BASE LOW PAGE AND CURRENT LOW PAGE REGISTERS                 |    |

|   | 3.2.10. DMA MEMORY BASE FIGH PAGE AND CORRENT FIGH PAGE REGISTERS               | -  |

|   | 3.2.12. DMA CLEAR BYTE POINTER REGISTER                                         | -  |

|   | 3.2.13. DMC—DMA MASTER CLEAR REGISTER                                           |    |

|   | 3.2.14. DCM—DMA MAGTER GEEAR REGISTER                                           |    |

|   | 3.2.15. SCATTER/GATHER (S/G) COMMAND REGISTER (82378ZB Only)                    |    |

|   | 3.2.16. SCATTER/GATHER (S/G) STATUS REGISTER (82378ZB Only)                     |    |

|   | 3.2.17. SCATTER/GATHER (S/G) DESCRIPTOR TABLE POINTER REGISTER (82378ZB Only)   |    |

|   | 3.2.18. SCATTER/GATHER (S/G) INTERRUPT STATUS REGISTER (82378ZB Only)           |    |

| 2 | .3. TIMER REGISTER DESCRIPTION                                                  |    |

| J | 3.3.1. TCW—TIMER CONTROL WORD REGISTER                                          |    |

|   | 3.3.2. INTERVAL TIMER STATUS BYTE FORMAT REGISTER                               |    |

|   | 3.3.3. COUNTER ACCESS PORTS REGISTER                                            |    |

|   | 3.3.4. BIOS TIMER REGISTER                                                      |    |

| 2 | .4. INTERRUPT CONTROLLER REGISTER DESCRIPTION                                   |    |

| J | 3.4.1. ICW1—INITIALIZATION COMMAND WORD 1 REGISTER                              |    |

|   | 3.4.2. ICW2—INITIALIZATION COMMAND WORD 2 REGISTER                              |    |

|   | 3.4.3. ICW3—INITIALIZATION COMMAND WORD 3 REGISTER                              |    |

|   |                                                                                 |    |

## 82378ZB (SIO) AND 82379 (SIO.A)

# intel®

| 3.4.4. ICW3—INITIALIZATION COMMAND WORD 3 REGISTER                   |    |

|----------------------------------------------------------------------|----|

| 3.4.5. ICW4—INITIALIZATION COMMAND WORD 4 REGISTER                   | 74 |

| 3.4.6. OCW1—OPERATIONAL CONTROL WORD 1 REGISTER                      | 74 |

| 3.4.7. OCW2—OPERATIONAL CONTROL WORD 2 REGISTER                      |    |

| 3.4.8. OCW3—OPERATIONAL CONTROL WORD 3 REGISTER                      |    |

| 3.5. CONTROL REGISTERS                                               |    |

| 3.5.1. NMISC—NMI STATUS AND CONTROL REGISTER                         |    |

| 3.5.2. NMI ENABLE AND REAL-TIME CLOCK ADDRESS REGISTER               | 78 |

| 3.5.3. PORT 92 REGISTER                                              |    |

| 3.5.4. DIGITAL OUTPUT REGISTER                                       | 79 |

| 3.5.5. RESET UBUS IRQ1/IRQ12 REGISTER                                | 79 |

| 3.5.6. COPROCESSOR ERROR REGISTER                                    | 80 |

| 3.5.7. ELCR—EDGE/LEVEL CONTROL REGISTER                              | 80 |

| 3.6. POWER MANAGEMENT REGISTERS                                      | 80 |

| 3.6.1. APMC—ADVANCED POWER MANAGEMENT CONTROL PORT                   | 81 |

| 3.6.2. APMS—ADVANCED POWER MANAGEMENT STATUS PORT                    | 81 |

| 3.7. APIC REGISTERS (82379AB ONLY)                                   | 81 |

| 3.7.1. IOREGSEL—I/O REGISTER SELECT REGISTER (82379AB Only)          | 82 |

| 3.7.2. IOWIN—I/O WINDOW REGISTER (82379AB Only)                      | 82 |

| 3.7.3. APICID—I/O APIC IDENTIFICATION REGISTER (82379AB Only)        | 82 |

| 3.7.4. APICID—I/O APIC VERSION REGISTER (82379AB Only)               |    |

| 3.7.5. APICARB-I/O APIC ARBITRATION REGISTER (82379AB Only)          |    |

| 3.7.6. IOREDTBL[15:0]—I/O REDIRECTION TABLE REGISTERS (82379AB Only) | 83 |

| 4.0. FUNCTIONAL DESCRIPTION                                          |    |

| 4.1. MEMORY AND I/O ADDRESS MAP                                      |    |

| 4.1.1. MEMORY ADDRESS MAP (GENERATING MEMCS#)                        |    |

| 4.1.2. BIOS MEMORY SPACE                                             |    |

| 4.1.3. I/O ACCESSES                                                  |    |

| 4.1.4. SUBTRACTIVELY DECODED CYCLES TO ISA                           | 88 |

| 4.1.5. UTILITY BUS ENCODED CHIP SELECTS                              | 88 |

| 4.2. PCI INTERFACE                                                   | 88 |

| 4.2.1. PCI COMMAND SET                                               | 88 |

| 4.2.2. TRANSACTION TERMINATION                                       | 89 |

| 4.3. PCI ARBITRATION CONTROLLER                                      |    |

| 4.3.1. ARBITRATION SIGNAL PROTOCOL                                   |    |

| 4.3.2. INTERNAL/EXTERNAL ARBITER CONFIGURATION                       | 91 |

| 4.3.3. Guaranteed Access Time Mode                                   |    |

| 4.3.3.1. DMA LATENCIES IN GAT MODE ONLY (82378ZB ONLY)               |    |

| 4.4. ISA INTERFACE                                                   |    |

| 4.4.1. ISA CLOCK GENERATION                                          | 93 |

| 4.5. DMA CONTROLLER                                                  |    |

| 4.5.1. DMA TIMINGS                                                                              | 94  |

|-------------------------------------------------------------------------------------------------|-----|

| 4.5.1.1. COMPATIBLE TIMING (82378ZB AND 82379AB)                                                | 95  |

| 4.5.1.2. TYPE "A" TIMING (82378ZB)                                                              | 95  |

| 4.5.1.3. TYPE "B" TIMING (82378ZB)                                                              | 95  |

| 4.5.1.4. TYPE "F" TIMING (82378ZB)                                                              | 95  |

| 4.5.1.5. DREQ AND DACK# LATENCY CONTROL (82378ZB AND 82379AB)                                   | 95  |

| 4.5.2. ISA REFRESH CYCLES (82378ZB and 82379AB)                                                 | 95  |

| 4.5.3. SCATTER/GATHER (S/G) DESCRIPTION (82378ZB)                                               | 95  |

| 4.6. DATA BUFFERING                                                                             | 98  |

| 4.6.1. DMA/ISA MASTER LINE BUFFER                                                               | 98  |

| 4.6.2. PCI MASTER POSTED WRITE BUFFER                                                           | 98  |

| 4.7. SIO TIMERS                                                                                 | 98  |

| 4.7.1. INTERVAL TIMERS                                                                          | 98  |

| 4.7.2. BIOS TIMER                                                                               | 99  |

| 4.8. INTERRUPT CONTROLLER                                                                       |     |

| 4.8.1. EDGE AND LEVEL TRIGGERED MODES                                                           |     |

| 4.8.2. NON-MASKABLE INTERRUPT (NMI)                                                             |     |

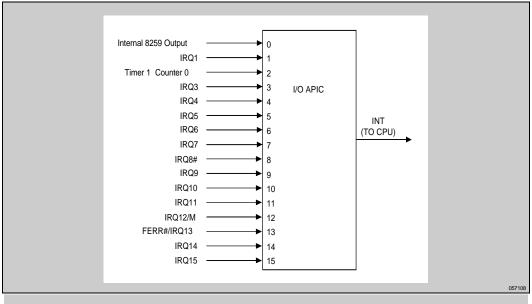

| 4.9. ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC) (82379AB ONLY)                           | 102 |

| 4.9.1. PHYSICAL CHARACTERISTICS OF APIC BUS (82379AB Only)                                      |     |

| 4.9.2. ARBITRATION FOR APIC BUS (82379AB Only)                                                  |     |

| 4.9.3. INTR AND THE PENTIUM $^{\circ}$ PROCESSOR'S "THROUGH LOCAL MODE" (82379AB Only)          |     |

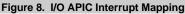

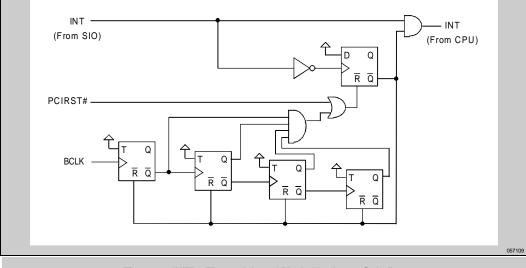

| 4.9.4. PULSING OF APICD1 DURING CPU RESET (82379AB Only)                                        |     |

| 4.9.5. SIO.A ASSERTING SIGNALS LOW DURING PCIRST# (82379AB ONLY)                                |     |

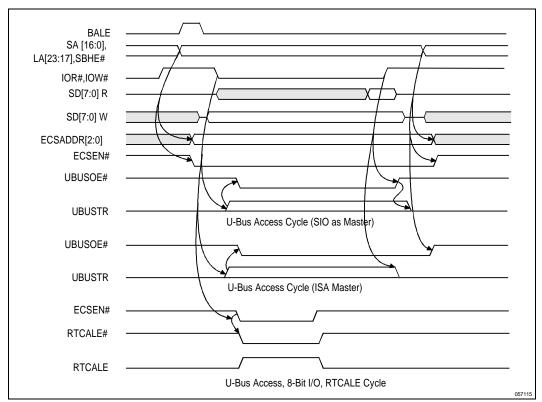

| 4.10. UTILITY BUS PERIPHERAL SUPPORT                                                            |     |

| 4.11. POWER MANAGEMENT                                                                          | -   |

| 4.11.1. SMM MODE                                                                                |     |

| 4.11.2. SMI SOURCES                                                                             |     |

| 4.11.3. SMI# AND INIT INTERACTION                                                               | -   |

| 4.11.4. CLOCK CONTROL                                                                           | -   |

| 4.11.5. DUAL-PROCESSOR POWER MANAGEMENT SUPPORT (82379AB Only)                                  |     |

| 4.11.5.1. SMI# DELIVERY MECHANISM                                                               | -   |

| 4.11.5.2. STPCLK# TIED TO BOTH SOCKETS                                                          |     |

| 4.11.5.3. SMI#/INTR (APIC MODE)                                                                 | 121 |

| 4.11.6. INTERRUPT LEVELS AND SYSTEM EVENT GENERATION IN POWER MANAGED<br>SYSTEMS (82378ZB Only) | 121 |

| 4.12. DESIGN CONSIDERATIONS (82378ZB/82379AB)                                                   | 121 |

| 4.12.1. Good Layout Practice                                                                    | 121 |

| 4.12.2. ASYNCHRONOUSLY SWITCHING SIGNALS                                                        | 121 |

| 5.0. ELECTRICAL CHARACTERISTICS                                                                 |     |

| 5.1. MAXIMUM RATINGS                                                                            | 122 |

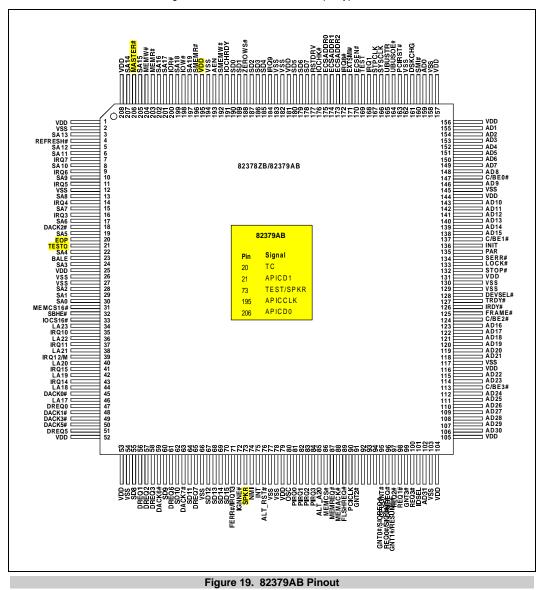

| 6.0. PIN ASSIGNMENT                                                                             | 123 |

## 82378ZB (SIO) AND 82379 (SIO.A)

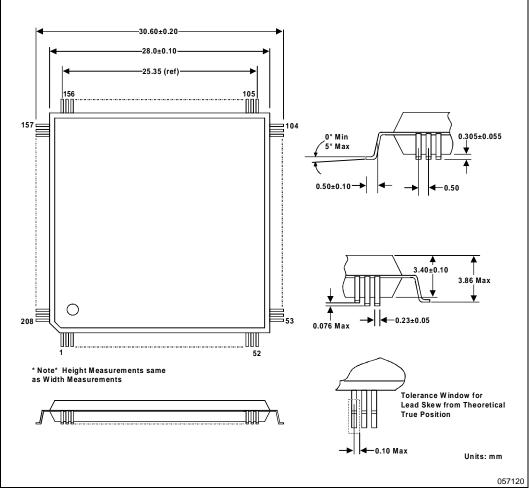

| 7.0. MECHANICAL SPECIFICATIONS |     |

|--------------------------------|-----|

| 7.1. PACKAGE DIAGRAM           | 127 |

| 7.2. THERMAL SPECIFICATIONS    |     |

| 8.0. TESTABILITY               |     |

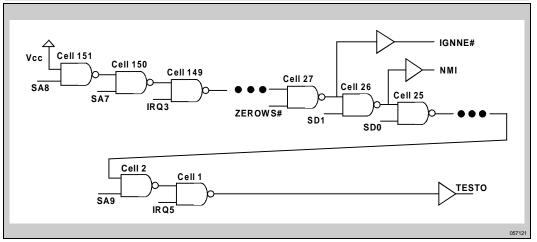

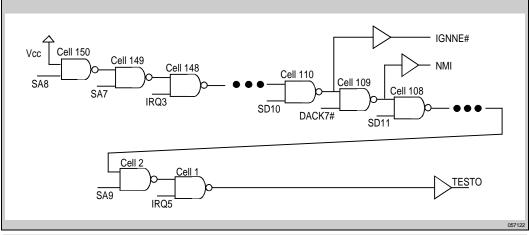

| 8.1. GLOBAL TRI-STATE          | 128 |

| 8.2. NAND TREE                 |     |

| 8.3. NAND TREE CELL ORDER      | 129 |

| 8.4. NAND TREE DIAGRAM         | 137 |

|                                |     |

## **1.0. ARCHITECTURAL OVERVIEW**

The major functions of the SIO and SIO.A components are broken up into blocks as shown in the SIO and SIO.A Component Block Diagrams. A description of each block is provided below.

#### **PCI Bus Interface**

The PCI Bus Interface provides the interface between the SIO/SIO.A and the PCI Bus. The SIO/SIO.A provides both a master and slave interface to the PCI Bus. As a PCI master, the SIO/SIO.A runs cycles on behalf of DMA, ISA masters, and the internal data buffer management logic when buffer flushing is required. The SIO/SIO.A burstS a maximum of two Dwords when reading from PCI memory, and one Dword when writing to PCI memory. The SIO/SIO.A does not generate PCI I/O cycles as a master. As a PCI slave, the SIO/SIO.A accepts cycles initiated by PCI masters targeted for the SIO/SIO.A internal register set or the ISA Bus. The SIO/SIO.A accepts a maximum of one data transaction before terminating the transaction. This supports the Incremental Latency Mechanism as defined in the Peripheral Component Interconnect (PCI) Specification.

As a master, the SIO/SIO.A generates address and command signal (C/BE#) parity for read and write cycles, and data parity for write cycles. As a slave, the SIO/SIO.A generates data parity for read cycles. Parity checking is not supported. The SIO/SIO.A also provides support for system error reporting by generating a Non-Maskable-Interrupt (NMI) when SERR# is driven active.

The SIO/SIO.A, as a resource, can be locked by any PCI master. In the context of locked cycles, the entire SIO/SIO.A subsystem (including the ISA Bus) is considered a single resource.

The SIO/SIO.A directly supports the PCI Interface running at either 25 MHz or 33 MHz. If a frequency of less than 33 MHz is required (not including 25 MHz), a SYSCLK divisor value (as indicated in the ISA Clock Divisor Register) must be selected that guarantees that the ISA Bus frequency does not violate the 6 MHz to 8.33 MHz SYSCLK range.

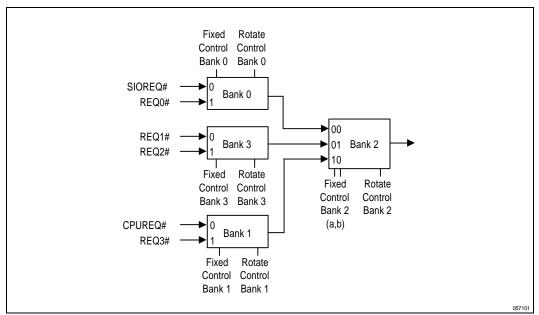

#### **PCI** Arbiter

The PCI arbiter provides support for six PCI masters; the Host Bridge, SIO/SIO.A, and four PCI masters. The arbiter can be programmed for a purely rotating scheme, fixed, or a combination of the two. The Arbiter can also be programmed to support bus parking. This gives the Host Bridge default access to the PCI Bus when no other device is requesting service. The arbiter can be disabled if an external arbiter is used.

#### Data Buffers

To isolate the slower ISA Bus from the PCI Bus, the SIO/SIO.A provides two types of data buffers. One Dworddeep posted write buffer is provided for the posting of PCI initiated memory write cycles to the ISA Bus. The second buffer is a bi-directional, 8-byte line buffer used for ISA master and DMA accesses to the PCI Bus. All DMA and ISA master read and write cycles go through the 8-byte line buffer. The data buffers also provide the data assembly or disassembly when needed for transactions between the PCI and ISA Buses. Buffering is programmable and can be enabled or disabled through software.

#### **ISA Bus Interface**

The SIO/SIO.A incorporates a fully ISA-Bus compatible master and slave interface. The SIO/SIO.A directly drives six ISA slots without external data or address buffering. The ISA interface also provides byte swap logic, I/O recovery support, wait-state generation, and SYSCLK generation. The SIO/SIO.A supports ISA Bus frequencies from 6 to 8.33 MHz.

#### 82378ZB (SIO) AND 82379AB (SIO.A)

As an ISA master, the SIO/SIO.A generates cycles on behalf of DMA, Refresh, and PCI master initiated cycles. The SIO/SIO.A supports compressed cycles when accessing ISA slaves (i.e., ZEROWS# asserted). As an ISA slave, the SIO/SIO.A accepts ISA master accesses targeted for the SIO/SIO.A internal register set or ISA master memory cycles targeted for the PCI Bus. The SIO/SIO.A does not support ISA master initiated I/O cycles targeted for the PCI Bus.

The SIO/SIO.A also monitors ISA master to ISA slave cycles to generate SMEMR# or SMEMW#, and to support data byte swapping, if necessary.

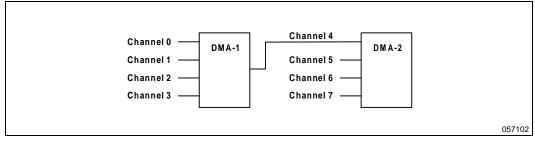

#### DMA

The DMA controller in the SIO/SIO.A incorporates the functionality of two 82C37 DMA controllers with seven independently programmable channels. Each channel can be programmed for 8- or 16-bit DMA device size. The DMA controller is also responsible for generating ISA refresh cycles.

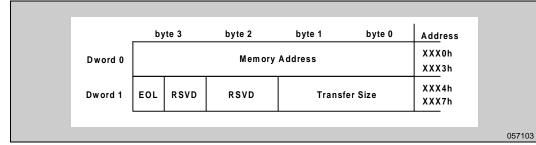

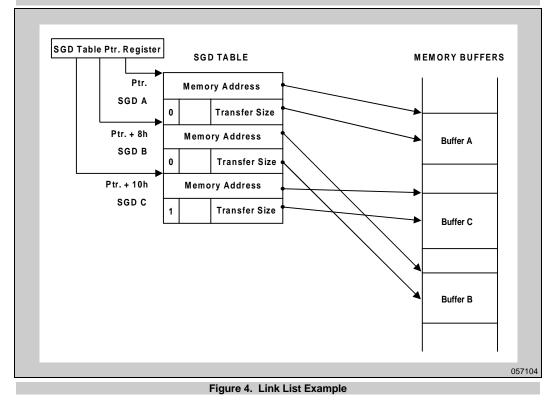

For the 82378ZB, ISA-compatible or fast DMA type "A", type "B", or type "F" timings are supported and 32-bit addressing is supported as an extension of the ISA-compatible specification. The SIO supports an enhanced feature called Scatter/Gather (S/G). This feature provides the capability of transferring multiple buffers between memory and I/O without CPU intervention. In S/G mode, the DMA can read the memory address and word count from an array of buffer descriptors, located in system memory, called the S/G Descriptor (SGD) Table. This allows the DMA controller to sustain DMA transfers until all of the buffers in the SGD table are read.

For the SIO.A, the DMA supports 8-/16-bit device size using ISA-compatible timings and 27-bit addressing as an extension of the ISA-compatible specification. Scatter/Gather is not supported.

#### Timer Block

The timer block contains three counters that are equivalent in function to those found in one 82C54 programmable interval timer. These three counters are combined to provide the System Timer function, Refresh Request, and speaker tone. The three counters use the 14.31818 MHz OSC input for a clock source.

In addition to the three counters, the SIO/SIO.A provides a programmable 16-bit BIOS timer. This timer can be used by BIOS software to implement timing loops. The timer uses the ISA system clock (SYSCLK) divided by 8 as a clock source. An 8:1 ratio between the SYSCLK and the BIOS timer clock is always maintained. The accuracy of the BIOS timer is  $\pm 1$  ms.

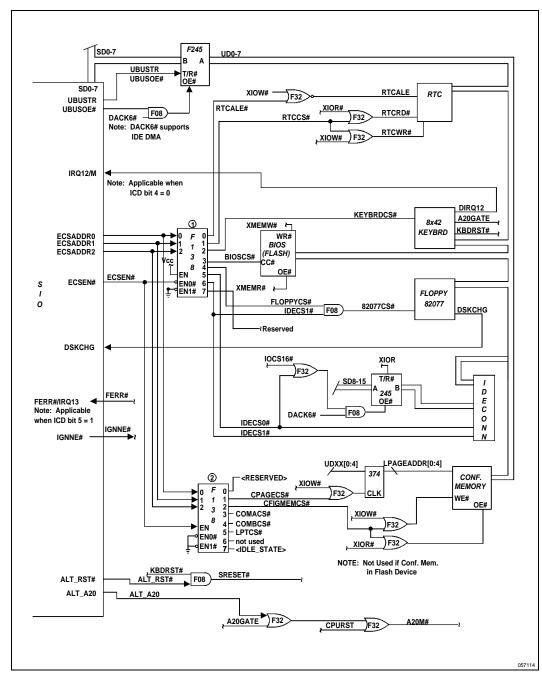

#### Utility Bus (X-Bus) Logic

The SIO/SIO.A provides four encoded chip selects that are decoded externally to provide chip selects for flash BIOS, real time clock, keyboard/Mouse Controller, floppy controller, two serial ports, one parallel port, and an IDE hard disk drive. The SIO/SIO.A provides the control for the buffer that isolates the lower 8 bits of the Utility Bus from the lower 8 bits of the ISA Bus. In addition to providing the encoded chip selects and Utility Bus buffer control, the SIO/SIO.A also provides Port 92 functions (Alternate Reset and Alternate A20), Coprocessor error reporting, the Floppy DSKCHG function, and a mouse interrupt input.

#### Interrupt Controller Block

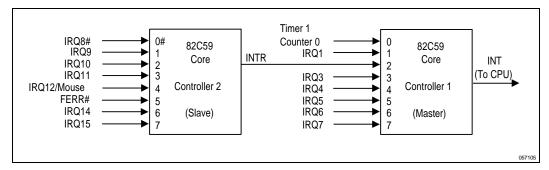

The SIO/SIO.A provides an ISA compatible interrupt controller that incorporates the functionality of two 82C59 interrupt controllers. The two interrupt controllers are cascaded so that 14 external and two internal interrupts are possible.

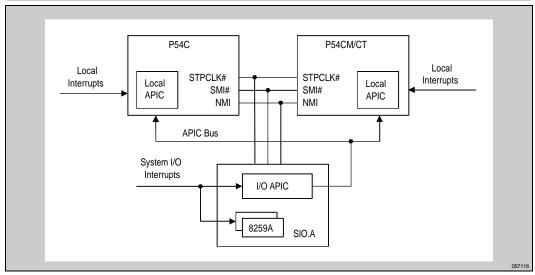

#### Advanced Programmable Interrupt Controller (APIC) (SIO.A Only)

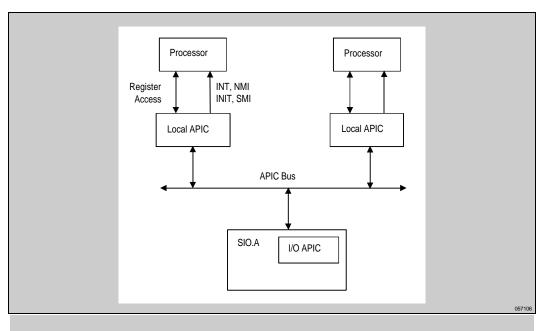

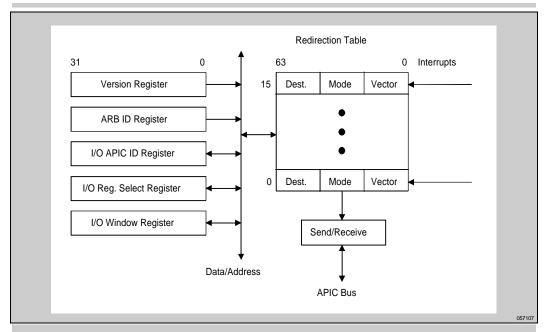

In addition to the standard ISA-compatible interrupt controller described above, the SIO.A incorporates the Advanced Programmable Interrupt Controller (APIC). While the standard interrupt controller is intended for use in a uni-processor system, APIC can be used in either a uni-processor or multi-processor system. APIC provides multi-processor interrupt management and incorporates both static and dynamic symmetric interrupt distribution across all processors. In systems with multiple I/O subsystems, each subsystem can have its own set of interrupts.

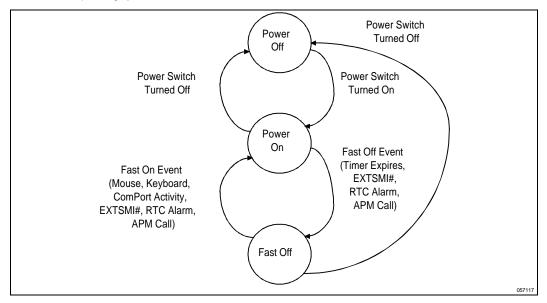

#### Power Management

Extensive power management capability permits a system to operate in a low power state without being powered down. Once in the low power state (called 'Fast-Off' state), the computer appears to be off. For example, the System Memory Management (SMM) code could turn off the CRT, line printer, hard disk drive's spindle motor, and fans. In addition, the CPU's clock can be governed. To the user, the machine appears to be in the off state. However, the system is actually in an extremely low power state that still permits the CPU to function and maintain communication connections normally associated with today's desktops (e.g., LAN, Modem, or FAX). Programmable options provide power management flexibility. For example, various system events can be programmed to place the system in the low power state or break events can be programmed to wake the system up.

#### Test

The test block provides the interface to the test circuitry within the SIO/SIO.A. The test input can be used to tristate all of the SIO/SIO.A outputs.

### 2.0. SIGNAL DESCRIPTION

This section contains a detailed description of each signal. The signals are arranged in functional groups according to the interface.

Note that the '#' symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When '#' is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of 'active-low' and 'active-high' signals. The term **assert**, or **assertion** indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term **negate**, or **negation** indicates that a signal is inactive.

The following notations are used to described the signal type.

| Signal Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| I           | Input is a standard input-only signal.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 0           | tem Pole Output is a standard active driver.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| OD          | pen Drain Input/Output.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| IO          | Input/Output is a bidirectional, tri-state pin.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| s/t/s       | <b>Sustained Tri-State</b> is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives a s/t/s pin low must drive it high for at least one clock before letting it float. A new agent can not start driving a s/t/s signal any sooner than one clock after the previous owner tri-states it. A pull-up sustains the inactive state until another agent drives it and is provided by the central resource. |  |  |  |

| t/s/o       | Tri-State Output                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

## 2.1. PCI Bus Interface Signals

| Signal Name Type Description |                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PCICLK                       | I              | <b>PCI CLOCK:</b> PCICLK provides timing for all transactions on the PCI Bus. All other PCI signals are sampled on the rising edge of PCICLK, and all timing parameters are defined with respect to this edge. Frequencies supported by the SIO/SIO.A include 25 and 33 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| PCIRST#                      | I              | PCI RESET: PCIRST# forces the SIO/SIO.A to a known state. AD[31:0],<br>C/BE[3:0]#, and PAR are always driven low by the SIO/SIO.A synchronously from<br>the leading edge of PCIRST#. The SIO/SIO.A always tri-states these signals from<br>the trailing edge of PCIRST#. If the internal arbiter is enabled (CPUREQ# sampled<br>high on the trailing edge of PCIRST#), the SIO/SIO.A will drive these signals low<br>again (synchronously 2-5 PCICLKs later) until the bus is given to another master. If<br>the internal arbiter is disabled (CPUREQ# sampled low on the trailing edge of<br>PCIRST#), these signals remain tri-stated until the SIO/SIO.A is required to drive<br>them valid as a master or slave. |  |  |

|                              |                | FRAME#, IRDY#, TRDY#, STOP#, DEVSEL#, MEMREQ#, FLSHREQ#,<br>CPUGNT#, GNT0#/SIOREQ#, and GNT1#/RESUME# are tri-stated from the<br>leading edge of PCIRST#. FRAME#, IRDY#, TRDY#, STOP#, and DEVSEL#<br>remain tri-stated until driven by the SIO/SIO.A as either a master or a slave.<br>MEMREQ#, FLSHREQ#, CPUGNT#, GNT0#/SIOREQ#, and GNT1#/RESUME#<br>are tri-stated until driven by the SIO/SIO.A. After PCIRST#, MEMREQ# and<br>FLSHREQ# are driven inactive asynchronously from PCIRST# inactive. CPUGNT#,<br>GNT0#/SIOREQ#, and GNT1#/RESUME# are driven based on the arbitration<br>scheme and the asserted REQx#'s.                                                                                          |  |  |

|                              |                | Il registers are set to their default values. PCIRST# may be asynchronous to CICLK when asserted or negated. Although asynchronous, negation must be a lean, bounce-free edge. Note that PCIRST# must be asserted for more than 1 $\mu$ s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| AD[31:0]                     | I/O            | <b>PCI ADDRESS/DATA.</b> The standard PCI address and data lines. The address is driven with FRAME# assertion and data is driven or received in following clocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| C/BE[3:0]#                   | I/O            | <b>BUS COMMAND AND BYTE ENABLES:</b> The command is driven with FRAME# assertion. Byte enables corresponding to supplied or requested data are driven on following clocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| FRAME#                       | I/O<br>(s/t/s) | <b>CYCLE FRAME:</b> Assertion indicates the address phase of a PCI transfer. Negation indicates that one more data transfer is desired by the cycle initiator. FRAME# is tristated from the leading edge of PCIRST#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| TRDY#                        | I/O<br>(s/t/s) | <b>TARGET READY:</b> Asserted when the target is ready for a data transfer. TRDY# is tri-stated from the leading edge of PCIRST#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| IRDY#                        | I/O<br>(s/t/s) | <b>INITIATOR READY:</b> Asserted when the initiator is ready for a data transfer. IRDY# is tri-stated from the leading edge of PCIRST#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| STOP#                        | I/O<br>(s/t/s) | <b>STOP:</b> Asserted by the target to request the master to stop the current transaction. STOP# is tri-stated from the leading edge of PCIRST#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| LOCK#                        | I              | <b>LOCK:</b> LOCK# indicates an atomic operation that may require multiple transactions to complete. LOCK# is always an input to the SIO/SIO.A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| IDSEL                        | I              | <b>INITIALIZATION DEVICE SELECT:</b> IDSEL is used as a chip select during configuration read and write transactions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Signal Name | Туре           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DEVSEL#     | I/O<br>(s/t/s) | <b>DEVICE SELECT:</b> The SIO/SIO.A asserts DEVSEL# to claim a PCI transaction through positive or subtractive decoding. DEVSEL# is tri-stated from the leading edge of PCIRST#. DEVSEL# remains tri-stated until driven by the SIO/SIO.A as either a master or a slave.                                                                                                                                                                                                |  |  |

| PIRQ[3:0]#  | 1              | PCI INTERRUPT REQUEST: PIRQ#s are used to generate asynchronous interrupts to the CPU via the Programmable Interrupt Controllers (82C59s) integrated in the SIO/SIO.A. These signals are defined as level sensitive and are asserted low. The PIRQx# interrupts can be steered into any unused IRQ interrupt. The PIRQx# Route Control Register determines which IRQ interrupt each PCI interrupt is steered into. These pins include a weak internal pull-up resistor. |  |  |

| PAR         | 0              | <b>CALCULATED PARITY SIGNAL:</b> A single parity bit is provided over AD[31:0] and C/BE[3:0]. PAR is always driven low by the 82379AB synchronously from the leading edge of PCIRST#.                                                                                                                                                                                                                                                                                   |  |  |

| SERR#       | I              | <b>SYSTEM ERROR:</b> SERR# can be pulsed active by any PCI device that detects a system error condition. Upon sampling SERR# active, the SIO/SIO.A generates a non-maskable interrupt (NMI) to the CPU.                                                                                                                                                                                                                                                                 |  |  |

## 2.2. PCI Arbiter Signals

| Signal Name       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CPUREQ#           | I    | CPU REQUEST: This signal provides the following functions:                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                   |      | 1. If CPUREQ# is sampled high on the trailing edge of PCIRST#, the internal arbiter is enabled. If CPUREQ# is sampled low on the trailing edge of PCIRST#, the internal arbiter is disabled. This requires that the host bridge drive CPUREQ# high during PCIRST#.                                                                                                                                                              |  |  |

|                   |      | 2. If the SIO/SIO.A internal arbiter is enabled, this pin is configured as CPUREQ#.<br>An active low assertion indicates that the CPU initiator desires the use of the PCI<br>Bus. If the internal arbiter is disabled, this pin is meaningless after reset.                                                                                                                                                                    |  |  |

|                   |      | his pin has a weak internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| REQ0#/<br>SIOGNT# | 1    | <b>REQUEST 0/SIO GRANT:</b> If the SIO/SIO.A internal arbiter is enabled, this pin is configured as REQ0#. An active low assertion indicates that Initiator0 desires the use of the PCI Bus. If the internal arbiter is disabled, this pin is configured as SIOGNT#. When asserted, SIOGNT# indicates that the external PCI arbiter has granted use of the bus to the SIO/SIO.A. This pin has a weak internal pull-up resistor. |  |  |

| REQ1#             | 1    | <b>REQUEST 1:</b> If the SIO/SIO.A internal arbiter is enabled through the Arbiter Configuration Register, then this signal is configured as REQ1#. An active low assertion indicates that Initiator1 desires the use of the PCI Bus. If the internal arbiter is disabled, the SIO/SIO.A ignores REQ1# after reset. This pin has a weak internal pull-up resistor.                                                              |  |  |

| Signal Name       | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CPUGNT#           | t/s/o | <b>CPU GRANT:</b> If the SIO/SIO.A internal arbiter is enabled, this pin is configured as CPUGNT#. The SIO/SIO.A internal arbiter asserts CPUGNT# to indicate that the CPU initiator has been granted the PCI Bus. If the internal arbiter is disabled, this signal is meaningless. CPUGNT# is tri-stated from the leading edge of PCIRST#. CPUGNT# is tri-stated until driven by the SIO/SIO.A. CPUGNT# is driven based on the arbitration scheme and the asserted REQx#s.                                                                                                                                   |  |

| GNT0#/<br>SIOREQ# | t/s/o | <b>GRANT 0/SIO REQUEST:</b> If the SIO/SIO.A internal arbiter is enabled, this pin is configured as GNT0#. The SIO/SIO.A internal arbiter asserts GNT0# to indicate that Initiator0 has been granted the PCI Bus. If the internal arbiter is disabled, this pin is configured as SIOREQ#. The SIO/SIO.A asserts SIOREQ# to request the PCI Bus. GNT0#/SIOREQ# is tri-stated from the leading edge of PCIRST#. GNT0#/SIOREQ# is tri-stated until driven by the SIO/SIO.A. GNT0#/SIOREQ# is driven based on the arbitration scheme and the asserted REQx#'s.                                                    |  |

| GNT1#/<br>RESUME# | t/s/o | <b>GRANT 1/RESUME:</b> If the SIO's internal arbiter is enabled, this pin is configured as GNT1#. The SIO/SIO.A internal arbiter asserts GNT1# to indicate that Initiator1 has been granted the PCI Bus. If the internal arbiter is disabled, this pin is configured as RESUME#. The SIO/SIO.A asserts RESUME# to indicate that the conditions causing the SIO/SIO.A to retry the cycle has passed. GNT1#/RESUME# is tristated from the leading edge of PCIRST#. GNT1#/RESUME# is tri-stated until driven by the SIO/SIO.A. GNT1#/RESUME# is driven based on the arbitration scheme and the asserted REQx#'s. |  |

| REQ2#             | I     | <b>REQUEST 2:</b> This pin is an active low signal that indicates that Initiator2 desires the use of the PCI Bus. This signal has a weak internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| REQ3#             | I     | <b>REQUEST 3:</b> This pin is an active low signal that indicates that Initiator3 desires the use of the PCI Bus. This signal has a weak internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| GNT2#             | t/s/o | <b>GRANT 2:</b> This pin is configured as GNT2#. The SIO/SIO.A internal arbiter asserts GNT2# to indicate that Initiator2 has been granted the PCI Bus. GNT2# is high upon reset.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| GNT3#             | t/s/o | <b>GRANT 3:</b> This pin is configured as GNT3#. The SIO/SIO.A internal arbiter asserts GNT3# to indicate that Initiator3 has been granted the PCI Bus. GNT3# is high upon reset.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Signal Name | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMREQ#     | t/s/o | (GAT) Mode, N<br>requesting the<br>requires owner<br>edge of PCIRS<br>After PCIRST,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IEMREQ# wil<br>ISA Bus (alor<br>ship of the ma<br>T#. MEMREC<br>MEMREQ# is | SIO/SIO.A is configured in Guaranteed Access Time<br>I be asserted when an ISA master or DMA is<br>ig with FLSHREQ#) to indicate that the SIO/SIO.A<br>ain memory. MEMREQ# is tri-stated from the leading<br>Q# remains tri-stated until driven by the SIO/SIO.A.<br>a driven inactive asynchronously from PCIRST#<br>erts FLSHREQ# concurrently with asserting |

|             |       | FLSHREQ#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MEMREQ#                                                                    | Meaning                                                                                                                                                                                                                                                                                                                                                         |

|             |       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                          | Idle                                                                                                                                                                                                                                                                                                                                                            |

|             |       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                          | Flush buffers pointing towards PCI to<br>avoid ISA deadlock                                                                                                                                                                                                                                                                                                     |

|             |       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                          | 82378ZB. Reserved                                                                                                                                                                                                                                                                                                                                               |

|             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            | 82379AB. GAT enabled or disabled: For buffer<br>coherency in APIC systems, the buffers<br>ting to main memory must be flushed<br>disabled for the duration of assertion.                                                                                                                                                                                        |

|             |       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                          | GAT mode. Guarantee PCI Bus immediate<br>access to main memory (this may or may<br>not require the PCI-to-main memory<br>buffers to be flushed first depending on<br>the number of buffers).                                                                                                                                                                    |

| FLSHREQ#    | t/s/o | <ul> <li>FLUSH REQUEST: FLSHREQ# is generated by the SIO/SIO.A to command all of the system's posted write buffers pointing towards the PCI Bus to be flushed. This is required before granting the ISA Bus to an ISA master or the DMA. FLSHREQ# is tri-stated from the leading edge of PCIRST#. FLSHREQ# remains tri-stated until driven by the SIO/SIO.A. After PCIRST, FLSHREQ# is driven inactive asynchronously from PCIRST# inactive.</li> <li>MEMORY ACKNOWLEDGE: MEMACK# is the response handshake that indicates to the SIO/SIO.A that the function requested over the MEMREQ# and/or FLSHREQ# signals has been completed. In GAT mode (MEMREQ# and FLSHREQ# asserted), the main memory bus is dedicated to the PCI Bus and the system's posted write buffers pointing towards the PCI Bus have been flushed and are disabled. In non-GAT mode (FLSHREQ# asserted alone), this means the system's posted write buffers have been flushed and are disabled. In either case, the SIO/SIO.A can now grant the ISA Bus to the requester.</li> </ul> |                                                                            |                                                                                                                                                                                                                                                                                                                                                                 |

| MEMACK#     | I     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |                                                                                                                                                                                                                                                                                                                                                                 |

## 2.3. Address Decoder Signal

| Signal Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMCS#      | 0    | <b>MEMORY CHIP SELECT.</b> MEMCS# is a programmable address decode signal provided to a Host CPU bridge. A CPU bridge can use MEMCS# to forward a PCI cycle to main memory behind the bridge. MEMCS# is driven one PCI clock after FRAME# is sampled active (address phase) and is valid for one clock cycle before going inactive. MEMCS# is high upon reset. |

## 2.4. Power Management Signals

| Signal Name | Туре | Description                                                                                                                                                                                                                                                              |

|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMI#        | 0    | <b>SYSTEM MANAGEMENT INTERRUPT:</b> SMI# is asserted by the 82379AB in response to one of many enableable hardware or software events. This signal is driven low during a hard reset (PCIRST# asserted) and driven high when PCIRST# is negated.                         |

| STPCLK#     | 0    | <b>STOP CLOCK:</b> STPCLK# is asserted by the 82379AB in response to one of many enableable hardware or software events. STPCLK# connects directly to the CPU. This signal is driven low during a hard reset (PCIRST# asserted) and driven high when PCIRST# is negated. |

| EXTSMI#     | 1    | <b>EXTERNAL SYSTEM MANAGEMENT INTERRUPT:</b> EXTSMI# is a falling edge triggered input to the 82379AB indicating that an external device is requesting the system to enter SMM mode. This pin includes a weak internal pull-up resistor.                                 |

| INIT        | I    | <b>INIT:</b> INIT is an input to the SIO/SIO.A indicating that the CPU is actually being soft reset. It is connected to the INIT pin of the CPU. This pin includes a weak internal pull-up resistor.                                                                     |

## 2.5. ISA Interface Signals

| Signal Name | Туре | Description                                                                                                                                                                                                                                                                                                                                      |  |

|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

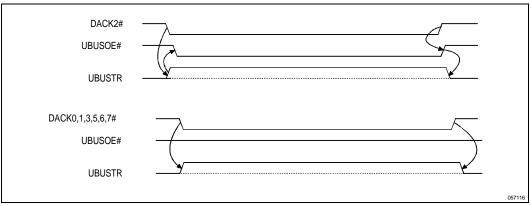

| AEN         | 0    | <b>ADDRESS ENABLE:</b> AEN is asserted during DMA cycles to prevent I/O slaves from misinterpreting DMA cycles as valid I/O cycles. This signal is also driven high during refresh cycles. AEN is driven low upon reset.                                                                                                                         |  |

| BALE        | 0    | <b>BUS ADDRESS LATCH ENABLE:</b> BALE is an active high signal asserted by the SIO/SIO.A to indicate that the address (SA[19:0], LA[23:17]), AEN and SBHE# signal lines are valid. The LA[23:17] address lines are latched on the trailing edge BALE. BALE remains asserted throughout DMA and ISA master cycles. BALE is driven low upon reset. |  |

| SYSCLK      | 0    | <b>SYSTEM CLOCK:</b> SYSCLK is an output of the SIO/SIO.A component. The frequencies supported are 6 to 8.33 MHz.                                                                                                                                                                                                                                |  |

| IOCHRDY     | I/O  | <b>I/O CHANNEL READY:</b> Resources on the ISA Bus assert IOCHRDY to indicate that additional time (wait states) is required to complete the cycle. IOCHRDY is tristated upon reset.                                                                                                                                                             |  |

| IOCS16#     | I    | <b>16-BIT I/O CHIP SELECT:</b> This signal is driven by I/O devices on the ISA Bus to indicate that they support 16-bit I/O bus cycles.                                                                                                                                                                                                          |  |

| IOCHK#      | I    | <b>I/O CHANNEL CHECK:</b> IOCHK# can be driven by any resource on the ISA Bus.<br>When asserted, it indicates that a parity or an un-correctable error has occurred for<br>a device or memory on the ISA Bus. A NMI will be generated to the CPU if the NMI<br>generation is enabled.                                                            |  |

| IOR#        | I/O  | <b>I/O READ:</b> IOR# is the command to an ISA I/O slave device that the slave may drive data on to the ISA data bus (SD[15:0]). IOR# is driven high upon reset.                                                                                                                                                                                 |  |

| IOW#        | I/O  | <b>I/O WRITE:</b> IOW# is the command to an ISA I/O slave device that the slave may latch data from the ISA data bus (SD[15:0]). IOW# is driven high upon reset.                                                                                                                                                                                 |  |

| Signal Name                  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |