### HIGH-SPEED CMOS OCTAL D FLIP-FLOP WITH CLOCK ENABLE

**IDT 54AHCT377**

#### **FEATURES:**

- Equivalent to ALS speeds and output drive over full temperature and voltage supply extremes

- · 10ns typical propagation delay

- Ioi = 14mA over full military temperature range

- CMOS power levels (5µW typ. static)

- . Both CMOS and TTL output compatible

- Substantially lower input current levels than ALS (5μA max.)

- Octal D flip-flop with clock enable

- JEDEC standard pinout for DIP and LCC

- · Military product compliant to MIL-STD-883, Class B

#### DESCRIPTION:

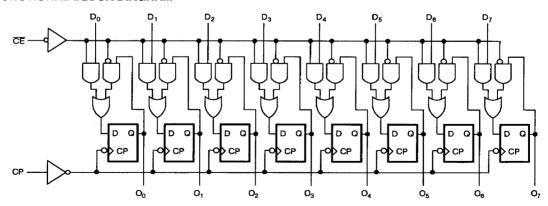

The IDT54AHCT377 is an octal D flip-flop built using advanced CEMOS ™, a dual metal CMOS technology. The IDT54AHCT377 has eight edge-triggered, D-type flip-flops with individual D inputs and O outputs. The common buffered Clock (CP) input loads all flip-flops simultaneously when the Clock Enable (CE) is LOW. The register is fully edge-triggered. The state of each D input, one setup time before the LOW-to-HIGH clock transition, is transferred to the corresponding flip-flop's O output. The CE input must be stable only one set-up time prior to the LOW-to-HIGH clock transition for predictable operation.

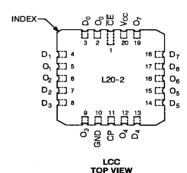

#### **PIN CONFIGURATIONS**

TOP VIEW

#### **FUNCTIONAL BLOCK DIAGRAM**

CEMOS is a trademark of Integrated Device Technology, Inc.

**MILITARY TEMPERATURE RANGE**

**JANUARY 1989**

© 1989 Integrated Device Technology, Inc.

DSC-4051/-1

## 10

#### ABSOLUTE MAXIMUM RATINGS (1)

| SYMBOL            | RATING                               | VALUE        | UNIT |

|-------------------|--------------------------------------|--------------|------|

| V <sub>TERM</sub> | Terminal Voltage with Respect to GND | -0.5 to +7.0 | ٧    |

| TA                | Operating Temperature                | -55 to +125  | °C   |

| TBIAS             | Temperature Under Bias               | -65 to +135  | °C   |

| T <sub>STG</sub>  | Storage Temperature                  | -65 to +150  | °C   |

| Pr                | P <sub>T</sub> Power Dissipation     |              | W    |

| lour              | DC Output Current 120                |              | mA   |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### CAPACITANCE ( $T_A = +25^{\circ}C$ , f = 1.0 MHz)

| SYMBOL | PARAMETER(1)       | CONDITIONS            | TYP. | MAX. | UNIT |

|--------|--------------------|-----------------------|------|------|------|

| CIN    | Input Capacitance  | $V_{IN} = 0V$         | 6    | 10   | рF   |

| Соит   | Output Capacitance | V <sub>OUT</sub> = 0V | 8    | 12   | рF   |

#### NOTE:

1. This parameter is measured at characterization but not tested.

#### DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

$T_A = -55$ °C to +125°C

$V_{CC} = 5.0V \pm 10\%$

$V_{LC} = 0.2V$

$V_{HC} = V_{CC} - 0.2V$

| SYMBOL          | PARAMETER             | TEST CONDITIONS (1)                                                        | MIN.            | TYP.(2)         | MAX. | UNIT |

|-----------------|-----------------------|----------------------------------------------------------------------------|-----------------|-----------------|------|------|

| V <sub>IH</sub> | Input HIGH Level      | Guaranteed Logic High Level                                                | 2.0             | _               | _    | v    |

| V <sub>IL</sub> | Input LOW Level       | Guaranteed Logic Low Level                                                 | _               | _               | 0.8  | ٧    |

| I <sub>iH</sub> | Input HIGH Current    | V <sub>CC</sub> = Max., V <sub>IN</sub> = V <sub>CC</sub>                  | _               | _               | 5.0  | μA   |

| l <sub>iL</sub> | Input LOW Current     | V <sub>∞</sub> = Max., V <sub>IN</sub> = GND                               | _               | _               | -5.0 | μА   |

| Isc             | Short Circuit Current | V <sub>CC</sub> = Max. <sup>(3)</sup>                                      | -60             | -100            | _    | mA   |

|                 |                       | $V_{CC} = 3V, V_{IN} = V_{LC} \text{ or } V_{HC}, I_{OH} = -32 \mu A$      | V <sub>HC</sub> | Vcc             | _    | mA   |

| V <sub>OH</sub> | Output HIGH Voltage   | $V_{CC} = Min.$ $I_{OH} = -150\mu A$                                       | V <sub>HC</sub> | V <sub>CC</sub> |      | >    |

|                 |                       | $V_{IN} = V_{IH} \text{ or } V_{IL}$ $I_{OH} = -1.0 \text{mA}$             | 2.4             | 4.3             | _    | ļ V  |

| V <sub>OL</sub> |                       | $V_{CC} = 3V$ , $V_{IN} = V_{LC}$ or $V_{HC}$ , $I_{OL} = 300 \mu\text{A}$ |                 | GND             | VLC  |      |

|                 | Output LOW Voltage    | $V_{CC} = Min.$ $I_{OL} = 300\mu A$                                        |                 | GND             | VLC  | V    |

|                 |                       | $V_{IN} = V_{IH} \text{ or } V_{IL}$ $I_{OL} = 14\text{mA}$                | -               | _               | 0.4  | 1    |

#### NOTES:

- 1. For conditions shown as max, or min., use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are at  $V_{CC} = 5.0V_{c} + 25^{\circ}C$  ambient and maximum loading.

- 3. Not more than one output should be shorted at one time. Duration of the short circuit test should not exceed one second.

#### POWER SUPPLY CHARACTERISTICS

$V_{IC} = 0.2V$ ;  $V_{HC} = V_{CC} - 0.2V$

| SYMBOL                         | PARAMETER                                                                   | TEST COND                                                                                | TIONS (1)                                                              | MIN. | TYP. <sup>(2)</sup> | MAX. | UNIT       |

|--------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|---------------------|------|------------|

| Icca                           | Quiescent Power Supply Current                                              | $V_{CC} = Max.$ $V_{IN} \ge V_{HC} : V_{IN} \le V_{LC}$ $f_{CP} = f_1 = 0$               |                                                                        | -    | 0.001               | 1.5  | mA         |

| Ісст                           | Quiescent Power Supply Current<br>TTL Inputs HIGH                           | $V_{CC} = Max.$ $V_{N} = 3.4V^{(3)}$                                                     |                                                                        | -    | 0.5                 | 2.0  | mA         |

| I <sub>CCD</sub>               | Dynamic Power Supply Current <sup>(5)</sup>                                 | V <sub>CC</sub> = Max. Outputs Open CE = GND One Bit Toggling 50% Duty Cycle             | V <sub>IN</sub> ≥ V <sub>HC</sub><br>V <sub>IN</sub> ≤ V <sub>LC</sub> | _    | 0.15                | 0.25 | mA/<br>MHz |

|                                | V <sub>CC</sub> = Max. Outputs Open f <sub>CP</sub> = 10MHz 50% Duty Cycle  | $V_{\text{IN}} \geq V_{\text{HC}}$ $V_{\text{IN}} \leq V_{\text{LC}}$ (AHCT)             | _                                                                      | 0.15 | 1.8                 |      |            |

| I <sub>cc</sub>                | (4)                                                                         | CE = GND One Bit Toggling at f <sub>1</sub> = 500kHz 50% Duty Cycle                      | V <sub>IN</sub> = 3.4V or<br>V <sub>IN</sub> = GND                     | _    | 0.65                | 3.8  | mA.        |

| Total Power Supply Current (4) | V <sub>CC</sub> = Max. Outputs Open f <sub>CP</sub> = 1.0MHz 50% Duty Cycle | $V_{\text{IN}} \geq V_{\text{HC}}^{(6)}$ $V_{\text{IN}} \leq V_{\text{LC}}^{(6)}$ (AHCT) | -                                                                      | 0.63 | 2.2                 |      |            |

|                                |                                                                             | CE = GND<br>Eight Bits Toggling<br>at f <sub>1</sub> = 250kHz<br>50% Duty Cycle          | V <sub>IN</sub> = 3.4V or <sup>(6)</sup><br>V <sub>IN</sub> = GND      | _    | 2.88                | 11.2 |            |

#### NOTES:

- 1. For conditions shown as max, or min., use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are at  $V_{\rm CC}=5.0V$ , +25°C ambient and maximum loading. 3. Per TTL driven input ( $V_{\rm IN}=3.4V$ ); all other inputs at  $V_{\rm CC}$  or GND.

- 4. Icc = I QUIESCENT + I INPUTS + I DYNAMC Icc = I CCC + I CCT DH NT + I CCD (ICP/2 + f<sub>1</sub>N<sub>1</sub>) Icc = Quiescent Current

- $I_{CCT}^{OO}$  = Power Supply Current for a TTL High Input (V<sub>IN</sub> = 3.4V)

- D<sub>H</sub> = Duty Cycle for TTL Inputs High

- N<sub>T</sub> = Number of TTL inputs at D<sub>H</sub>

- $I_{CCD}$  = Dynamic Current caused by an input Transition pair (HLH or LHL)

- f<sub>CP</sub> = Clock Frequency for Register Devices (Zero for Non-Register Devices)

- f<sub>i</sub> = Input Frequency

- N; = Number of inputs at f

- All currents are in milliamps and all frequencies are in megahertz.

- 5. This parameter is not directly testable, but is derived for use in Total Power Supply calculations.

- 6. Values for these conditions are examples of the I<sub>CC</sub> formula. These limits are guaranteed but not tested.

### 10

#### **DEFINITION OF FUNCTIONAL TERMS**

| PIN NAMES                      | DESCRIPTION               |

|--------------------------------|---------------------------|

| D <sub>0</sub> -D <sub>7</sub> | Data Inputs               |

| CE                             | Clock Enable (Active LOW) |

| 00-07                          | Data Outputs              |

| CP                             | Clock Pulse Input         |

#### **TRUTH TABLE**

| OPERATING MODE    | INPUTS |        |   | OUTPUTS                |  |

|-------------------|--------|--------|---|------------------------|--|

|                   | СР     | CE     | D | 0                      |  |

| Load "1"          | t      | 1      | h | н                      |  |

| Load "0"          | †      | ı      | ŀ | L                      |  |

| Hold (Do Nothing) | †<br>× | h<br>H | X | No Change<br>No Change |  |

H = HIGH Voltage Level

HIGH Voltage Level one setup time prior to the LOW-to-HIGH Clock Transition

L = LOW Voltage Level

LOW Voltage Level one setup time prior to the LOW-to-HIGH Clock Transition

X = Immaterial

† = LOW-to-HIGH Clock Transition

#### SWITCHING CHARACTERISTICS OVER OPERATING RANGE

| SYMBOL                               | PARAMETER                                          | CONDITION(1)          | TYP. | MIN. <sup>(2)</sup> | MAX. | UNIT |

|--------------------------------------|----------------------------------------------------|-----------------------|------|---------------------|------|------|

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CP to O <sub>N</sub>          |                       | 10.0 | 2.0                 | 20.0 | ns   |

| t <sub>s</sub>                       | Set-up Time<br>HIGH or LOW<br>D <sub>N</sub> to CP |                       | 5.0  | 2.0                 | _    | ns   |

| t <sub>H</sub>                       | Hold Time<br>HIGH or LOW<br>D <sub>N</sub> to CP   | C <sub>L</sub> = 50pF | 2.0  | 1.5                 | _    | ns   |

| t <sub>s</sub>                       | Set-up Time<br>HIGH or LOW<br>CE to CP             | R <sub>L</sub> = 500Ω | 3.0  | 4.0                 | _    | ns   |

| t <sub>H</sub>                       | Hold Time<br>HI <u>GH</u> or LOW<br>CE to CP       |                       | 2.0  | 1.5                 |      | ns   |

| tw                                   | Clock Pulse Width, LOW                             | 1 -                   | 7.0  | 7.0                 | _    | ns   |

#### NOTES:

- 1. See test circuit and waveform.

- 2. Minimum limits are guaranteed but not tested on Propagation Delays.

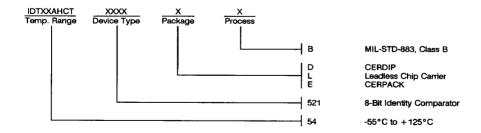

#### **ORDERING INFORMATION**

#### **CMOS TESTING CONSIDERATIONS**

Special test board considerations must be taken into account when applying high-speed CMOS products to the automatic test environment. Large output currents are being switched in very short periods and proper testing demands that test set-ups have minimized inductance and guaranteed zero voltage grounds. The techniques listed below will assist the user in obtaining accurate testing results:

- All input pins should be connected to a voltage potential during testing. If left floating, the device may oscillate; causing improper device operation and possible latchup.

- Placement and value of decoupling capacitors is critical. Each physical set-up has different electrical characteristics and it is recommended that various decoupling capacitor sizes be experimented with. Capacitors should be positioned using the

- minimum lead lengths. They should also be distributed to decouple power supply lines and be placed as close as possible to the DUT power pins.

- 3. Device grounding is extremely critical for proper device testing. The use of multi-layer performance boards with radial decoupling between power and ground planes is necessary. The ground plane must be sustained from the performance board to the DUT interface board and wiring unused interconnect pins to the ground plane is recommended. Heavy gauge stranded wire should be used for power wiring, with twisted pairs being recommended for minimized inductance.

- 4. To guarantee data sheet compliance, the input thresholds should be tested per input pin in a static environment. To allow for hardware-induced noise, it may be necessary to use V<sub>IL</sub> ≤ 0V and V<sub>IH</sub> ≥ 3V for ATE testing purposes.

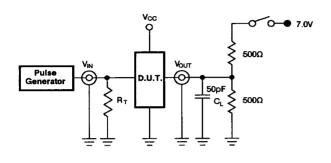

#### TEST CIRCUITS FOR THREE-STATE OUTPUTS

#### SWITCH POSITION

| TEST                                    | SWITCH |  |

|-----------------------------------------|--------|--|

| Open Drain<br>Disable Low<br>Enable Low | Closed |  |

| All Other Outputs                       | Open   |  |

#### DEFINITIONS

C<sub>L</sub> = Load capacitance: includes jig and probe capacitance

R<sub>T</sub> = Termination resistance: should be equal to Z<sub>OUT</sub> of the Pulse Generator

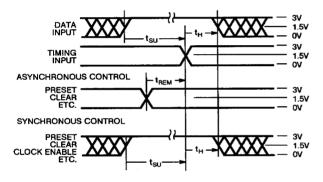

#### SET-UP, HOLD, AND RELEASE TIMES

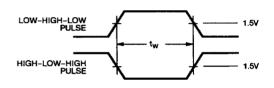

#### **PULSE WIDTH**

# 10

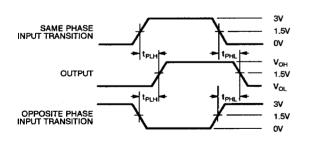

#### PROPAGATION DELAY

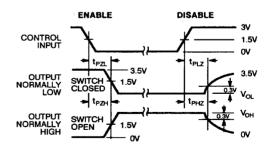

#### **ENABLE AND DISABLE TIMES**

#### NOTES:

- Diagram shown for input Control Enable-LOW and input Control Disable-HIGH

- 2. Pulse Generator for All Pulses: Rate  $\leq$  1.0 MHz; Z  $_{0} \leq$  50 $\Omega$ ;  $t_{F} \leq$  2.5ns;  $t_{R} \leq$  2.5ns