# High-Speed TTL Voltage Comparator

AD9686

FEATURES

7ns Propagation Delay

Complementary TTL Outputs

+5V, -6V Supply Voltages

APPLICATIONS

85dB CMRR

High-Speed Triggers

High-Speed Line Receivers

Peak Detectors

Threshold Detectors

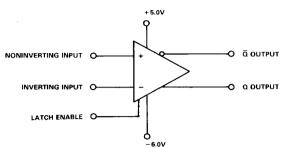

#### AD9686 FUNCTIONAL BLOCK DIAGRAM

#### GENERAL DESCRIPTION

The AD9686 is a high-speed voltage comparator with complementary TTL outputs. The AD9686 is manufactured in a high-performance bipolar process which provides an excellent match between high-speed ac switching and dc accuracy. The AD9686 operates with a propagation delay of only 7ns.

The AD9686 incorporates a Latch Enable control line providing operation in either a sample-hold mode or a track-hold mode. The Latch Enable setup times are less than 2ns which allows very high-speed voltage sampling.

The precision differential input stage has less than 2mV of offset voltage and requires an input bias current of only  $4\mu A$ . This combined with the 85dB common-mode rejection ratio, makes the AD9686 especially well suited for high-speed analog signal processing.

The AD9686 is offered as both an industrial temperature range device, -25°C to +85°C, and as an extended temperature range device, -55°C to +125°C. Both versions are available packaged in a TO-100 metal can and in a ceramic DIP. The extended temperature range device is also available in a ceramic LCC package.

#### ORDERING INFORMATION

| Device   | Temperature Range | Description                      | Package<br>Options* |

|----------|-------------------|----------------------------------|---------------------|

| AD9686BH | - 25°C to + 85°C  | 10-Pin Can, Industrial           | H-10A               |

| AD9686BQ | – 25°C to + 85°C  | 16-Pin DIP, Industrial           | Q-16                |

| AD9686TE | − 55°C to + 125°C | 20-Pin LCC, Extended Temperature | E-20A               |

| AD9686TH | −55°C to +125°C   | 10-Pin Can, Extended Temperature | H-10A               |

| AD9686TQ | -55°C to +125°C   | 16-Pin DIP, Extended Temperature | Q-16                |

<sup>\*</sup>See Section 16 for package outline information.

COMPARATORS 3-13

## **SPECIFICATIONS**

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup>          |                                            |

|------------------------------------------------|--------------------------------------------|

| Positive Supply Voltage (+V <sub>S</sub> ) +7V | Power Dissipation 600mW                    |

| Negative Supply Voltage $(-V_S)$               | Operating Temperature Range <sup>3</sup>   |

| Input Voltage Range <sup>2</sup>               | AD9686BH/BQ25°C to +85°C                   |

| Differential Input Voltage 6.0V                | AD9686TE/TH/TQ55°C to +125°C               |

| Latch Enable Voltage                           | Storage Temperature Range65°C to +150°C    |

| Output Current Sourcing 4mA                    | Junction Temperature + 175°C               |

| Sinking 14mA                                   | Lead Soldering Temperature (10sec) + 300°C |

|                                                |                                            |

## **ELECTRICAL CHARACTERISTICS** (Supply Voltages = -6.0V and +5.0V, unless otherwise stated)

| P                                         | Mil <sup>4</sup><br>Sub | _      | Al   | Industri<br>25°C to +<br>D9686BF | - 85°C<br>I/BQ | - 55<br>AD9 |     |      |          |

|-------------------------------------------|-------------------------|--------|------|----------------------------------|----------------|-------------|-----|------|----------|

| Parameter                                 | Group                   | Temp   | Min  | Тур                              | Max            | Min         | Тур | Max  | Units    |

| INPUT CHARACTERISTICS                     |                         | ļ      |      |                                  |                |             |     |      |          |

| Input Offset Voltage <sup>5</sup>         | 1                       | + 25°C |      | 1.0                              | 2.0            |             | 1.0 | 2.0  | mV       |

|                                           | 2,3                     | Full   |      |                                  | 3.0            | l           |     | 3.0  | mV       |

| Input Offset Drift                        | 1                       | Full   |      | 10                               |                | l           | 10  |      | μV/°C    |

| Input Bias Current                        | 1                       | + 25°C |      | 4                                | 10             | l           | 4   | 10   | μA       |

| • 000 0                                   | 2,3                     | Full   | İ    |                                  | 13             |             |     | 13   | μA       |

| Input Offset Current                      | 1                       | + 25°C |      | 0.4                              | 1.0            |             | 0.4 | 1.0  | μA       |

|                                           | 2,3                     | Full   | ļ    |                                  | 1.3            |             |     | 1.3  | μA       |

| Input Resistance                          | ]                       | + 25°C |      | 100                              |                |             | 100 |      | kΩ       |

| Input Capacitance                         |                         | + 25°C |      | 3                                |                |             | 3   |      | рF       |

| Input Voltage Range                       | 1,2,3                   | Full   | -3.3 |                                  | +4.5           | -3.3        |     | +4.5 | V        |

| Common-Mode Rejection Ratio               |                         | Full   |      | 85                               |                | ĺ           | 85  |      | dB       |

| ENABLE INPUT                              |                         |        |      |                                  |                |             |     |      |          |

| Logic "1" Voltage                         | 1,2,3                   | Full   | •    |                                  | 2.0            |             |     | 2.0  | Ιv       |

| Logic "0" Voltage                         | 1,2,3                   | Full   | 0.8  |                                  |                | 0.8         |     |      | v        |

| Logic "1" Current                         | 1,2,3                   | Full   | l    |                                  | 100            |             |     | 100  | μA       |

| Logic "0" Current                         | 1,2,3                   | Full   | ŀ    |                                  | 100            |             |     | 100  | μA       |

| DIGITAL OUTPUTS                           |                         |        |      |                                  |                |             |     |      |          |

| Logic "1" Voltage (Source 1mA)            | 1,2,3                   | Full   | 2.4  | 3.5                              |                | 2.4         | 3.5 |      | v        |

| Logic "0" Voltage (Sink 10mA)             | 1,2,3                   | Full   | 2.,  | 0.3                              | 0.4            | 2.7         | 0.3 | 0.4  | v        |

| SWITCHING PERFORMANCE                     | 1                       |        |      |                                  |                | <u> </u>    |     |      |          |

| Propagation Delays                        |                         |        |      |                                  |                |             |     |      |          |

| Input to Output HIGH                      |                         | +25℃   |      | 7                                |                |             | 7   |      |          |

| Input to Output LOW                       |                         | +25℃   |      | 7                                |                |             | 7   |      | ns       |

| Latch Enable to Output HIGH               |                         | +25°C  |      | 7                                |                |             | 7   |      | ns       |

| Latch Enable to Output LOW                | 1                       | + 25°C |      | 7                                |                |             | 7   |      | ns       |

| Delta Delay Between Outputs               |                         | +25°C  |      | 2                                |                |             | 2   |      | ns       |

| Latch Enable                              | i                       | . 23 0 |      | -                                |                |             | 2   |      | ns       |

| Minimum Pulse Width                       | 12                      | +25℃   |      | 2                                | 3              |             | 2   | 3    | 20       |

| Minimum Setup Time                        | 12                      | +25°C  |      | 1                                | 2              |             | 1   | 2    | ns       |

| Minimum Hold Time                         | 12                      | +25℃   |      | 1                                | 2              |             | 1   | 2    | ns<br>ns |

| POWER SUPPLY <sup>6</sup>                 |                         |        |      |                                  |                |             |     |      | 119      |

| Positive Supply Current (+5.0V)           | 1,2,3                   | Full   |      | 30                               | 35             |             | 20  |      |          |

| Negative Supply Current (+5.0V)           |                         | Fuli   |      |                                  |                |             | 30  | 35   | mA.      |

| Power Supply Rejection Ratio <sup>7</sup> | 1,2,3                   | Full   |      | 26<br>65                         | 32             |             | 26  | 32   | mA       |

| 1 ower supply Rejection Ratio             | L                       | ruii   |      | 03                               |                |             | 65  |      | dB       |

<sup>3</sup>Typical thermal impedance . . .

AD9686 Metal Can

$\theta_{JA} = 172^{\circ}\text{C/W}; \theta_{JC} = 52^{\circ}\text{C/W}$   $\theta_{JA} = 115^{\circ}\text{C/W}; \theta_{JC} = 57^{\circ}\text{C/W}$   $\theta_{JA} = 102^{\circ}\text{C/W}; \theta_{JC} = 45^{\circ}\text{C/W}$ AD9686 Ceramic AD9686 LCC

3-14 COMPARATORS

<sup>4</sup>Military subgroups apply to military qualified devices only.

$^{5}R_{S}=100\Omega$ .

Specifications subject to change without notice.

<sup>&</sup>lt;sup>1</sup>Absolute maximum ratings are limiting values, to be applied individually, and beyond which serviceability of the circuit may be impaired. Functional operation under any of these conditions is not necessarily implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>&</sup>lt;sup>2</sup>Under no circumstances should the input voltages exceed the supply voltages.

<sup>&</sup>lt;sup>6</sup>Supply voltage should remain stable within ±5% for normal operation. <sup>7</sup>Measured at  $\pm$  5% of  $+V_S$  and  $-V_S$ .

#### **EXPLANATION OF GROUP A MILITARY SUBGROUPS**

Subgroup 1-Static tests at +25°C.

Subgroup 4-Dynamic tests at +25°C.

Subgroup 2-Static tests at max rated oper. temp. Subgroup 3 - Static tests at min rated oper, temp.

Subgroup 5 - Dynamic tests at max rated oper. temp.

Subgroup 9-Switching tests at +25°C.

Subgroup 12 - Periodically sample tested.

Subgroup 6-Dynamic tests at min rated oper. temp. Subgroup 7-Functional tests at +25°C

Subgroup 10 - Switching tests at max rated oper. temp. Subgroup 11 - Switching tests at min rated oper. temp.

Subgroup 8-Functional tests at max and min rated

oper, temp.

#### FUNCTIONAL DESCRIPTION

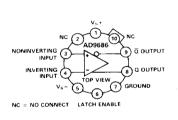

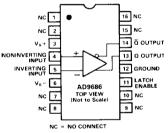

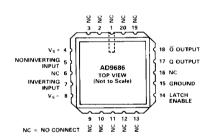

#### PIN NAME

#### DESCRIPTION

$+V_S$

NONINVERTING INPUT

Positive supply terminal, nominally +5.0V. Noninverting analog input of the differential input stage. The NONINVERTING INPUT must be driven in conjunction with the INVERTING INPUT.

INVERTING INPUT

Inverting analog input of the differential input stage. The INVERTING INPUT must be driven in conjunction with the NONINVERTING INPUT.

Negative supply terminal, nominally -6.0V.

LATCH ENABLE

In the "compare" mode (logic LOW), the output will track changes at the input of the comparator. In the "latch" mode (logic HIGH), the output will reflect the input state just prior to the comparator

GROUND QOUTPUT

being placed in the "latch" mode. Analog and digital ground. One of two complementary outputs. Q will be at logic HIGH if the analog voltage at the NON-

**OOUTPUT**

INVERTING INPUT is greater than the analog voltage at the INVERTING INPUT (provided the comparator is in the "compare" mode). See LATCH ENABLE for additional information.

NC

One of two complementary outputs.  $\overline{\mathbf{Q}}$  will be at logic LOW if the analog voltage at the NONIN-VERTING INPUT is greater than the analog voltage at the INVERTING INPUT (provided the comparator is in the "compare" mode). See LATCH ENABLE for additional information.

"NO CONNECT" pins are not internally connected.

#### PINOUT CONFIGURATIONS

TO-100 10-Pin Can

16-Pin DIP

20-Pin LCC

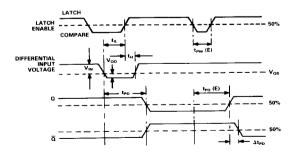

#### SYSTEM TIMING DIAGRAM

Minimum Setup Time  $t_S$ Minimum Hold Time tH

Input to Output Delay  $t_{PD}$

LATCH ENABLE to Output Delay  $t_{PD}(E)$  t<sub>PW</sub>(E) - Minimum LATCH ENABLE Pulse Width

Input Offset Voltage  $v_{os}$  $V_{OD}$ Overdrive Voltage

Delta Delay Between Complementary Outputs  $\Delta t_{PD}$

COMPARATORS 3-15

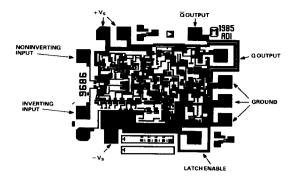

### DIE LAYOUT AND MECHANICAL INFORMATION

| Die Dimension  | ns |     |  |   |    |   |   |     |            |     |    |     |     | 59 | ) × | : 5 | 0 : | ×  | 18  | (r  | naz | K) 1 | mil  |

|----------------|----|-----|--|---|----|---|---|-----|------------|-----|----|-----|-----|----|-----|-----|-----|----|-----|-----|-----|------|------|

| Pad Dimensio   |    |     |  |   |    |   |   |     |            |     |    |     |     |    |     |     |     |    |     |     |     |      |      |

| Metalization . |    |     |  |   |    |   |   |     |            |     |    |     |     |    |     |     |     |    |     | A   | lur | nin  | un   |

| Backing        |    |     |  |   |    |   |   |     |            |     |    |     |     |    |     |     |     |    |     |     |     | N    | one  |

| Substrate Pote | nt | ial |  |   |    |   |   |     |            |     |    |     |     |    |     |     |     |    |     |     |     | _    | · V  |

| Passivation .  |    |     |  |   |    |   |   |     |            |     |    |     |     |    |     |     |     |    |     | 0   | ху  | ait  | ride |

| Die Attach .   |    |     |  |   |    |   |   |     |            |     |    |     |     |    |     |     |     |    | G   | old | É   | ute  | ctic |

| Bond Wire .    |    |     |  | 1 | .2 | 5 | m | ül, | . <i>P</i> | VI. | un | aiı | nu  | ım | ; 1 | Ul  | tra | as | or  | iic | Bo  | ond  | ling |

|                |    |     |  |   |    |   |   |     | o          | r l | ln | ıil | , ( | Go | ld  | ; ( | 9   | lc | l B | all | Bo  | ond  | ling |

3-16 COMPARATORS