# M-957 DTMF Receiver

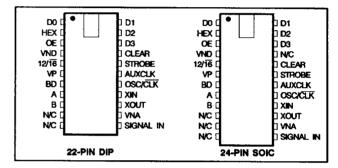

The Teltone M-957 (see Figure 1) combines switched-capacitor and digital frequency measuring techniques to decode Dual-Tone Multifrequency (DTMF) signals to four-bit binary data. Dial tone rejection and 60-Hz noise rejection filters are built in. Fabricated as a monolithic integrated circuit using low-power CMOS processing, the M-957 is packaged in a 22-pin DIP or 24-pin SOIC. M-957-01 operates from a wide 5-through-12-volt DC supply; M-957-02 from a 5-Volt supply. An inexpensive 3.58-MHz television crystal and resistor are the only external components required. High system density may be achieved by using the clock output of one crystal-connected receiver to drive the time bases of additional receivers.

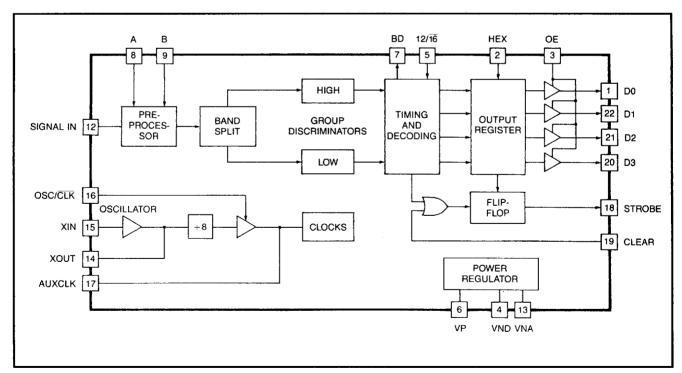

The SIGNAL IN input to the M-957 (see Figure 2) interfaces readily to telephone lines, radio receivers, tape players, and other DTMF signal sources. Inputs A and B control sensitivity to a maximum of -38 dBm at 5 V, while the 12/16 input determines the signals to be detected. The preprocessing stages of the M-957 filter out dial tone and noise, split the signal into its high- and low-frequency components, and hard-limit each component to provide automatic gain control. Four discriminators in each group then detect the individual tones. Postprocessing stages of the M-957 time the tone durations and store binary data for outputting as determined

by the HEX input. The STROBE output is activated by the presence of valid data in the output register and cleared by the detection of a valid end-of-signal pause or by the CLEAR input. An early signal presence indicator, BD, facilitates applications requiring tone blocking. The data outputs operate with simple logic circuits or microprocessors, and are three-state enabled to facilitate bus-oriented architectures.

### **Features**

- Complete DTMF receiver in 22-pin (plastic or CerDIP) or 24-pin SOIC package

- · Decodes all 16 DTMF digits

Figure 1 Pin Diagram

Figure 2 Block Diagram

- Meets telephone impulse noise immunity standards

- Digitally selectable sensitivity to -38 dBm

- Selectable 4-bit hexadecimal or binary coded 2 of 8 output

- Fabricated using low-power CMOS technology

- Operates on single DC supply

- Uses inexpensive 3.58-MHz crystal

- Three-state outputs

- 5- through 12-Volt supply (M-957-01)

- 5-Volt supply (M-957-02)

# **Applications**

- Central office products

- PBX and key systems

- · Radio telephones

- Remote control and monitoring devices

- Computer data entry systems

## **Table 1 Pin Functions**

| Pin                 | Function                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

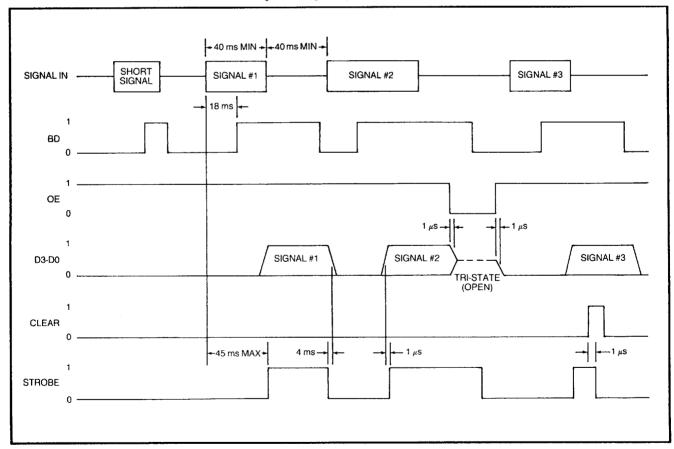

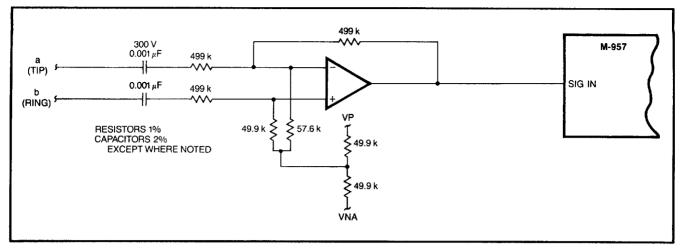

| SIGNAL IN           | DTMF input. Timings are shown in Figure 3. Internally biased so that the input signal may be AC coupled, SIGNAL IN also permits DC coupling as long as the input voltage does not exceed the positive supply. Proper coupling is shown in Figure 5. See Table 2 for the frequency pairs associated with each DTMF signal. |  |  |  |  |

| 12/16               | DTMF signal detection control. When 12/6 is at logic "1", the M-957 detects the 12 most commonly used DTMF signals (1 through #). When 12/6 is at logic "0", the M-957 detects all 16 DTMF signals (1 through D).                                                                                                         |  |  |  |  |

| A, B (Ref. Table 4) | Binary DTMF signal sensitivity control inputs. A and B select the sensitivity of the SIGNAL IN input to a maximum of -31 dBm.                                                                                                                                                                                             |  |  |  |  |

| D3, D2, D1, D0      | Data outputs. When enabled by the OE input, the data outputs provide the code corresponding to the detected digit in the format programmed by the HEX pin. See Table 2. The data outputs become valid after a tone pair has been detected and are cleared when a valid pause is timed. Timings are shown in Figure 3.     |  |  |  |  |

| OE                  | Output enable. When OE is at logic "1", the data outputs are in the CMOS push/pull state and represent the contents of the cregister (see Figure 2). When OE is driven to logic "0", the data outputs are forced to the high-impedance or "third" state. Timing shown in Figure 3.                                        |  |  |  |  |

| НЕХ                 | Binary output format control. When HEX is at logic "1", the output of the M-957 is full, 4-bit binary. When HEX is at logic "0", the output is binary coded 2-of-8. Table 2 shows the output codes.                                                                                                                       |  |  |  |  |

| STROBE              | Valid data indication. STROBE goes to logic "1" after a valid tone pair is sensed and decoded at the data outputs. STROBE remains at logic "1" until a valid pause occurs or the CLEAR input is driven to logic "1", whichever is earlier. Timings are shown in Figure 3.                                                 |  |  |  |  |

| CLEAR               | STROBE control. Driving CLEAR to logic "1" forces the STROBE output to logic "0". When CLEAR is at logic "0", STROBE is forced to logic "0" only when a valid pause is detected. Tie to VNA or VND when not used.                                                                                                         |  |  |  |  |

| BD                  | Early signal presence output. BD indicates that a possible signal has been detected and is being validated. As shown in Figure 3, BD precedes STROBE and the data outputs.                                                                                                                                                |  |  |  |  |

| XIN, XOUT           | Crystal connections. When an auxiliary clock is used, XIN should be tied to logic "1". See Figure 6.                                                                                                                                                                                                                      |  |  |  |  |

| OSC/CLR             | Time base control. When OSC/CLK is at logic "1", the output of the M-957's internal oscillator is selected as the time base. When OSC/CLK is at logic "0" and XIN is at logic "1", the AUXCLK input is selected as the time base.                                                                                         |  |  |  |  |

| AUXCLK              | Auxiliary clock input. When OSC/CLK is at logic "0" and XIN is at logic "1", the AUXCLK input is selected as the M-957's time base. The auxiliary input must be 3.58 MHz divided by 8 for the M-957 to operate to specifications. If unused, AUXCLK should be left open.                                                  |  |  |  |  |

| VNA, VND            | Negative analog and digital power supply connections. Separated on the chip for greater system flexibility, VNA and VND should be at equal potential.                                                                                                                                                                     |  |  |  |  |

| VP                  | Positive power supply connection.                                                                                                                                                                                                                                                                                         |  |  |  |  |

| N/C                 | Not connected. These pins have no internal connection and may be left floating.                                                                                                                                                                                                                                           |  |  |  |  |

Table 2 DTMF to Binary Decoding

| SIGNAL      | LOW-<br>FREQUENCY<br>COMPONENT | HIGH-<br>FREQUENCY<br>COMPONENT | HEX<br>OUTPUT<br>FORMAT | 2-OF-8<br>OUTPUT<br>FORMAT |  |

|-------------|--------------------------------|---------------------------------|-------------------------|----------------------------|--|

|             | (Hz)                           | (Hz)                            | 3210                    | 3210                       |  |

|             | 605                            | 1000                            | 0 0 0 1                 | 0000                       |  |

| 1           | 697<br>697                     |                                 |                         | 0000                       |  |

| 2 2         | 697                            | 1336<br>1477                    | 0010                    | 0010                       |  |

| 2<br>3<br>4 | 770                            | 1209                            | 0100                    | 0100                       |  |

| *           | 770                            | 1209                            | 1 0100                  | 0.00                       |  |

| 5           | 770                            | 1336                            | 0101                    | 0101                       |  |

| 5<br>6<br>7 | 770                            | 1477                            | 0110                    | 0110                       |  |

| 7           | 852                            | 1209                            | 0111                    | 1000                       |  |

| 8           | 852                            | 1336                            | 1000                    | 1001                       |  |

|             |                                |                                 |                         |                            |  |

| 9           | 852                            | 1477                            | 1001                    | 1010                       |  |

| 0           | 941                            | 1336                            | 1010                    | 1101                       |  |

| *           | 941                            | 1209                            | 1011                    | 1100                       |  |

| #           | 941                            | 1477                            | 1100                    | 1110                       |  |

| Α           | 697                            | 1633                            | 1101                    | 0011                       |  |

| В           | 770                            | 1633                            | 1110                    | 0111                       |  |

| Ç           | 852                            | 1633                            | liiii                   | 1011                       |  |

| D           | 941                            | 1633                            | 0000                    | liiii                      |  |

| 2           | 1 "                            |                                 |                         |                            |  |

Note: The M-957 detects signals A through D only when the 12/16 input is at logic "0".

Figure 3 Timing Diagram

Figure 4 Telephone Line Differential Input Interface

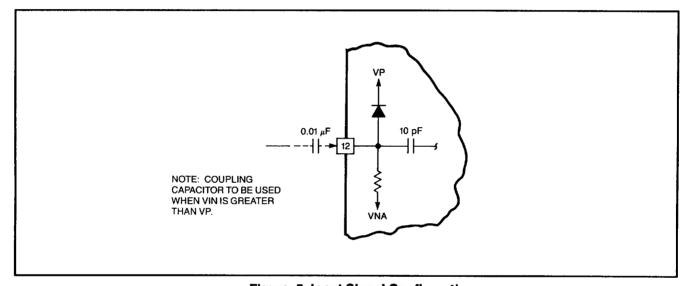

Figure 5 Input Signal Configuration

## Table 3 Absolute Maximum Ratings (Note 1)

| DC Supply Voltage (Note 2)          |

|-------------------------------------|

| Voltage on SIGNAL IN                |

| Voltage on Any Pin Except SIGNAL IN |

| Storage Temperature Range           |

| Operating Temperature Range         |

| Lead Soldering Temperature          |

| Power Dissipation                   |

## Notes:

- 1. Exceeding these ratings may permanently damage the M-957.

- $2. \quad VP \ \text{referenced to VND. VND should be at equal potential to VNA. VND/VNA may be at ground.}$

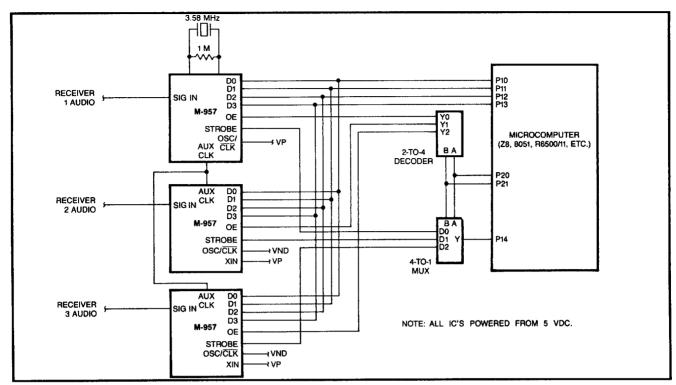

Figure 6 Multiple Receiver/Microprocessor interface

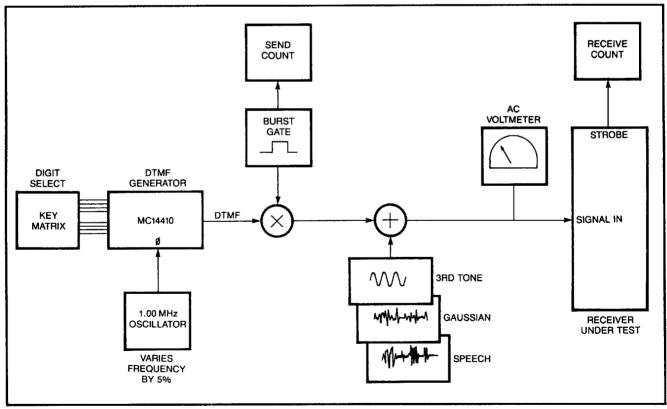

Figure 7 Test Circuit

Table 4 Specifications

|                                   | Parameter                                     | Conditions                                                            | Min                    | Тур                | Max                 | Units                    | Notes       |

|-----------------------------------|-----------------------------------------------|-----------------------------------------------------------------------|------------------------|--------------------|---------------------|--------------------------|-------------|

| SIGNAL IN Input<br>Requirements   | Signal Level (per tone)                       | VP=12V<br>A=0, B=0<br>A=1, B=0<br>A=0, B=1<br>A=1, B=1<br>VP=5V       | -24<br>-27<br>-30      |                    | +6<br>+3<br>0<br>-  | dBm<br>dBm<br>dBm<br>dBm | <br>        |

|                                   |                                               | A=0, B=0<br>A=1, B=0<br>A=0, B=1<br>A=1, B=1                          | -32<br>-35<br>-38<br>- | -<br>-<br>-<br>-40 | -2<br>-5<br>-8<br>- | dBm<br>dBm<br>dBm<br>dBm | 1<br>1<br>1 |

|                                   | Signal Duration                               | _                                                                     | 40                     | -                  | _                   | ms                       | ŀ           |

|                                   | Interval Between Signals                      | _                                                                     | 40                     | _                  | _                   | ms                       |             |

|                                   | Signal Present Without Detection              | _                                                                     | _                      | _                  | 20                  | ms                       |             |

|                                   | Interruption of Signal Without Redetection    | _                                                                     | _                      | _                  | 20                  | ms                       |             |

|                                   | Signal Frequency Deviation With Detection     | _                                                                     | _                      | ±2.5%              | ± (1.5% +2)         | Hz                       |             |

|                                   | Signal Frequency Deviation Without Detection  | _                                                                     | ± 3.5%                 | ±3.0%              |                     | Hz                       |             |

|                                   | Twist                                         | _                                                                     |                        |                    | ± 10                | dB                       | 2           |

|                                   | Gaussian Noise                                | _                                                                     | _                      | 12                 | A-7                 | dB                       | 3           |

|                                   | Dial Tone Level<br>(per tone, F≤480 Hz)       | _                                                                     | _                      | _                  | A + 22              | dB                       | 4           |

| Digital Input<br>Requirements     | Logic 0 Voltage                               | VP = 12V<br>VP = 5V                                                   | 0                      |                    | 3.6<br>1.5          | v<br>v                   | 5<br>5      |

|                                   | Logic 1 Voltage                               | VP = 12V<br>VP = 5V                                                   | 8.4<br>3.5             | <u>-</u>           | 12.0<br>5.0         | v<br>v                   | 5<br>5      |

| Digital Output<br>Characteristics | Logic 0 Voltage                               | $VP = 12V, I_O = 1.0 \text{ mA}$<br>$VP = 5V, I_O = 0.4 \text{ mA}$   | 0                      | _                  | 1.2<br>0.5          | V<br>V                   | 5           |

|                                   | Logic I Voltage                               | $VP = 12V, I_O = -0.5 \text{ mA}$<br>$VP = 5V, I_O = -0.2 \text{ mA}$ | 10.8<br>4.5            | _<br>_             | 12.0<br>5.0         | V<br>V                   | 5<br>5      |

|                                   | Tri-State Leakage                             | _                                                                     | _                      | -                  | 10.0                | uA                       |             |

| Miscellaneous<br>Characteristics  | CMOS Latch-up Voltage                         | _                                                                     | 20                     | _                  | _                   | v                        | 6           |

|                                   | SIGNAL IN Input Impedance                     | F=1 kHz,<br>paralleled with 15 pF                                     | 100k                   | _                  | _                   | ohms                     |             |

| Power<br>Requirements             | Supply Current                                | VP = 12V<br>VP = 5V                                                   | _                      | 17<br>6            | 40<br>18            | mA<br>mA                 |             |

|                                   | Power Dissipation (Outputs Open)              | VP = 12V<br>VP = 5V                                                   | _<br>_                 | 204<br>30          | 480<br>90           | mW<br>mW                 | 7<br>7      |

|                                   | Power Supply Wide Band Noise $(A = 0, B = 0)$ | _                                                                     | _                      |                    | 10                  | mVpp                     |             |

#### Notes:

<sup>1.</sup> With an ambient temperature of 25°C, the signal duration and signal interval at minimum, and the signal frequency deviation and twist at maximum. The unit "dBm" refers to decibels above or below a reference power of one milliwatt into a 600-ohm load. (For example, -24 dBm equals 49 mVrms.)

<sup>2.</sup> Twist is defined as the ratio of the level of the high-frequency DTMF component to the level of the low-frequency DTMF component.

<sup>3.</sup> With an ambient temperature of 25 °C, the signal level at A + 5, the signal frequency deviation and twist at 0, and the signal applied 50 ms off and 50 ms on. The A level is the minimum detect level selected.

<sup>4.</sup> With the signal duration and signal interval at minimum, and the signal frequency deviation and twist at maximum. The A level is the minimum detect level selected.

<sup>5.</sup> Logic levels shown are referenced to VND.

<sup>6.</sup> Power supply excursions above this value can cause device damage.

<sup>7.</sup> For an ambient temperature of  $25\,^{\circ}$  C.

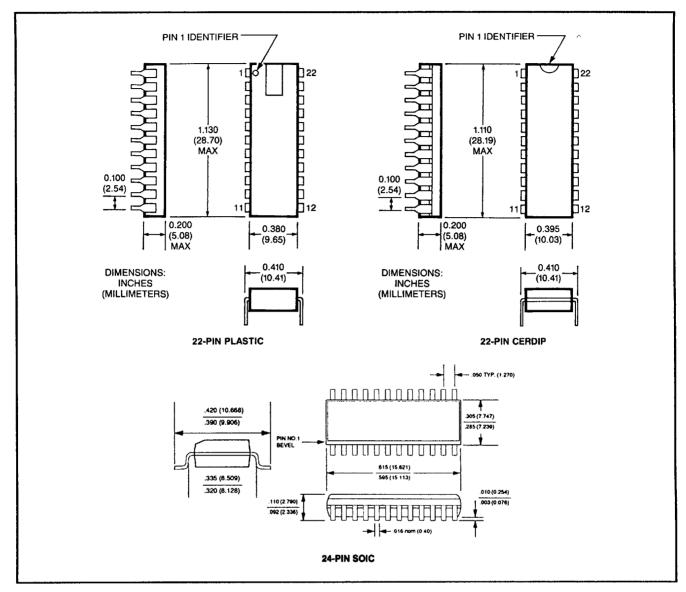

Figure 8 Package Dimensions

## **Ordering Information**

M-957-01 DTMF Receiver, 5-12 Volt, plastic package

M-957-02 DTMF Receiver, 5-Volt, plastic package

M-957-01C DTMF Receiver, 5-12 Volt, CerDIP

M-957-02C DTMF Receiver, 5-Volt, CerDIPpackage

M-957-01S DTMF Receiver, 5-12 Volt, plastic SOIC