# RC288ACL/VFC, RC240ACL/VFC and RC192ACL/VFC Integrated V.Fast Class™(V.FC™) Low Power Data and Fax Modem Device Set Family

### INTRODUCTION

The Rockwell V.Fast Class™ (V.FC™) integrated modem device set family supports ultra high speed data and high speed fax operation. Models are provided that meet different requirements for data throughput and options (Table 1). Each model consists of modem data pump and controller devices and supporting firmware.

As a data modem, the modem operates at line speeds to 28800 bps (RC288ACL/VFC), 24000 bps (RC240ACL/VFC), or 19200 bps (RC192ACL/VFC). Error correction (V.42/MNP 2-4) and data compression (V.42 bis/MNP 5) maximize data transfer integrity and boost data throughput up to 115.2 kbps, 96 kbps, or 76.8 kbps. The modem also operates in non-error-correcting mode.

As a fax modem, the modem supports Group 3 send and receive rates up to 14400 bps and supports T.30 protocol. Extended "AT" commands provide data, fax class 1 and class 2, MNP 10, and world-class functions while using minimal external ROM, RAM, and optional NVRAM. Models supporting US/Canada and multiple countries with different memory requirements are available (Table 1).

The modem operates over a dial-up telephone line, can auto-dial and auto-answer, and can operate in both synchronous and asynchronous modes. Configuration information can be stored in non-volatile memory.

A PC-based "ConfigurACE™" utility program can be used to customize the MCU firmware to specific application and country requirements.

The MCU is packaged in an 80-pin plastic quad flat pack (PQFP). The MDP is available in two PQFPs (one 100-pin and one 80-pin) or in a 68-pin plastic leaded chip carrier (PLCC).

With low power consumption and small footprint, low profile PQFP packages meeting PCMCIA Type II envelope requirements, this modem is ideal for PCMCIA PC Cards or inclusion on motherboards for battery-powered portable applications such as notebook computers.

Accelerator kits are available to minimize application design time and costs.

V.Fast Class, V.FC, and ConfigurACE are trademarks of Rockwell International.

MNP is a trademark of Microcom Systems, Inc.

Hayes is a trademark of Hayes Microcomputer Products, Inc.

#### **FEATURES**

- Data modem throughput up to 115.2 kbps

- V.Fast Class (V.FC), V.32 bis, V.32, V.22 bis,

V.22A/B, V.23, and V.21; Bell 212A and 103

- -V.42 LAPM and MNP 2-4 error correction

- -V.42 bis and MNP 5 data compression

- MNP 10 data throughput enhancement (to V.32 bis)

- Fax modem send and receive rates up to 14400 bps

- -V.17, V.29, V.27 ter, and V.21 channel 2

- · World-class operation (option)

- -V.25 bis commands (asynchronous only)

- -Call progress and blacklisting parameters

- -Multiple country support

- Hayes AutoSync (option)

- ConfigurACE utility program

- Communication software compatible command sets

- -AT, fax class 1, and fax class 2 commands

- S registers

- Built-in DTE interfaces

- -DTE speed up to 115.2 kbps

- -Parallel 16550A UART-compatible interface

- -Serial CCITT V.24 (EIA/TIA-232-E)

- · Line quality monitoring and auto retrain

- NVRAM directory and stored profiles

- Flow control and speed buffering

- · Automatic format/speed sensing

- Serial synchronous and asynchronous data

- · Parallel asynchronous data

- · Auto dial and auto answer

- Tone, pulse, and adaptive dialing

- Calling Number Delivery (Caller ID) detect

- Diagnostics

- · Extended operating temperature models available

- +5V operation

- Typical power consumption:

| Mode         | Power   |

|--------------|---------|

| Normal       |         |

| RC288ACL/VFC | 790 mW  |

| RC240ACL/VFC | 710 mW  |

| RC192ACL/VFC | 600 mW  |

| Sleep        | 20.0 mW |

| Stop         | 9.8 mW  |

|              |         |

CMOS VLSI devices

- -MCU: One 80-pin PQFP

- -MDP: Two PQFPs (a 100-pin and an 80-pin) or one 68-pin PLCC

Data Sheet (Preliminary)

Table 1. Modem Models, Functions, and Memory Requirements

|                    | Supported Functions <sup>2</sup> |       |         |          | External ROM |         |

|--------------------|----------------------------------|-------|---------|----------|--------------|---------|

| Model <sup>1</sup> | Fax                              | MNP10 | W-Class | AutoSync | Country      | (Bytes) |

| RC288ACL-D/VFC     | -                                | _     | _       | _        | US/Can       | 64k     |

| RC288ACL/VFC       | s                                | _     | _       | _        | US/Can       | 64k     |

| RC288ACL(/A)/VFC   | s                                | S     | _       | Α        | US/Can       | 128k    |

| RC288ACLW-D/VFC    | _                                | S     | S       | S        | Multiple     | 128k    |

| RC288ACLW(E)/VFC   | S                                | S     | S       | S        | Multiple     | 128k    |

| RC240ACL-D/VFC     | _                                | -     | _       | _        | US/Can       | 64k     |

| RC240ACL/VFC       | S                                | -     | _       | _        | US/Can       | 64k     |

| RC240ACL(/A)/VFC   | s                                | S     | _       | Α        | US/Can       | 128k    |

| RC240ACLW-D/VFC    | -                                | S     | S       | S        | Multiple     | 128k    |

| RC240ACLW(E)/VFC   | s                                | S     | S       | S        | Multiple     | 128k    |

| RC192ACL-D/VFC     | _                                | -     | _       | -        | US/Can       | 64k     |

| RC192ACL/VFC       | s                                | -     | -       | _        | US/Can       | 64k     |

| RC192ACL(/A)/VFC   | s                                | s     | _       | Α        | US/Can       | 128k    |

| RC192ACLW-D/VFC    | _                                | S     | S       | S        | Multiple     | 128k    |

| RC192ACLW/VFC      | s                                | s     | S       | s        | Multiple     | 128k    |

1. Option notations:

-D Data only (no fax).

W World class support.

(/A) Optional AutoSync support.

(E) Optional industrial temperature range.

2. Supported functions (A = Optionally supported; S = Supported; - = Not supported):

Fax Fax class 1 and class 2 command functions.

MNP 10 Data throughput enhancement functions.

W-Class World class functions supporting multiple country requirements.

AutoSync Hayes AutoSync available with 128k-byte ROM installed.

#### **TECHNICAL OVERVIEW**

#### **GENERAL DESCRIPTION**

The modem device set provides the processing core of the modem. The OEM adds external memory, crystal, discrete components, and a digital access arrangement (DAA) circuit to complete the modem system.

#### **System Configuration**

The modern device set consists of a Microcontroller (MCU) and a Modern Data Pump (MDP).

The OEM provides external memory for the MCU (64k/128k bytes ROM and 32k bytes RAM).

#### Modem Data Pump (MDP)

The MDP is a Rockwell RC288DPL/VFC, RC240DPL/VFC, or RC192DPL/VFC 2-wire data/fax modem data pump packaged in two PQFPs (a 100-pin PQFP and an 80-pin PQFP) or one 68-pin PLCC.

As a data modem, the MDP can operate in full-duplex, synchronous/asynchronous modes at line rates up to 28800 bps. Using a proprietary scheme to optimize modem configuration for line conditions, the MDP can connect at the highest data rate that the channel can support from 28800 bps (RC288DPL/VFC), 24000 bps (RC240DPL/VFC), or 19200 bps (RC192DPL/VFC) to 14400 bps with automatic fallback. Automode operation in V.32 bis is provided in accordance with EIA/TIA-PN2330.

As a fax modem, the MDP fully supports Group 3 facsimile send and receive speeds of 14400, 12000, 9600, 7200, 4800, and 2400 bps.

#### Microcontroller (MCU)

The MCU is a Rockwell L39 microcomputer packaged in a 80-pin PQFP.

MCU performs the command processing and host interface functions.

The MCU connects to the host via a V.24 (EIA/TIA-232-E) serial interface or a parallel microcomputer bus. The MCU connects to the MDP via dedicated lines and the external bus. The MCU external bus also connects to OEM-supplied ROM and RAM. The MCU external memory is 64k or 128k bytes ROM (45 ns) and 32k bytes RAM (45 ns). For W-class models, buffered switch inputs and latched indicator/control outputs can optionally be connected to the MCU external bus.

For all models, 256 bytes NVRAM can optionally be connected to the MCU over a dedicated serial interface.

The MCU crystal frequency is 14.7456 MHz.

#### **MCU Firmware**

MCU firmware performs processing of general modem control, command sets, error correction, MNP 10, fax class 1 and class 2, and DTE interface functions. The MCU firmware is provided by Rockwell in object code form for the OEM to program into external ROM. The MCU

firmware may also be provided in source code form under a source code addendum license agreement.

#### SUPPORTED INTERFACES

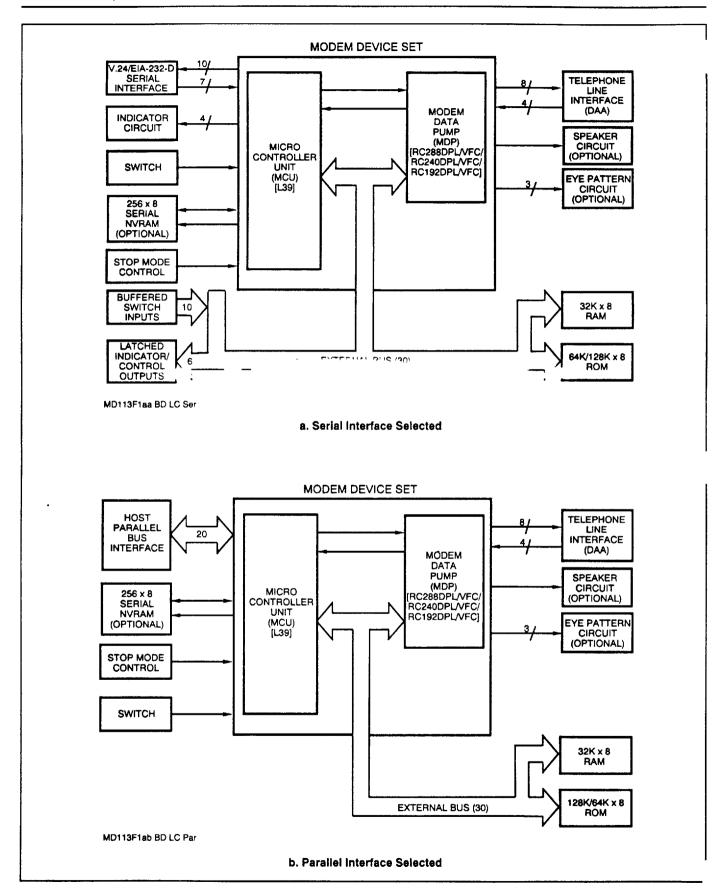

The major hardware signal interfaces of the modern device set are illustrated in Figure 1.

#### Parallel Host Bus Interface

A 16550A UART-compatible parallel interface is provided.

Eight data lines, three address lines, and nine control lines are supported.

#### Serial/Switch/Indicator Interface

A DTE serial interface, direct connect and bit mapped switch inputs, and indicator/control outputs are supported.

Serial Interface. A 16-line V.24 and EIA/TIA-232-E logic-compatible serial interface to the DTE is supported. A clock stop output signal is provided which can be used to turn off transmitter and receiver clocks to the DTE in asynchronous modes.

**Switch Interface.** A direct connect strap input can be sampled. Thirteen switch inputs, bit-mapped through an external three-state buffer, can be sampled in the world-class (W-class) configuration.

Indicator Interface. Four direct connect indicator outputs are supported. Six indicator outputs, bit-mapped through an external latch, are supported in W-class configurations.

#### Stop Mode Control

The STPMODE input is supported which controls modem entry into Stop Mode.

#### **NVRAM** Interface

A serial interface to the optional OEM-supplied 256-byte non-volatile RAM (NVRAM) is provided. Data stored in NVRAM can take precedence over the factory default settings. The 256-byte NVRAM can store up to two user-selectable configurations and can store up to four 45-digit dial strings.

#### Speaker Interface

A speaker output, controlled by AT or V.25 bis commands, is provided for an optional OEM-supplied speaker circuit.

#### MCU External Bus Interface

The MCU external bus connects to the MDP, ROM, RAM, and, for W-class configuration, a switch input buffer and indicator output latches. The non-multiplexed bus supports eight bidirectional data lines and 17 address lines. Dedicated MDP, ROM, and RAM chip select and control outputs as well as indicator/control device chip select outputs are also provided.

#### Line Interface

MDP. The MDP connects to the line interface circuitry via a receive analog input, two transmit analog outputs, a relay driver output, and a ring signal input. The relay output may be used to drive the Caller ID relay.

Figure 1. Modem General Interface

MCU. The MCU provides four relay control outputs to the line interface. These outputs may be used to control relays such as off-hook, pulse, mute, A/A1, earth, and talk/data. The MCU accepts ring signal and line current sense from the line interface.

#### Eye Pattern Generator Interface

Eye pattern data, clock, and sync interface signals are provided to allow an external eye pattern generator circuit to be easily added in order to observe modem performance relative to line impairments.

#### **COMMANDS**

The modem supports data modem, fax class 1 and 2, MNP 10, and W-class commands and S Registers (see Tables 2 and 3, respectively) depending on the modem model.

**Data Modem Operation.** Data modem functions operate in response to the basic AT commands when +FCLASS=0. Default parameters support US/Canada operation.

MNP 10 Operation (Option). MNP 10 functions operate in response to MNP 10 commands.

AutoSync Operation (Option). AutoSync operates in response to the &Q4 command.

World Class (W-Class) Operation. W-class functions operate in response to W-class AT and V.25 bis commands.

Fax Modem Operation (Option). Facsimile functions operate in response to fax class 1 commands when +FCLASS=1 or to fax class 2 commands when +FCLASS=2.

#### DATA MODEM OPERATION

#### Automatic Speed/Format Sensing (Serial Interface)

The modem can automatically determine the speed and format of the data sent from the DTE (serial interface only). The modem can sense speeds of 300, 600, 1200, 2400, 4800, 7200, 9600, 12000, 14400, 16800, 19200, 21600, 24000, 26400, 28800, 38400, 57600, and 115200 bps and the following data formats:

| Parity | Data Length (No. of Bits) | No. of<br>Stop Bits | Character Length (No. of Bits) |

|--------|---------------------------|---------------------|--------------------------------|

| None   | ` 7                       | `2                  | 10                             |

| Odd    | 7                         | 1                   | 10                             |

| Even   | 7                         | 1                   | 10                             |

| None   | 8                         | 1                   | 10                             |

| Odd    | 8                         | 1                   | 11 *                           |

| Even   | 8                         | 1                   | 11 *                           |

<sup>\* 11-</sup>bit characters are sensed, but the parity bits are stripped off during data transmission in Normal and Error Correction modes. Direct mode does not strip off the parity bits.

The modem can speed sense data with mark or space parity and configures itself as follows:

| DTE Configuration | Modem Configuration |

|-------------------|---------------------|

| 7 mark            | 7 none              |

| 7 space           | 8 none              |

| 8 mark            | 8 none              |

| 8 space           | 8 even              |

MD113C1

#### **ESTABLISHING DATA MODEM CONNECTIONS**

Note: Default parameter values support modem operation in the U.S. For modem use in a different country, parameter values can be changed using ConfigureACE.

#### **Telephone Number Directory**

The modem supports four telephone number entries in a directory that can be saved in a serial NVRAM. Each telephone number can be up to 45 characters in length. A telephone number can be saved using the &Zn=x command and a saved telephone number can be dialed using the DS=n command.

#### Dialing

**DTMF Dialing.** DTMF dialing using DTMF tone pairs is supported in accordance with CCITT Q.23. The transmit tone level complies with Bell Publication 47001.

Pulse Dialing. Pulse dialing is supported in accordance with EIA/TIA-496-A.

Adaptive Dialing. If DTMF dialing is selected (T command) and the telephone network will not recognize DTMF tones, the modem will switch to pulse dialing. If pulse dialing is selected (P command), pulse dialing will be used.

Blind Dialing. The modem can blind dial in the absence of a dial tone if enabled by the X0, X1, or X3 command.

#### **Modem Handshaking Protocol**

If a tone is not detected within the time specified in the S7 register after the last digit is dialed, the modem aborts the call attempt.

#### **Call Progress Tone Detection**

Ringback, equipment busy, and progress tones can be detected in accordance with the applicable standard.

#### **Answer Tone Detection**

Answer tone detection can be detected over the frequency range of 2100  $\pm$  40 Hz in CCITT modes and 2225  $\pm$  40 Hz in Bell modes.

#### **Ring Detection**

A ring signal can be detected from a TTL-compatible 15.3 Hz to 68 Hz square wave input.

#### **Billing Protection**

When the modem goes off-hook to answer an incoming call, both transmission and reception of data are prevented for 2 seconds (data modem) or 4 seconds (fax adaptive answer) to allow transmission of the billing signal.

#### **Connection Speeds**

The modem functions as a data modem when the +FCLASS=0 command is active. The possible data connection modes/speeds are listed in Table 4. Two methods of establishing a connection are supported: use of the F command and use of N command, speed sense, and S37 register combination.

Table 2. AT Commands

| Command    | Function                                 |

|------------|------------------------------------------|

|            | Basic AT Commands                        |

| A/         | Re-execute command                       |

| Ä          | Answer a call                            |

| Bn         | Set CCITT or Bell Mode                   |

| Cn         | Carrier control                          |

| Dn         | Dial (originate a call)                  |

| E          | Command echo                             |

| Fn         | Select line modulation                   |

| Hn         | Disconnect (hang-up)                     |

| In         | Identification                           |

| Ln         | Speaker volume                           |

| <b>M</b> n | Speaker control                          |

| Nn         | Automode enable                          |

| On         | Return to on-line data mode              |

| P          | Set pulse dial default                   |

| Qn         | Quiet results codes control              |

| Sn=x       | Write to S Register                      |

| Sn?        | Read S Register                          |

| T          | Set tone dial default                    |

| Vn         | Result code form                         |

| Wn         | Error correction message control         |

| Xn         | Extended result codes                    |

| Yn         | Long space disconnect                    |

| Zn         | Soft reset and restore profile           |

| &Cn        | RLSD (DCD) option                        |

| &Dn        | DTR option                               |

| &F         | Restore factory configuration (profile)  |

| &Gn<br>&Jn | Select guard tone Telephone jack control |

| &Kn        | Flow control                             |

| &Mn        | Asynchronous/synchronous mode selection  |

| &Pn        | Select pulse dial make/break ratio       |

| &Qn        | Asynchronous/synchronous mode selection  |

| &Rn        | RTS/CTS option                           |

| &Sn        | DSR override                             |

| &Tn        | Test and diagnostic                      |

| &V         | Display current configuration and stored |

|            | profiles                                 |

| &Wn        | Store current configuration              |

| &Xn        | Select synchronous clock source          |

| &Yn        | Designate a default reset profile        |

| &Zn=x      | Store phone number                       |

| %En        | Enable/disable line quality monitor and  |

|            | auto-retrain or fallback/fall forward    |

| %L         | Report line signal level                 |

| %Q         | Report line signal quality               |

| %TTn       | PTT testing utilities                    |

| \Gn        | Modem-to-modem flow control (XON/XOFF)   |

| \Kn        | Break control                            |

| ₩n         | Operating mode                           |

| #CID       | Caller ID detection and reporting        |

| **         | Download to flash memory                 |

|            |                                          |

|            |                                          |

|            |                                          |

|            |                                          |

|            |                                          |

Table 2. AT Commands (Cont'd)

| Command                                | Function                                            |

|----------------------------------------|-----------------------------------------------------|

|                                        | ECC AT Commands                                     |

| %C                                     | Select data compression                             |

| ∖An                                    | Maximum MNP block size                              |

| ∖Bn                                    | Transmit BREAK to remote                            |

| \Ln                                    | MNP block transfer control                          |

| ······································ | MNP 10 AT Commands                                  |

| )Mn                                    | Enable cellular power level adjustment              |

| * Hn                                   | Set link negotiation speed                          |

| -Kn                                    | MNP extended services                               |

| -Qn                                    | Enable fallback to V.22 bis/V.22                    |

| @Mn                                    | Select initial transmit level                       |

| :E                                     | Compromise equalizer enable                         |

| · <u>C</u>                             | Fax Class 1 AT+F Commands                           |

| . EOL ACC                              |                                                     |

| +FCLASS=n                              |                                                     |

| +FTS=n                                 | Stop transmission and wait                          |

| +FRS=n                                 | Receive silence                                     |

| +FTM=n                                 | Transmit data                                       |

| +FRM=n                                 | Receive data                                        |

| +FTH=n                                 | Transmit data with HDLC framing                     |

| +FRH=n                                 | Receive data with HDLC framing                      |

|                                        | Fax Class 2 AT+F Commands                           |

| +FCLASS=n                              |                                                     |

|                                        | Class 2 Action Commands                             |

| +FCIG                                  | Set the polled station identification               |

| +FDT                                   | Data transmission                                   |

| +FET=N                                 | Transmit page punctuation                           |

| +FDR                                   | Begin or continue Phase C receive data              |

| +FK                                    | Terminate session                                   |

| +FLPL                                  | Document for polling                                |

| +FSPL                                  | Enable polling                                      |

|                                        | Class 2 DCE Responses                               |

| +FCIG:                                 | Report the polled station identification            |

| +FCON                                  | Facsimile connection response                       |

| +FDCS:                                 | Report current session                              |

| +FDIS:                                 | Report remote capabilities                          |

| +FDTC:                                 | Report the polled station capabilities              |

| +FCFR                                  | Indicate confirmation to receive                    |

| +FTSI:                                 | Report the transmit station ID                      |

| +FCSI:                                 | Report the called station ID                        |

| +FPTS:                                 | Page transfer status                                |

| +FET:                                  | Post page message response                          |

| +FHNG:                                 | Call termination with status                        |

| +FPOLL                                 | Indicates polling request                           |

|                                        | Class 2 Session Parameters                          |

| +FMFR?                                 | Identify manufacturer                               |

| +FMDL?                                 | Identify manufacturer                               |

| +FREV?                                 | Identify revision                                   |

| +FDCC                                  | DCE capabilities parameters                         |

| +FDIS                                  | ·                                                   |

| +FDCS                                  | Current sessions parameters Current session results |

| +FUCS                                  |                                                     |

|                                        | Local ID string                                     |

| +FPTS                                  | Page transfer status                                |

| +FCR                                   | Capability to receive                               |

| +FAA                                   | Adaptive answer Buffer size (read only)             |

| . EDITED                               | Duber Size (read only)                              |

| +FBUF?                                 |                                                     |

| +FPHCTO                                | Phase C time out                                    |

|                                        |                                                     |

Table 2. AT Commands (Cont'd)

| Command    | Function                                  |  |  |  |  |

|------------|-------------------------------------------|--|--|--|--|

|            | W-Class AT Commands                       |  |  |  |  |

| %Fn        | Split-speed direction select              |  |  |  |  |

| \ <b>S</b> | Display active configuration              |  |  |  |  |

| \W         | Split-speed operation                     |  |  |  |  |

| *B         | Display blacklisted numbers               |  |  |  |  |

| *D         | Display delayed numbers                   |  |  |  |  |

| *NCnn      | Country select                            |  |  |  |  |

|            | W-Class V.25 bis Commands                 |  |  |  |  |

| CIC        | Connect incoming call                     |  |  |  |  |

| CNL        | Execute AT command (if permitted)         |  |  |  |  |

| CRN        | Call request with number                  |  |  |  |  |

| CRS        | Call request with memory address          |  |  |  |  |

| DIC        | Disregard incoming call                   |  |  |  |  |

| PRN        | Program normal                            |  |  |  |  |

| RLD        | Request list of delayed call numbers      |  |  |  |  |

| RLF        | Request list of forbidden call numbers    |  |  |  |  |

| RLN        | Request stored number list (dial strings) |  |  |  |  |

|            |                                           |  |  |  |  |

|            |                                           |  |  |  |  |

Table 3. S Registers

| Popletor       | Function                                        |

|----------------|-------------------------------------------------|

| Register<br>S0 |                                                 |

| S1             | Rings to auto-answer Ring counter               |

| S2             | Escape character                                |

| S3             | Carriage return character                       |

| S4             | Line feed character                             |

| S5             | Backspace character                             |

| S6             | Maximum time to wait for dial tone              |

| Ť              |                                                 |

| S7             | Wait for carrier                                |

| S8<br>S9       | Pause time for dial delay modifier              |

| S10            | Carrier detect response time                    |

| 1 7 17         | Carrier loss disconnect time DTMF Tone Duration |

| S11            |                                                 |

| S12            | Escape code guard time                          |

| S13            | Reserved                                        |

| S14            | General bit mapped options                      |

| S15            | Reserved                                        |

| S16            | Test mode bit mapped options (&T)               |

| S17            | Reserved                                        |

| S18            | Test timer                                      |

| S19-S20        | Reserved                                        |

| S21            | V24/general bit mapped options                  |

| S22            | Speaker/results bit mapped options              |

| S23            | General bit mapped options                      |

| S24            | Sleep inactivity timer                          |

| S25            | Delay to DTR (CT108) off                        |

| S26            | RTS-to-CTS (CT105-to-CT106) delay               |

| S27            | General bit mapped options                      |

| S28            | General bit-mapped options                      |

| S29            | Flash modifier time                             |

| S30            | Inactivity timer                                |

| S31            | General bit-mapped options                      |

| S32            | XON character                                   |

| S33            | XOFF character                                  |

| S34-S35        | Reserved                                        |

| S37            | Line connection speed                           |

| S38            | Delay before forced hangup                      |

| S39            | Flow control                                    |

| S40            | General bit-mapped options                      |

| S41            | General bit-mapped options                      |

| S42-S45        | Reserved                                        |

| S91            | PSTN transmit attenuation level                 |

| S92            | Fax transmit attenuation level                  |

| S95            | Result code messages control                    |

|                | ECC S Registers                                 |

| S36            | LAPM failure control                            |

| S46            | Data compression control                        |

| S48            | V.42 negotiation control                        |

| S82            | Break handling control                          |

| S86            | Call failure reason code                        |

|                | W-Class S Registers                             |

| S80            | Soft-switch functions                           |

|                | Cellular Registers                              |

| S201           | Cellular transmit level                         |

|                | www.aran stantorius IQTO                        |

| İ              |                                                 |

| 1              |                                                 |

|                |                                                 |

|                |                                                 |

|                |                                                 |

| 1              |                                                 |

|                |                                                 |

#### **Automode**

Automode detection can be enabled by the N1 or F0 commands to allow the modem to connect to a remote modem in V.FC mode or in accordance with EIA/TIA-PN2330. Automode is disabled on a leased line.

#### **DATA MODE**

Data mode exists when a telephone line connection has been established between modems and all handshaking has been completed.

#### Speed Buffering (Normal Mode)

Speed buffering allows a DTE to send to, and receive data from, a modem at a speed different than the line speed. The modem supports speed buffering at all line speeds.

#### **Flow Control**

**DTE-to-Modem Flow Control.** If the modem-to-line speed is less than the DTE-to-modem speed, the modem supports XOFF/XON or RTS/CTS flow control with the DTE to ensure data integrity.

Modem-to-Modem Flow Control. When enabled by the \G1 command, the modem supports XON/XOFF flow control with the remote modem to ensure data integrity. Modem-to-modem flow control is not used in error correction mode. In this case, flow control is accomplished within the error-correction protocol.

#### **Escape Sequence Detection**

The "+++" escape sequence with guard time can be used to return control to the command mode from the data mode. Escape sequence detection is disabled by a S2 Register value greater than 127. Escape sequence detection is disabled in synchronous mode.

#### **BREAK Detection**

The modem can detect a BREAK signal from either the DTE or the remote modem. The \Kn command determines the modem response to a received BREAK signal.

#### Telephone Line Monitoring

GSTN Cleardown (V.FC, V.32 bis, V.32). Upon receiving GSTN Cleardown from the remote modem in a non-error correcting mode, the modem cleanly terminates the call.

Loss of Carrier. If carrier is lost for a time greater than specified by the S10 register, the modern will disconnect.

Receive Space Disconnect. If selected by the Y1 command in non-error-correction mode, the modem will disconnect after receiving 1.6  $\pm$  10% seconds of continuous SPACE.

#### Send SPACE on Disconnect

If selected by the Y1 command in non-error-correction mode, the modem will send  $4 \pm 10\%$  seconds of continuous SPACE when a locally commanded hang-up is issued by the &Dn or H command.

#### Fall Forward/Fallback (V.FC, V.32 bis/V.32)

During initial handshake, the modem will fallback to the optimal line connection within V.FC mode if the remote modem is a V.FC modem, or within V.32 bis/V.32 mode i. the remote modem is a V.32 bis/V.32 modem, depending upon signal quality if automode is enabled by the N1 command.

When connected in V.FC or V.32 bis/V.32 mode, the modem will fall forward or fallback to the optimal line speed within the connected mode depending upon signal quality if fall forward/fallback is enabled by the %E2 command.

#### Retrain

The modem may lose synchronization with the received line signal under poor line conditions. If this occurs, retraining may be initiated to attempt recovery depending on the type of connection.

The modem initiates a retrain if line quality becomes unacceptable if enabled by the %E command. The modem continues to retrain until an acceptable connection is achieved or until 30 seconds elapse which will result in telephone line disconnect.

#### Synchronous Data Mode (Serial Interface Only)

The modem can establish a synchronous connection in accordance with the &Mn or &Qn commands. Upon completing the physical handshake, the modem enters synchronous data mode. The inactivity timer is not used during synchronous data mode.

#### **Direct Mode (Serial Interface Only)**

The Direct mode allows data to be transmitted and received directly from the DTE and remote modem. The Direct mode is selected with the &Q0 or \N1 command. In Direct mode, no flow control characters are recognized or transmitted, the modem cannot execute error correction, and the inactivity timer is not used. Speed buffering is disabled in Direct mode.

**Table 4. Connection Speed Options**

| Configuration | Rate                                                                                |

|---------------|-------------------------------------------------------------------------------------|

| V.FC          | 28800 <sup>1</sup> , 26400 <sup>1</sup> , 24000 <sup>2</sup> , 21600 <sup>2</sup> , |

|               | 19200, 16800, or 14400 bps                                                          |

| V.32 bis      | 14400, 12000, 9600, 7200,                                                           |

|               | or 4800 bps                                                                         |

| V.32          | 9600 or 4800 bps                                                                    |

| V.22 bis      | 2400 or 1200 bps                                                                    |

| V.22          | 1200 bps                                                                            |

| V.23          | 1200Tx/75Rx or 75Tx/1200Rx                                                          |

| V.21          | 0-300 bps                                                                           |

| Bell 212A     | 1200 bps                                                                            |

| Bell 103      | 0-300 bps                                                                           |

#### Notes:

- 1. RC288ACL/VFC.

- 2. RC288ACL/VFC and RC240ACL/VFC.

#### **Programmable Inactivity Timer**

The modem will disconnect from the line if data is not sent or received for a specified length of time. In normal or error-correction mode, this inactivity timer is reset when data is received from either the DTE or from the line. This timer can be set to a value between 0 and 2550 seconds by register S30. A value of 0 disables the inactivity timer.

#### DTE Signal Monitoring

DTR. When DTR is asserted, the modem responds in accordance with the &Dn and &Qn commands.

RTS. RTS is used for flow control if enabled by the &K command in normal or error-correction mode, or to affect the CTS output if enabled by the &R command in synchronous mode.

RDL. When RDL is asserted, the modem requests a remote digital loop if connected in non-error-correction mode (serial interface only).

AL. When AL is asserted, the modern disconnects and enters analog loop (serial interface only).

#### **ERROR CORRECTION AND DATA COMPRESSION**

#### V.42 Error Correction

V.42 supports two methods of error correction: LAPM and, as a alternative, MNP 4. The modem provides a detection and negotiation technique for determining and establishing the preferred method of error correction between two moderns.

#### MNP 2-4 Error Correction

MNP 2-4 is a data link protocol that uses error correction algorithms to ensure data integrity. MNP block or stream mode operation may be selected by the \Ln command.

In stream mode, the modem sends data frames in varying lengths depending on the amount of time between characters coming from the DTE.

In block mode, the modem sends data frames of 256 characters in length. Special communication software must be used when using block mode.

#### V.42 bis Data Compression

V.42 bis data compression mode, enabled by the %Cn or S46 command, operates when a LAPM or MNP 10 connection is established.

The V.42 bis data compression employs a "string learning" algorithm in which a string of characters from the DTE is encoded as a fixed length codeword. Two 2k-byte dictionaries are used to store the strings. These dictionaries are dynamically updated during normal operation.

#### **MNP 5 Data Compression**

MNP 5 data compression mode, enabled by the %Cn command, operates during an MNP connection.

In MNP 5, the modern increases its throughput by compressing data into tokens before transmitting it to the remote modem, and by decompressing encoded received data before sending it to the DTE.

## MNP 10 DATA THROUGHPUT ENHANCEMENT (TO V.32 BIS)

MNP10 protocol, cellular functionality, and MNP Extended Services enhance performance under adverse channel conditions such as those found in rural, long distance, or cellular environments. An MNP 10 connection is established when either an MNP 2-4 connection is negotiated with a remote modern supporting MNP 10 or MNP 10 extended services is enabled as described below. MNP 10 functions include:

Robust Auto-Reliability. Higher connection success rate is achieved by attempting to overcome channel interference during the modern negotiation phase while maintaining backward compatibility with non-MNP 10 moderns.

Negotiated Speed Upshift. Initial connection and MNP handshake is performed at the most dependable speed, then the connection upshifts to the highest supported modem/channel speed. This function is particularly useful in channel conditions with high connection failure rates.

Aggressive Adaptive Packet Assembly. Frame size is dynamically changed to quickly adapt to varying levels of interference.

Dynamic Speed Shifting. Connection speed is shifted upward or downward to optimize data throughput for the channel conditions by continuously monitoring the line quality and link performance.

Dynamic Transmit Level Adjustment. Transmit level is dynamically adjusted to adapt to the varying cellular network environment and to prevent "clipping," which causes data corruption, due to the Preemphasis and Compander effect.

MNP 10 Extended Services. The modem can quickly switch to MNP 10 operation when the remote modem supports MNP 10 and both modems are configured to operate in V.42.

V.42 bis/MNP 5 Support. MNP 10 can operate with V.42 bis or MNP 5 data compression.

#### **FAX CLASS 1 AND CLASS 2 OPERATION**

The modem operates as a facsimile (fax) DCE whenever the +FCLASS=1 or +FCLASS=2 command is active. In the fax mode, the on-line behavior of the modem is different from the data (non-fax) mode. After dialing, modem operation is controlled by the fax commands. Some AT commands are still valid but may operate differently from data modem mode.

#### **Calling Tone**

Calling tone is generated in accordance with T.30.

#### WORLD CLASS COUNTRY SUPPORT

The W-class models include functions which support modem operation in multiple countries. The following capabilities are provided in addition to the data modem functions previously described. Country dependent parameters are all programmable by ConfigurACE.

#### V.25 bis Commands

V.25 bis commands (Table 2) are available in asynchronous modes when enabled by the AT/V25B bit in the External Buffer 1 inputs.

#### **Blacklist Parameters**

tablished by ConfigurACE.

The modem can operate in accordance with requirements of individual countries to prevent misuse of the network by limiting repeated calls to the same number when previous call attempts have failed. Call failure can be detected for reasons such as no dial tone, number busy, no answer, no ringback detected, voice (rather than modem) detected, and key abort (dial attempt aborted by user). Actions resulting from such failures can include specification of minimum inter-call delay, extended delay between calls, and maximum numbers of retries before the pumber is permanently forbidden ("bl. sted"). In the permanenter are established.

#### Dialing

**Dial Tone Detection.** Dial tone detection levels and frequency ranges are programmable by ConfigurACE.

**DTMF Dialing.** Transmit output level, DTMF signal duration, and DTMF interdigit interval parameters are programmable by ConfigurACE.

**Pulse Dialing.** Parameters such as make/break times, set/clear times, and dial codes are programmable by ConfigurACE.

**Ring Detection.** The frequency range is programmable by ConfigurACE.

Adaptive Dialing. Adaptive dialing can be disabled by ConfigurACE.

Blind Dialing. Blind dialing, permitted only in some countries, can be enabled or disabled by setting or resetting a flag bit in the corresponding country file using ConfigurACE. If enabled, blind dialing can be invoked using the ATX command; if disabled, blind dialing is not available.

#### Carrier Transmit Level

The carrier transmit level is programmable by ConfigurACE to match specific country and DAA characteristics.

#### **Calling Tone**

Calling tone is generated in accordance with V.25. Calling tone may be toggled (enabled/disabled) by inclusion of a "^" character in a dial string. It may also be enabled or

disabled by programming a country specific parameter using ConfigurACE.

#### **Call Progress Tone Detection**

Frequency and cadence of tones for busy, ringback, congested, dial tone 1, and dial tone 2 are programmable by ConfigurACE.

#### **Answer Tone Detection**

The answer tone detection period is programmable by ConfigurACE.

#### **Relay Control**

On-hook/off-hook, make/break, and set/clear relay control parameters are programmable by ConfigurACE.

#### **Automatic Country Code Recognition**

Automatic country code recognition is supported in conjunction with country identification code circuitry provided in the DAA. Automatic country code recognition is enabled using the AT\*NCnn command with nn = 0. Automatic country code recognition is disabled using the AT\*NCnn command with nn = any valid country code other than 0.

parameters in Table 9.)

Once enabled, the MCU interrogates the DAA circuit upon reset (POR or the ATZ command) or attempt to go off-hook. An 8-bit country code is shifted in from the DAA and is used to look up the corresponding country code parameters loaded in ROM. If country code parameters are present for the shifted-in country code and the country is different from the active country, the country code parameters are loaded. If the shifted-in country code does match a country with stored parameters in ROM, the modem issues an ERROR message.

Note that when automatic country code recognition is enabled, the country code can be changed at any time before going off-hook (e.g., by changing the DAA or selecting a different country code on the DAA). Upon going off-hook, the MCU will then load the country code parameters corresponding to the new DAA country code.

#### ConfigurACE UTILITY PROGRAM

The ConfigurACE utility program allows the OEM to customize the MCU firmware to suit specific application and country requirements. ConfigurACE allows programming of functions such as:

- Loading of multiple sets of country parameters

- Call progress and blacklisting parameters

- -Entry of S register maximum/minimum values

- -Use of "soft switches" instead of panel switches

- -Modification/limitation of transmit levels

- -Modification of result codes

- Modification of factory default values

- -Customization of the ATI4 response

- -Customization of fax OEM messages

This program, which runs on a PC-compatible computer, modifies the hex object code which can be programmed

directly into the system ROM. Lists of the generated parameters can be displayed or printed.

Rockwell-provided country parameter files allow a complete set of country-specific call progress and blacklisting parameters to be selected.

#### DIAGNOSTICS

#### **Commanded Tests**

Diagnostics are performed in response to &T commands, serial interface control signals, or switch inputs per V.54.

Analog Loopback. Data from the local DTE is sent to the modern, which loops the data back to the local DTE.

Analog Loop Self Test. An internally generated test pattern of alternating 1s and 0s (reversals) is sent to the modem. An error detector within the modem checks for errors in the string of reversals.

Remote Digital Loopback (RDL). Data from the local DTE is sent to the remote modem which loops the data back to the local DTE.

Remote Digital Loopback with Self Test. An internally generated pattern is sent from the local modem to the remote modem which loops the data back to the local modem.

Local Digital Loopback. When local digital loop is requested from the local DTE, two data paths are set up in the local modem. Data from the local DTE is looped back to the local DTE (path 1) and data received from the remote modem is looped back to the remote modem (path 2).

#### **Power On Reset Tests**

Upon power on, or receipt of the Z command, the modem performs tests of the MDP, RAM, ROM, and NVRAM.

#### LOW POWER MODES

#### Sleep Mode

Entry. The modem will enter the low power sleep mode when no line connection exists and no host activity occurs for the period of time specified in the S24 register. All MCU circuits are turned off except the internal MCU clock circuitry in order to consume lower power but be able to immediately wake up and resume normal operation.

Wake-Up. Wakeup occurs when a ring is detected on the telephone line, the host writes to the modem (parallel interface version) or the DTE sends a character to the modem (serial interface version).

#### Stop Mode

**Entry.** The modem will enter the low power stop mode when the STPMODE input is asserted. All MCU circuits are turned off including the internal MCU clock circuitry in order to consume lower power than sleep mode. The modem will enter stop mode immediately, terminating a

line connection, terminating any test in process, and allowing any data in the Receive Buffer Register to clear.

STPMODE must be returned high before the modem can wake-up.

Wake-Up. Wakeup occurs when a ring is detected on the telephone line, the host writes to the modem (parallel interface version) or the DTE sends a character to the modem (serial interface version). Since the modem requires more time to attain normal operation when waking up from Stop mode rather than from Sleep mode, the host must send a character to the modem before issuing the first AT command.

#### **CALLER ID**

Caller ID can be enabled/disabled using the #CID command. When enabled, caller ID information (date, time, caller code, and name) can be passed to the DTE in formatted or unformatted form. Inquiry support allows the current caller ID mode and mode capabilities of the modem to be retrieved from the modem.

#### **ADDITIONAL INFORMATION**

Additional information is described in the RC288ACL/VFC Modern Designer's Guide (Order No. 1032) and the AT Command Reference Manual for RC288ACL/VFC and RC288ACi/VFC Modern Families (Order No. 1034).

#### HARDWARE INTERFACE

#### HARDWARE INTERFACE SIGNALS

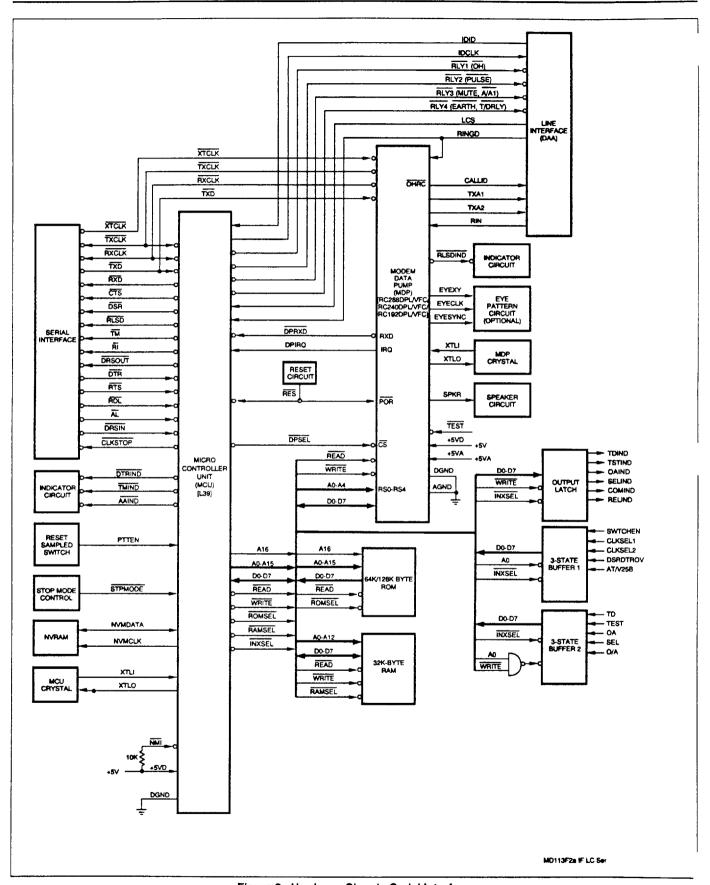

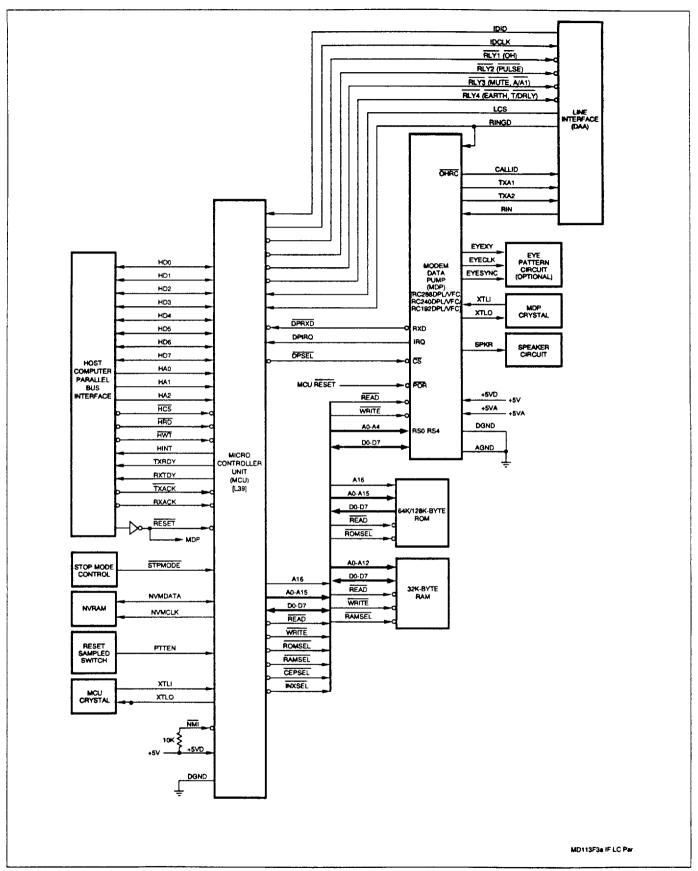

The modem hardware interface signals for serial and parallel interface configurations are shown in Figures 2 and 3, respectively.

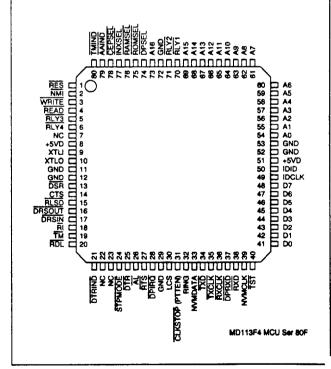

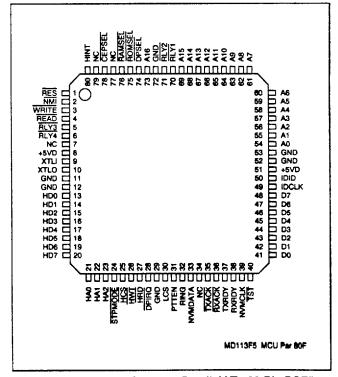

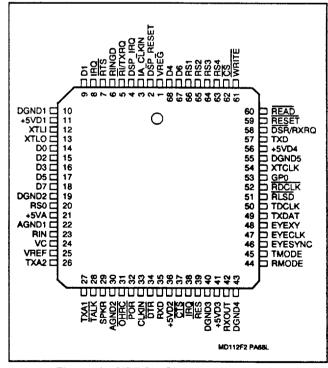

The MCU pin assignments for serial interface firmware are shown in Figure 4 and are listed in Table 5.

The MCU pin assignments for parallel interface firmware are shown in Figure 5 and are listed in Table 6.

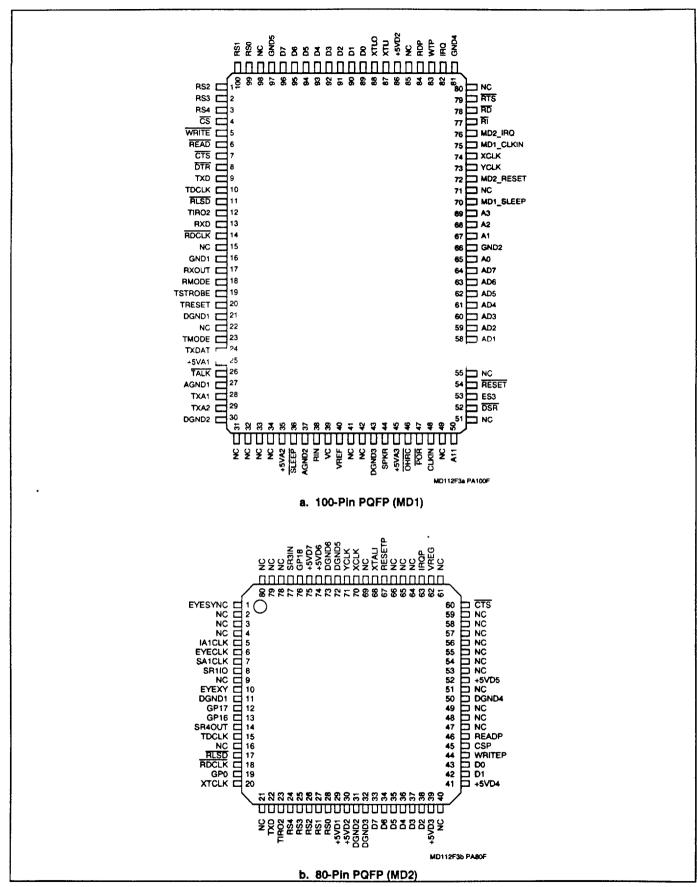

The MDP pin assignments are shown in Figure 6 and are listed in Table 7.

The MCU hardware interface signals are defined in Table 8.

The MDP hardware interface signals are defined in Table 9.

The digital electrical characteristics for the hardware interface signals are listed in Table 10.

The analog electrical characteristics for the hardware interface signals are listed in Table 11.

The current and power requirements are listed in Table 12.

The absolute maximum ratings are listed in Table 13.

Table 14 shows the parallel interface registers and the corresponding bit assignments.

Figure 2. Hardware Signals-Serial Interface

Figure 3. Hardware Signals-Parallel Interface

Table 5. MCU Pin Signals - Serial I/F - 80-Pin PQFP

| Pin | MCU Signal | I/O Type | Modem Signal         |

|-----|------------|----------|----------------------|

| 1   | RES        | IC       | RES                  |

| 2   | NMI        | _        | NMI (Note 4)         |

| 3   | WT         | OA       | WRITE                |

| 4   | RD         | OA       | READ                 |

| 5   | PE2        | OA       | RLY3 (MUTE, A/A1)    |

| 6   | PE3        | OA       | RLY4 (EARTH, T/DRLY) |

| 7   | PSC        | IA       | PSC                  |

| 8   | VCC1       | PWR      | vcc                  |

| 9   | XTLI       | ΙE       | XTLI                 |

| 10  | XTLO       | OE       | хтьо                 |

| 11  | GND        | GND      | GND                  |

| 12  | GND        | GND      | GND                  |

| 13  | PC0        | OA       | DSR                  |

| 14  | PC1        | OA       | CTS                  |

| 15  | PC2        | OA       | RLSD                 |

| 16  | PC3        | OA       | DRSOUT               |

| 17  | PC4        | OA       | DRSIN                |

| 18  | PC5        | OA       | RI                   |

| 19  | PC6        | OA       | TM                   |

| 20  | PC7        | IA       | RDL                  |

| 21  | PD0        | OA       | DTRIND               |

| 22  | PD1        | -        | NC                   |

| 23  | PD2        | IA       | NC                   |

| 24  | PD3        | IA       | STPMODE              |

| 25  | PD4        | IA IA    | DTR                  |

| 26  | PD5        | ΪA       | AL                   |

| 27  | PD6        | IA       | RTS                  |

| 28  | PD7        | IA       | DPIRQ                |

| 29  | GND        | GND      | GND                  |

| 30  | PE4        | IA       | LCS                  |

| 31  | PE5        | OA [IA]  | CLKSTOP [PTTEN]      |

| 32  | PAO        | IA       | RINGD                |

| 33  | PA1        | ÖA       | NVMDATA (Note 4)     |

| 34  | PA2        | IA I     | TXD                  |

| 35  | PA3        | IA I     | TXCLK                |

| 36  | PA4        | IA       | RXCLK                |

| 37  | PA5        | MI       | DPRXD                |

| 38  | PA6        | OA       | RXD                  |

| 39  | PA7        | OA       | NVMCLK               |

| 40  | TST        |          | TST (Note 5)         |

| 41  | DO         | IA/OA    | D0                   |

| 42  | D1         | IA/OA    | D1                   |

| 43  | D2         | IA/OA    | D2                   |

| 44  | D3         | IA/OA    | D3                   |

| 45  | D4         | IA/OA    | D4                   |

| 46  | D5         | IA/OA    | D5                   |

| 47  | D6         | IA/OA    | D6                   |

| 48  | D7         | IA/OA    | D7                   |

| 49  | PE6        | OA       | IDCLK                |

| 50  | PE7        | IA       | IDID                 |

| 51  | VCC2       | PWR      | vcc                  |

| 52  | GND        | GND      | GND                  |

| 53  | GND        | GND      | GND                  |

| 54  | AO         | OA       | A0                   |

| 55  | A1         | OA       | A1                   |

| 56  | A2         | OA       | A2                   |

| 57  | A2<br>A3   | OA       | A3                   |

| 1   | A3<br>A4   | 1        | A3                   |

| 58  | A4<br>A5   | OA       |                      |

| 59  |            | OA       | A5                   |

| 60  | A6         | OA       | A6                   |

Table 5. MCU Pin Signals-Ser I/F-80-Pin PQFP (Cont'd)

| Pin        | MCU Signal | I/O Type | Modem Signal |

|------------|------------|----------|--------------|

| 61         | A7         | OA       | A7           |

| 62         | A8         | OA       | A8           |

| 63         | A9         | OA       | A9           |

| 64         | A10        | OA       | A10          |

| <b>6</b> 5 | A11        | OA       | A11          |

| 66         | A12        | OA       | A12          |

| 67         | A13        | OA       | A13          |

| 68         | A14        | OA       | A14          |

| 69         | A15        | OA       | A15          |

| 70         | PE0        | OA       | RLY1 (OH)    |

| 71         | PE1        | OA       | RLY2 (PULSE) |

| 72         | GND        | GND      | GND          |

| 73         | PB0        | OA       | A16          |

| 74         | PB1        | MI       | DPSEL        |

| 75         | PB2        | OA       | ROMSEL       |

| 76         | PB3        | OA       | RAMSEL       |

| 77         | PB4        | OA       | INXSEL       |

| 78         | PB5        | OA       | CEPSEL       |

| 79         | PB6        | OA       | AAIND        |

| 80         | PB7        | OA       | TMIND        |

| Makes      |            |          |              |

- 1. MI = Modern interconnect.

- 2. NC = No external connection.

- 3. NU = Not used; connect as noted.

- 4. Connect to VCC through 10 KΩ.

- 5. Connect to GND.

Figure 4. MCU Pin Signals - Serial I/F - 80-Pin PQFP

Table 6. MCU Pin Signals - Parallel I/F - 80-Pin PQFP

| Pin | MCU Signal    | I/O Type | Modem Signal         |

|-----|---------------|----------|----------------------|

| 1   | RES           | IC       | RES                  |

| 2   | NMI           |          | NMI (Note 4)         |

| 3   | <del>₩T</del> | OA       | WRITE                |

| 4   | RD            | OA       | READ                 |

| 5   | PE2           | OA       | RLY3 (MUTE, A/A1)    |

| 6   | PE3           | OA       | RLY4 (EARTH, T/DRLY) |

| 7   | PSC           | IA       | PSC                  |

| 8   | VCC1          | PWR      | VCC                  |

| 9   | XTLI          | ΙE       | XTLI                 |

| 10  | XTLO          | OE       | XTLO                 |

| 11  | GND           | GND      | GND                  |

| 12  | GND           | GND      | GND                  |

| 13  | PC0           | IA/OA    | HD0                  |

| 14  | PC1           | IA/OA    | HD1                  |

| 15  | PC2           | IA/OA    | HD2                  |

| 16  | PC3           | IA/OA    | HD3                  |

| 17  | PC4           | IA/OA    | HD4                  |

| 18  | PC5           | IA/OA    | HD5                  |

| 19  | PC6           | IA/OA    | HD6                  |

| 20  | PC7           | IA/OA    | HD7                  |

| 21  | PD0           | IA       | HA0                  |

| 22  | PD1           | IA       | HA1                  |

| 23  | PD2           | IA       | HA2                  |

| 24  | PD3           | IA       | STPMODE              |

| 25  | PD4           | IA       | HCS                  |

| 26  | PD5           | IA       | HWT                  |

| 27  | PD6           | IA       | HRD                  |

| 28  | PD7           | IA       | DPIRQ                |

| 29  | GND           | GND      | GND                  |

| 30  | PE4           | IA       | LCS                  |

| 31  | PE5           | IA       | PTTEN                |

| 32  | PA0           | IA       | RINGD                |

| 33  | PA1           | OA       | NVMDATA (Note 4)     |

| 34  | PA2           |          | NC NC                |

| 35  | PA3           | IA.      | TXACK                |

| 36  | PA4           | IA.      | RXACK                |

| 37  | PA5           | OA       | TXRDY                |

| 38  | PA6           | OA       | RXRDY                |

| 39  | PA7           | OA       | NVMCLK               |

| 40  | TST           |          | TST (Note 5)         |

| 41  | D0            | IA/OA    | D0                   |

| 42  | D1            | IA/OA    | D1                   |

| 43  | D2            | IA/OA    | D2                   |

| 44  | D3            | IA/OA    | D3                   |

| 45  | D4            | IA/OA    | D4                   |

| 46  | D5            | IA/OA    | D5                   |

| 47  | D6            | IA/OA    | D6                   |

| 48  | D7            | IA/OA    | D7                   |

| 49  | PE6           | OA       | IDCLK                |

| 50  | PE7           | IA       | IDID                 |

| 51  | VCC2          | PWR      | VCC                  |

| 52  | GND           | GND      | GND                  |

| 53  | GND           | GND      | GND                  |

| 54  | A0            | OA       | A0                   |

| 55  | A1            | OA       | A1                   |

| 56  | A2            | OA       | A2                   |

| 57  | A3            | OA       | A3                   |

| 58  | A4            | OA       | A4                   |

| 59  | A5            | OA       | A5                   |

| 60  | A6            | OA       | A6                   |

Table 6. MCU Pin Signals-Par I/F-80-Pin PQFP (Cont'd)

| Pin | MCU Signal | I/O Type | Modem Signal |

|-----|------------|----------|--------------|

| 61  | A7         | OA       | A7           |

| 62  | A8         | OA       | A8           |

| 63  | A9         | OA       | <b>A9</b>    |

| 64  | A10        | OA       | A10          |

| 65  | A11        | OA       | A11          |

| 66  | A12        | OA       | A12          |

| 67  | A13        | OA       | A13          |

| 68  | A14        | OA       | A14          |

| 69  | A15        | OA       | A15          |

| 70  | PE0        | OA       | RLY1 (OH)    |

| 71  | PE1        | OA       | RLY2 (PULSE) |

| 72  | GND        | GND      | GND          |

| 73  | PB0        | OA       | A16          |

| 74  | PB1        | MI       | DPSEL        |

| 75  | PB2        | OA       | ROMSEL       |

| 76  | PB3        | OA       | RAMSEL       |

| 77  | PB4        |          | NC           |

| 78  | PB5        | OA       | CEPSEL       |

| 79  | PB6        |          | NC           |

| 80  | PB7        | OA       | HINT         |

- 1. MI = Modem interconnect.

- 2. NC = No external connection.

- 3. NU = Not used; connect as noted.

- 4. Connect to VCC through 10 K $\Omega$ .

- 5. Connect to GND.

Figure 5. MCU Pin Signals - Parallel I/F - 80-Pin PQFP

Figure 6a. Pin Signals - 100-Pin and 80-Pin PQFPs

Table 7a. MDP Pin Signals - 100-Pin PQFP (MD1)

Interface Pin Signal Label | I/O Type RS<sub>2</sub> Host Parallel Interface 1 RS3 IA Host Parallel Interface 2 3 RS4 IA Host Parallel Interface <del>CS</del> ΙA Host Parallel Interface 4 5 WRITE IΑ Host Parallel Interface 6 READ IΑ Host Parallel Interface 7 CTS OA DTE Serial Interface 8 DTR IΑ DTE Serial Interface 9 TXD IA DTE Serial Interface 10 **TDCLK** OA DTE Serial Interface 11 RLSD OA DTE Serial Interface TIRO2 MD2: TIRO2 12 MI 13 RXD OA DTE Serial Interface RDCLK OA DTE Senal Interface 14 15 NC GND GND<sub>1</sub> 16 **RXOUT** MI MD2: SR3IN 17 RMODE MD1: TMODE/MD2: SR110 18 М MD2: IA1CLK TSTROBE MI 19 TRESET MD2: SA1CLK MI 20 DGND1 GND 21 22 NC **TMODE** MD1: RMODE/MD2: SR1IO 23 М **TXDAT** MD2: SR4OUT 24 25 +5VA1 **PWR** TALK OD Line Interface 26 27 AGND1 **GND** 28 TXA1 O(DD) Line Interface 29 TXA2 O(DD) Line Interface 30 DGND2 GND 31 NC 32 NC 33 NC 34 NC **PWR** 35 +5VA2 SLEEP 36 Mi MD1: MD1\_SLEEP AGND2 **GND** 37 38 RIN I(DA) Line Interface 39 VC MI To GND through capacitors **VREF** 40 МΙ To VC through capacitors 41 NC NC 42 43 **DGND3 GND** O(DF) 44 SPKR Speaker Circuit **PWR** +5VA3 45 **OHRC** OD Line Interface 46 Connect to MCU RES POR MI 47 CLKIN MD1: MD1\_CLKIN 48 MI NC 49 50 A11 MI MD2: RS4 (Note 3) 51 NC DSR OA DTE Serial Interface 52 MD2: CSP 53 ES3 MI MD1: POR RESET IA 54 55 NC **PWR** 56 +5VD1 57 AD0 Mi MD2: D0 58 AD1 MI MD2: D1 MI 59 AD2 MD2: D2 AD3 ΜI MD2: D3 60

Table 7a. MDP Pin Signals - 100-Pin PQFP (MD1) (Cont'd)

| Pin    | Signal Label | I/O Type    | Interface               |  |  |

|--------|--------------|-------------|-------------------------|--|--|

| 61     | AD4          | MI          | MD2: D4                 |  |  |

| 62     | AD5          | М           | MD2: D5                 |  |  |

| 63     | AD6          | MI          | MD2: D6                 |  |  |

| 64     | AD7          | MI          | MD2: D7                 |  |  |

| 65     | <b>A</b> 0   | MI          | MD2: RS0                |  |  |

| 66     | GND2         | GND         |                         |  |  |

| 67     | A1           | MI          | MD2: RS1                |  |  |

| 68     | A2           | MI          | MD2: RS2                |  |  |

| 69     | A3           | MI          | MD2: RS3                |  |  |

| 70     | MD1_SLEEP    | MI          | MD1: SLEEP              |  |  |

| 71     | NC           |             |                         |  |  |

| 72     | MD2_RESET    | MI          | MD2: RESETP             |  |  |

| 73     | YCLK         | MI          | MD2: YCLK               |  |  |

| 74     | XCLK         | MI          | MD2: XCLK               |  |  |

| 75     | MD1_CLKIN    | MI          | MD1: CLKIN              |  |  |

| 76     | MD2_IRQ      | MI          | MD2: IRQP               |  |  |

| 77     | RI           | OA          | DTE Serial Interface    |  |  |

| 78     | RD           | IA          | Line Interface          |  |  |

| 79     | RTS          | IA          | DTE Serial Interface    |  |  |

| 80     | NC           |             | (See Note 4.)           |  |  |

| 81     | GND4         | GND         |                         |  |  |

| 82     | IRQ          | OA          | Host Parallel Interface |  |  |

| 83     | WTP          | MI          | MD2: WTP                |  |  |

| 84     | RDP          | Mi          | MD2: RDP                |  |  |

| 85     | NC           |             |                         |  |  |

| 86     | +5VD2        | PWR         |                         |  |  |

| 87     | XTLI         | 1           | Crystal/Clock Circuit   |  |  |

| 88     | XTLO         | 0           | Crystal/Clock Circuit   |  |  |

| 89     | D0           | IA/OA       | Host Parallel Interface |  |  |

| 90     | D1           | IA/OA       | Host Parallel Interface |  |  |

| 91     | D2           | IA/OA       | Host Parallel Interface |  |  |

| 92     | D3           | IA/OA       | Host Parallel Interface |  |  |

| 93     | D4           | IA/OA       | Host Parallel Interface |  |  |

| 94     | D5           | IA/OA       | Host Parallel Interface |  |  |

| 95     | D6           | IA/OA       | Host Parallel Interface |  |  |

| 96     | D7           | IA/OA       | Host Parallel Interface |  |  |

| 97     | GND5         | GND         |                         |  |  |

| 98     | NC<br>DSS    | l           |                         |  |  |

| 99     | RS0          | IA.         | Host Parallel Interface |  |  |

| 100    | RS1          | <u> </u> IA | Host Parallel Interface |  |  |

| Notes: |              |             |                         |  |  |

1. I/O Type:

MI = Modern interconnect.

IA, IB = Digital input.

OA, OB, OD = Digital output.

I(DA)] = Analog input.

O(DD), O(DF) = Analog output.

2. NC = no external connection.

- 3. Pin 50 (A11) is functionally compatible with RC144DPL 100-pin PQFP pin 50 (A13).

- Pin 80 (NC internally) can be connected to GND for functional compatibility with RC144DPL 100-pin PQFP pin 80 (GND3).

Table 7b. MDP Pin Signals - 80-Pin PQFP (MD2)

| EYESYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Pin | Signal Label | I/O Type | Interface                             |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|----------|---------------------------------------|--|

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1   | EYESYNC      | OA       | Eye Pattern Test Circuit              |  |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2   | NC           |          |                                       |  |

| S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3   | NC           |          |                                       |  |

| 6         EYECLK         MI         Eye Pattern Test Circuit           7         SA1CLK         MI         MD1: TRESET           8         SR1IO         MI         MD1: TMODE           9         NC         D         Eye Pattern Test Circuit           10         EYEXY         OA         Eye Pattern Test Circuit           11         DGND1         GND         Eye Pattern Test Circuit           11         DGND1         GND         Eye Pattern Test Circuit           11         DGND1         GND         Connect to DGND           12         GP16         MI         Connect to DGND           14         SR40UT         MI         MD1: TXDAT           15         TDCLK         IA         DTE: Serial Interface           16         NC         IA         DTE: Serial Interface           17         RISD         IA         DTE: Serial Interface           18         RDCLK         IA         DTE: Serial Interface           20         TXTCLK         IA         DTE: Serial Interface           21         NC         MI         MD1: AD1           22         TXD         IA         MD1: AD1           23         TIRO2 | 4   | NC           |          | 1                                     |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5   | IA1CLK       | MI       | MD1: TSTROBE                          |  |