## 27F64 64K (8K x 8) CHMOS FLASH MEMORY

- Quick-Erase™ Algorithm

- Two Second Typical Array Electrical Erasure

- High Performance Speeds

150 ns Maximum Access Time

- Low Power Consumption

100 µA Maximum Standby Current

- for Power-Down Savings

Quick-Pulse Programming™ Algorithm

One Second Typical Chip Program

- On-Board Program/Erase

New Modes Simplify In-Module

Firmware Upgrades

- 2764A and 27C64 JEDEC Pinout — 28 Pin Cerdip Package (See Packaging Spec., Order # 231369)

- EPROM Based ETOX™ Process

3 Year CHMOS\* EPROM

- Manufacturing Base

Improved Latch-Up Immunity

through EPI Processing

The Intel 27F64 ETOXTM (EPROM tunnel oxide) flash memory is a 64K bit non-volatile memory organized as 8192 bytes of 8 bits. The 27F64 electrically erases all bits in parallel, making it ideal for EPROM applications where U.V. erasure is impractical or time consuming. Electrical erasure allows manufacturers to efficiently implement code changes for testing and end-of-line final configuration.

To decrease the cost of servicing and updating program code, the 27F64 offers new programming and erase modes called On-Board modes. These modes simplify in-circuit programming and erasure by maintaining V<sub>CC</sub> at 5V, and CE and OE at standard logic levels. Devices socketed or soldered to circuit boards can be erased and programmed via an edge connector to a PROM programmer, or via the board tester already available. The Quick-Erase<sup>TM</sup> algorithm and On-Board features give system designers innovative capabilities. Compared to byte-alterable E2PROM, these features address industry's need for a cost-effective code update solution.

Intel's new ETOX flash memory process combines the programming mechanism of EPROM with the erase mechanism of EPROM to produce dense electrically erasable memories with the reliability and manufacturability of today's EPROM technology.

Intel's unique Epitaxial (EPI) processing provides excellent latch-up immunity. Prevention of latch-up is specified for stress up to 100 mA from -1V to  $V_{\rm CC}$  + 1V on address and data pins. All high voltage pins are protected from overshoot up to 14V.

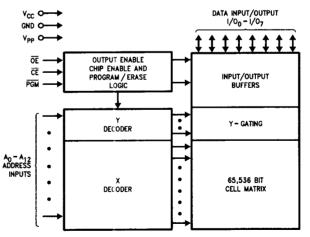

Figure 1. 27F64 Internal Block Diagram

September 1988 Order Number: 290153-004

290153-1

<sup>\*</sup>CHMOS is a patented process of Intel Corporation.

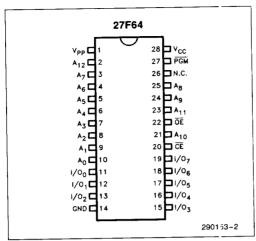

Pin Names Addresses  $A_0 - A_{12}$ Data Input/Output 1/00-1/07 Œ Chip Enable ŌĒ Output Enable **PGM** Program Program/Erase Power  $V_{PP}$ **Device Power**  $V_{CC}$ Ground GND No Internal Connection N.C.

Figure 2. Cerdip (D) Pin Configuration

Table 1. Pin Description

| Symbol                          | Type | Name and Function                                                                                                                                                                                                                                                                                               |

|---------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>12</sub> | I    | ADDRESS BUS inputs the memory addresses, and selects the 8 bits in the 256 row by 256 column array.                                                                                                                                                                                                             |

| 1/00-1/07                       | 1/0  | DATA BUS inputs data during memory program cycles; outputs data during memory read cycles. The data bus is active high and floats to tri-state OFF when the chip is deselected or the outputs disabled.                                                                                                         |

| CE                              | I    | CHIP ENABLE activates the device's control logic, input buffers, decoders, and sense amplifiers. $\overline{CE}$ is active low; $\overline{CE}$ high deselects the memory device and reduces power consumption to standby levels.                                                                               |

| ŌĒ                              | ı    | OUTPUT ENABLE when active low gates the device's output through the data buffers during a read cycle. OE driven to a third logic level V <sub>H</sub> 11.5V–13.0V, selects the conventional chip erase mode.                                                                                                    |

| PGM                             | 1    | PROGRAM controls the program and erase pulse-width in the conventional modes by being driven low. PGM driven to a third logic level V <sub>H</sub> (11.5V – 13.0V) gates entry into the On-Board program verify, erase, and erase verify modes*. In the On-Board erase mode, CE controls the erase pulse width. |

| V <sub>PP</sub>                 |      | PROGRAM/ERASE POWER SUPPLY (12.75V ±0.25V) for programming and erasing the device. Vpp also supplies the Flash memory cell margin voltage during the On-Board program verify and erase verify modes. In these modes, Vpp must switch to 6.25V ±0.25V and 3.25V ±0.25V, respectively.                            |

| V <sub>CC</sub>                 |      | <b>DEVICE POWER</b> for most operations (5V $\pm$ 5%). V <sub>CC</sub> also supplies the memory cell's margin voltage during the conventional program verify and erase verify modes. In these modes, V <sub>CC</sub> must switch to 6.25V $\pm$ 0.25V and 3.25V $\pm$ 0.25V, respectively.                      |

| GND                             |      | GROUND: Reference for the device's circuitry.                                                                                                                                                                                                                                                                   |

| N.C.                            |      | NO INTERNAL CONNECTION to this device. Pin may be driven or left floating.                                                                                                                                                                                                                                      |

<sup>\*</sup>For complete discussion and explanation of the On-Board modes, refer to the On-Board device operation section.

### PRINCIPLES OF OPERATION

The 27F64 features two distinct modes of operation—conventional EPROM and On-Board. Both follow the same program and erase algorithms although the implementations differ. Due to specified V<sub>CC</sub> levels, the conventional modes tend to be more suited to programming and erasure in a PROM programmer, than to in-circuit code alteration. Intel offers the new program and erase methodology (On-Board modes) in consideration of the new trends in system design and manufacturing.

In all cases, the 27F64 flash memory performs the read and standby functions exactly like Intel's 2764A and 27C64 EPROMs.

The following sections discuss the read mode and then the specifics of the two program/erase methodologies. Discussion of conventional modes precedes that of On-Board modes.

### **READ MODE**

The 27F64 is functionally equivalent to the 2764A or 27C64 in the read mode, and can replace either in

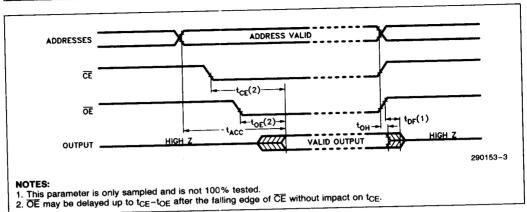

existing designs. The 27F64 has two read control pins, both of which must be logically active to obtain data at the outputs. Chip Enable (CE) controls device selection and activates internal circuitry. Output Enable (OE) controls the selected device's I/O buffers and dates data onto the output pins. The address access time (tACC) specifies the maximum delay time from stable address inputs to valid data out. with CE and OE active low. The chip enable access time (t<sub>CE</sub>) specifies the maximum delay from CE active low to valid data, assuming stable addresses and OE driven low. Valid data becomes available on the outputs a maximum of toe after OE transitions high to low. The top specification assumes stable chip selection and addresses for  $t = t_{ACC}-t_{OE}$  or t<sub>CE</sub>-t<sub>OE</sub>. (See Figure 3. Read Operation A.C. Waveforms for graphical explanation.)

### STANDBY MODE

With  $\overline{CE}$  at a logic high (V<sub>IH</sub>), the standby mode disables most of the 27F64's circuitry and substantially reduces the device's power consumption to 100  $\mu$ A (with CMOS inputs). The outputs assume a high impedance state, independent of the  $\overline{OE}$  input.

| Table 21 Conventional Mode Ocicetton     |                 |                    |                 |                    |                |                                |       |                  |  |

|------------------------------------------|-----------------|--------------------|-----------------|--------------------|----------------|--------------------------------|-------|------------------|--|

| Pins                                     | CE              | ŌĒ                 | PGM             | A <sub>9</sub>     | A <sub>0</sub> | V <sub>PP</sub>                | Vcc   | Outputs          |  |

| Mode                                     |                 | <u> </u>           |                 |                    |                |                                | 1     |                  |  |

| Read                                     | VIL             | V <sub>IL</sub>    | V <sub>IH</sub> | X(1)               | Х              | Vcc                            | 5.0V  | D <sub>OUT</sub> |  |

| Output Disable                           | V <sub>IL</sub> | V <sub>IH</sub>    | V <sub>IH</sub> | X                  | X              | Vcc                            | 5.0V  | High Z           |  |

| Standby                                  | V <sub>IH</sub> | X                  | ×               | X                  | X              | Vcc                            | 5.0V  | High Z           |  |

| Program/Erase Inhibit                    | Х               | ×                  | X               | X                  | Х              | V <sub>CC</sub> <sup>(4)</sup> | 5.0V  |                  |  |

| Program                                  | V <sub>IL</sub> | V <sub>IH</sub>    | VIL             | X                  | Х              | 12.75V                         | 6.25V | DiN              |  |

| Program Verify                           | V <sub>IL</sub> | V <sub>IL</sub>    | V <sub>IH</sub> | X                  | Х              | 12.75V                         | 6.25V | D <sub>OUT</sub> |  |

| Quick-Erase                              | V <sub>IL</sub> | V <sub>H</sub> (2) | VIL             | X                  | Х              | 12.75V                         | 3.25V | High Z           |  |

| Erase Verify                             | V <sub>IL</sub> | VIL                | V <sub>IH</sub> | ×                  | Х              | 12.75V                         | 3.25V | D <sub>OUT</sub> |  |

| int <sub>e</sub> ligent ID™ Manufacturer | V <sub>IL</sub> | VIL                | V <sub>IH</sub> | V <sub>H</sub> (2) | VIF(3)         | Vcc                            | 5.0V  | 89H              |  |

| inteligent ID™ Device                    | VIL             | VII                | ViH             | V <sub>H</sub> (2) | VIH(3)         | Vcc                            | 5.0V  | 03H              |  |

Table 2. Conventional Mode Selection

- 1. X can be V<sub>IL</sub> or V<sub>IH</sub>.

- 2.  $11.5V \le V_H \le 13.0V$ .

- 3.  $A_1 A_8$ ,  $A_{10} A_{12} = V_{1L}$

- 4. With V<sub>PP</sub> ≤ V<sub>CC</sub>, the 27F64 inhibits all erase and program functions.

## ABSOLUTE MAXIMUM RATINGS\*

| Operating Temperature During Read                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Temperature Under Bias 10°C to +80°C                                                                                              |

| Storage Temperature65°C to +125°C                                                                                                 |

| Voltage on Any Pin with Respect to Ground $-2.0$ V to $+7$ V <sup>(2)</sup>                                                       |

| Voltage on Pin A <sub>9</sub> , $\overrightarrow{PGM}$ , or $\overrightarrow{OE}$ with Respect to Ground $-2.0V$ to $+13.5V(2,3)$ |

| V <sub>PP</sub> Supply Voltage with<br>Respect to Ground During<br>Programming/Erase2.0V to +14V(2, 3)                            |

| V <sub>CC</sub> Supply Voltage with Respect to Ground2.0V to +7.0V(2)                                                             |

| Program/Erase Cycles100                                                                                                           |

| Output Short Circuit Current                                                                                                      |

\*Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

NOTICE: Specifications contained within the following tables are subject to change.

#### NOTES:

1. Operating temperature is for commercial product defined by this specification.

- 2. Minimum D.C. input voltage is -0.5V. During transitions, the inputs may undershoot to -2.0V for periods less than 20 ns. Asximum D.C. voltage on output pins is V<sub>CC</sub> + 0.5V, which may overshoot to V<sub>CC</sub> + 2V for periods less than 20 ns. 3. Maximum D.C. Voltage on A<sub>9</sub>, PGM, OE, or V<sub>PP</sub> is 13V. OE, PGM or A<sub>9</sub> may overshoot to 13.5V for periods less than 20 ns. V<sub>PP</sub> may overshoot to 14V for periods less than 20 ns.

- 4. Output shorted for no more than one second. No more than one output shorted at a time.

### Table 3a. Read Operation

### D.C. CHARACTERISTICS TTL/NMOS Compatible

|                 |                                     | L    | imits                 | Unit | Test Conditions                                                                                                |  |

|-----------------|-------------------------------------|------|-----------------------|------|----------------------------------------------------------------------------------------------------------------|--|

| Symbol          | Parameter                           | Min  | Max                   |      |                                                                                                                |  |

| ILI             | Input Leakage Current               |      | ± 1.0                 | μΑ   | $V_{CC} = V_{CC} \text{ max},$<br>$V_{IN} = V_{CC} \text{ or GND}$                                             |  |

| lo              | Output Leakage Current              |      | ± 10                  | μА   | $V_{CC} = V_{CC} \text{ max},$<br>$V_{OUT} = V_{CC} \text{ or GND}$                                            |  |

| 1               | V <sub>CC</sub> Standby Current     |      | 1.0                   | mA   | $V_{CC} = V_{CC} \text{ max}, \overline{CE} = V_{IH}$                                                          |  |

| I <sub>SB</sub> | V <sub>CC</sub> Active Read Current |      | 20, 30                | mA   | $V_{CC} = V_{CC} \text{ max}, \overline{CE} = V_{IL},$<br>$f = 5 \text{ MHz}, I_{OUT} = 0 \text{ mA}^{(1, 4)}$ |  |

| loo.            | V <sub>PP</sub> Read Current        |      | 100                   | μΑ   | $V_{PP} = V_{CC}(2)$                                                                                           |  |

| V <sub>IL</sub> | Input Low Voltage                   | -0.5 | 0.8                   | V    | $V_{PP} = V_{CC}$                                                                                              |  |

| V <sub>IH</sub> | Input High Voltage                  | 2.0  | V <sub>CC</sub> + 0.5 | V    | $V_{PP} = V_{CC}^{(3)}$                                                                                        |  |

| V <sub>OL</sub> | Output Low Voltage                  |      | 0.45                  | ٧    | $I_{OL} = 2.1 \text{ mA},$ $V_{CC} = V_{CC} \text{ min}$                                                       |  |

| V <sub>OH</sub> | Output High Voltage                 | 2.4  |                       | V    | $I_{OH} = -2.5 \text{ mA},$ $V_{CC} = V_{CC} \text{ min}$                                                      |  |

- 1. Maximum active read power is the sum of ICC active + Ipp. The maximum current value is with the outputs unloaded.

- 2.  $V_{PP}$  may be equal to  $V_{CC}$ , or one diode drop below  $V_{CC}$ . 3. If driven higher than  $V_{CC}$  + 0.5V during programming, the data input transistors will forward bias and pull down the bus

- 4. 20 mA for STD versions; 30 mA for -150, -170, and -200 ns versions.

### Table 3b. Read Operation (Continued)

### D.C. CHARACTERISTICS CMOS Compatible

| Symbol           | Parameter                           | Liı                   | nits                  | Unit | Took Conditions                                                                                                     |  |

|------------------|-------------------------------------|-----------------------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------|--|

| <b>O</b> ,20.    | - arameter                          | Min                   | Max                   | Uill | Test Conditions                                                                                                     |  |

| ال               | Input Leakage Current               |                       | ±1.0                  | μΑ   | V <sub>CC</sub> = V <sub>CC</sub> max,<br>V <sub>IN</sub> = V <sub>CC</sub> or GND                                  |  |

| lLO              | Output Leakage Current              |                       | ±10                   | μΑ   | $V_{CC} = V_{CC} \text{ max,}$ $V_{OUT} = V_{CC} \text{ or GND}$                                                    |  |

| I <sub>SB</sub>  | V <sub>CC</sub> Standby Current     |                       | 100                   | μΑ   | $\begin{aligned} & V_{CC} = V_{CC} \text{ max,} \\ & \overline{CE} = V_{CC} \pm 0.2 \text{V}^{(7)} \end{aligned}$   |  |

| lcc <sub>1</sub> | V <sub>CC</sub> Active Read Current |                       | 20, 30                | mA   | $V_{CC} = V_{CC} \text{ max, } \overline{CE} = V_{ L }$<br>$f = 5 \text{ MHz, } I_{OUT} = 0 \text{ mA}^{(1, 5, 6)}$ |  |

| I <sub>PP1</sub> | V <sub>PP</sub> Read Current        |                       | 100                   | μА   | $V_{PP} = V_{CC}(2)$                                                                                                |  |

| V <sub>IL</sub>  | Input Low Voltage                   | -0.5                  | 0.8                   | ٧    | $V_{PP} = V_{CC}(3)$                                                                                                |  |

| V <sub>IH</sub>  | Input High Voltage                  | 0.7 V <sub>CC</sub>   | V <sub>CC</sub> + 0.5 | ٧    | $V_{PP} = V_{CC}(3, 5)$                                                                                             |  |

| V <sub>OL</sub>  | Output Low Voltage                  |                       | 0.40                  | ٧    | I <sub>OL</sub> = 1.6 mA,<br>V <sub>CC</sub> = V <sub>CC</sub> min                                                  |  |

| V <sub>OH1</sub> | Output High Voltage                 | 0.85 V <sub>CC</sub>  |                       | ٧    | $I_{OH} = -2.1 \text{ mA},$<br>$V_{CC} = V_{CC} \text{ min}$                                                        |  |

| V <sub>OH2</sub> |                                     | V <sub>CC</sub> - 0.4 |                       | ٧    | $I_{OH} = -100 \mu\text{A}, (4)$ $V_{CC} = V_{CC} \text{min}$                                                       |  |

#### **NOTES:**

- 1. Maximum active read power is the sum of ICC active + Ipp. The maximum current value is with the outputs unloaded.

- 2. VPP may be equal to VCC, or one diode drop below VCC.

- 3. To maintain CMOS leakage current specifications, do not drive the data inputs above V<sub>CC</sub> or below ground.

- 4.  $V_{OH2}$  specifies the minimum high output voltage with 100  $\mu A$  of bus leakage.

- 5. If driven higher than  $V_{CC}$  + 0.5V during programming, the data input transistor's will forward bias and pull down the bus driver.

- 6. 20 mA for STD versions; 30 mA for -150, -170 and -200 ns versions.

- 7. Signal driving CE is assumed to be in the CMOS logic "1" steady state.

### **READ OPERATION**

#### **Table 4. Read Operation**

### A.C. CHARACTERISTICS 27F64(1) $0 \le T_A \le 70$ °C

| Ve                  | rsions      | V <sub>CC</sub> ±5%                         | D27F64 | -150V05 | D27F64 | -170V05 | D27F64 | -200V05 | D27F64 | -250V05 |      |

|---------------------|-------------|---------------------------------------------|--------|---------|--------|---------|--------|---------|--------|---------|------|

| Symbol              | CI          | haracteristic                               | Min    | Max     | Min    | Max     | Min    | Max     | Min    | Max     | Unit |

| tACC                | Address to  | Output Delay                                |        | 150     |        | 170     |        | 200     |        | 250     | ns   |

| t <sub>CE</sub>     | CE to Outpu | ıt Delay                                    |        | 150     |        | 170     |        | 200     |        | 250     | ns   |

| t <sub>OE</sub>     | OE to Outpu | ıt Delay                                    |        | 65      |        | 70      |        | 75      |        | 100     | ns   |

| t <sub>DF</sub> (2) | OE High to  | Output High Z                               |        | 35      |        | 35      |        | 55      |        | 60      | ns   |

| t <sub>OH</sub> (2) |             | from Addresses, CE<br>ge-Whichever is First | 0      |         | 0      |         | 0      |         | 0      |         | ns   |

#### NOTES:

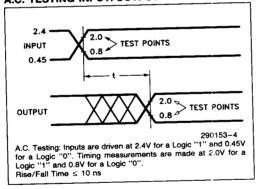

1. A.C. characteristics tested at  $V_{IH}=2.4V$  and  $V_{IL}=0.45V$ . Timing measurements made at  $V_{OH}=2.0V$  and  $V_{OL}=0.8V$ .

2. Guaranteed and sampled.

Figure 3. A.C. Waveforms 27F64

CAPACITANCE(1) TA = 25°C, f = 1.0 MHz

| APACHANU        | E(1) 1A = 25 0,1 = 1.0 VII 12 | Τ        | T    | Ornditions     |

|-----------------|-------------------------------|----------|------|----------------|

| Symbol          | Parameter                     | Max      | Unit | Conditions     |

| C <sub>IN</sub> | Address/Control Capacitance   | 6        | pF   | $V_{IN} = 0V$  |

|                 | Output Capacitance            | 12       | pF   | $V_{OUT} = 0V$ |

| Cout            | Output Capacitation           | <u> </u> |      |                |

#### NOTE:

1. Sampled. Not 100% tested.

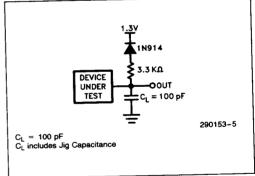

## A.C. TESTING INPUT/OUTPUT WAVEFORM

### A.C. TESTING LOAD CIRCUIT

### **CONVENTIONAL OPERATION**

### PROGRAM MODE

Caution: Exceeding 14V on  $V_{PP}$  will permanently damage the device.

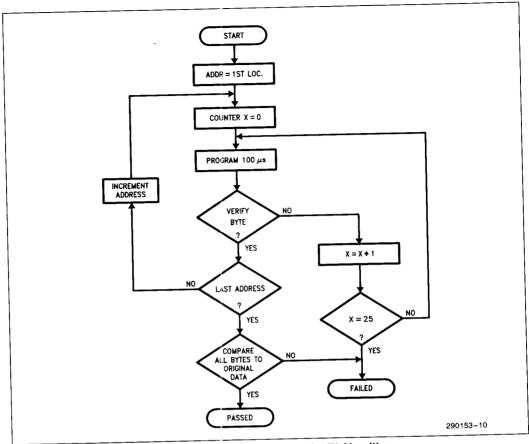

In the conventional program mode, the 27F64 operates like the P2764A and the 27C64 EPROMs. The Quick-Pulse Programming algorithm enables one second programming of the entire flash array. (See Figure 8. Quick Pulse Programming Algorithm.)

Erasure removes charge from the flash memory memory cells leaving the array in the logic high state (0FFH). Programming injects charge onto the floating gate, changing selected cell data to the low state. Data bytes can include both unaltered erased state and programmed state bits.

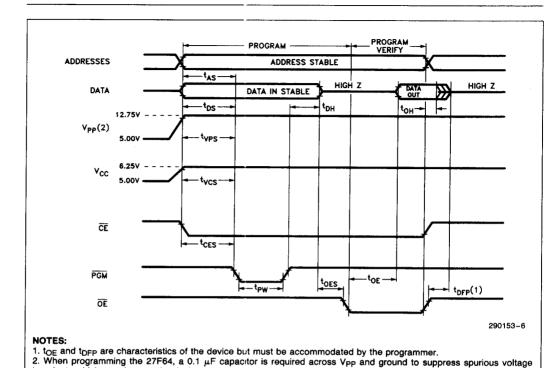

The method by which you enter the 27F64 into the programming mode is as follows: raise  $V_{CC}$  to 6.25V, raise  $V_{PC}$  to 12.75V, lower  $\overline{CE}$  to  $V_{IL}$ , and select the desired address. While applying eight bits of data in parallel to the device's inputs, toggle  $\overline{PGM}$  low to program the byte. (See Figure 4. Conventional Programming/Verify Waveforms.)

### PROGRAM VERIFY MODE

Setting V<sub>PP</sub> to 12.75V, V<sub>CC</sub> to 6.25V, PGM to V<sub>IH</sub>, CE and OE to V<sub>IL</sub>, places the device in the program verify mode. V<sub>CC</sub> provides an elevated reference level which guarantees a minimum of ten years' data retention in the normal read mode.

The Quick-Pulse Programming algorithm (Figure 8) requires a final array verify after the completion of byte programming. The system should verify the entire array with  $V_{CC}$  and  $V_{PP}$  at 6V.

### QUICK-ERASETM MODE

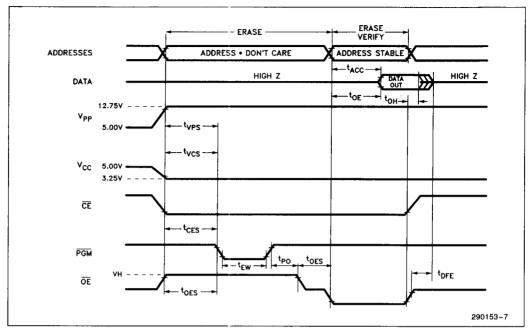

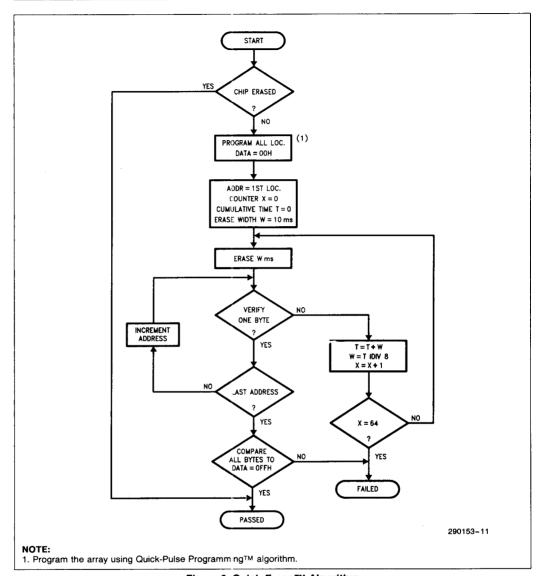

The Quick-Erase mode of the 27F64 eliminates the requirement of U.V. light for device erasure. Electrical erasure removes charge from all bits of the array in parallel, via Fowler-Nordheim tunneling. 1 The Quick-Erase algorithm controls the electrical erasure and verification sequence. (See Figure 9. Quick-Erase algorithm.)

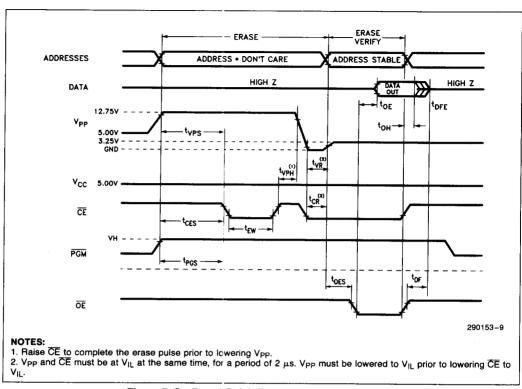

Enter the device into the Quick-Erase mode by lowering  $V_{CC}$  to 3.25V, raising  $V_{PP}$  and  $\overline{OE}$  to 12.75V, and setting  $\overline{CE}$  to  $V_{IL}$ . Toggling  $\overline{PGM}$  low controls the erase pulse width. (See Figure 5. Conventional Quick-Erase/Verify Waveforms.)

### **ERASE VERIFY MODE**

After returning  $\overline{PGM}$  to a logic "1" level in the Quick-Erase mode, change  $\overline{OE}$  from a high voltage level (12.75V) to V<sub>IL</sub> to select the erase verify mode. Sequentially verify each address in the array for valid erased data (0FFH). V<sub>CC</sub> at 3.25V provides the erased reference level for the flash memory cell. Verification at this level guarantees ten years of data integrity for normal read mode operation.

Once all bytes in the array verify, the algorithm returns the device to the read mode, and performs a final erase verify at  $V_{CC} = 5V$ .

## PROGRAM AND ERASE INHIBIT MODE

With Vpp and V<sub>CC</sub> at 5V, the 27F64 effectively bars spurious programming and erasure of the flash memory array. Other ways to control the program or erase modes include maintaining  $\overline{PGM}$  or  $\overline{CE}$  at a V<sub>IH</sub> logic level.

### inteligent Identifier™ MODE

The inteligent Identifier mode outputs the manufacturer code (89H) and device code (03H). Programming equipment automatically matches a device with its proper algorithms.

With  $\overline{PGM}$  at  $V_{IH}$ ,  $\overline{CE}$  and  $\overline{OE}$  active low, and  $A_1$  through  $A_{12}$  at  $V_{IL}$ , raising  $A_9$  to a high voltage level (11.5V-13V) activates the integrated Identifier mode. Byte 0 ( $A_0 = V_{IL}$ ) represents the manufacturer's code, and byte 1 ( $A_0 = V_{IH}$ ) represents the device identifier.

### REFERENCE

1. R. Williams, Phys. Rev., Vol. 140, p. 569, 1965.

## Table 5. Conventional Programming/Verify Operation

## D.C. CHARACTERISTICS TA = 25°C ±15°C

|                  | THE THE THE TENT OF THE TENT O |      | Limits                | Test Conditions |                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|-----------------|--------------------------------|

| Symbol           | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Min  | Max                   | Unit            | (Note 1)                       |

| lu               | Input Leakage Current (All Inputs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | ±1.0                  | μΑ              | $V_{IN} = V_{CC}$ or GND(7)    |

| V <sub>IL</sub>  | Input Low Level (All Inputs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -0.5 | 0.8                   | ٧               |                                |

| VIH              | Input High Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.0  | V <sub>CC</sub> + 0.5 | V               |                                |

| Vol              | Output Low Voltage During Verify                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 0.45                  | V               | I <sub>OL</sub> = 2.1 mA       |

| VoH              | Output High Voltage During Verify                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.5  |                       | V               | $I_{OH} = -2.5 \mathrm{mA}$    |

| ICC2             | V <sub>CC</sub> Programming Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 30                    | mA              | $\overline{CE} = V_{IL}(3, 6)$ |

| I <sub>PP2</sub> | V <sub>PP</sub> Programming Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 30                    | mA              | $\overline{CE} = V_{IL}(3, 6)$ |

| V <sub>H</sub>   | High Voltage Detect Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11.5 | 13.0                  | V               | (Notes 4, 5)                   |

| V <sub>PP2</sub> | V <sub>PP</sub> Program/Verify Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12.5 | 13.0                  | V               | $\overline{CE} = V_{IL}(6)$    |

| V <sub>CC2</sub> | V <sub>CC</sub> Program/Verify Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6.0  | 6.5                   | V               | $\overline{CE} = V_{IL}(6)$    |

## A.C. CHARACTERISTICS T<sub>A</sub> = 25°C ± 15°C

|                  | CIERISTICS TA - 20 0 1 10 0                                  |     | Lin      | Test Conditions |      |              |

|------------------|--------------------------------------------------------------|-----|----------|-----------------|------|--------------|

| Symbol           | Parameter                                                    | Min | Тур      | Max             | Unit | (Note 1)     |

| t <sub>AS</sub>  | Address Setup Time                                           | 2   |          |                 | μs   |              |

| toes             | OE Setup Time                                                | 2   |          |                 | μs   |              |

| t <sub>DS</sub>  | Data Setup Time                                              | 2   |          |                 | μs   |              |

| t <sub>ОН</sub>  | Output Hold from Address, CE or OE, whichever Occurred First | 0   |          |                 | μs   |              |

| t <sub>DH</sub>  | Data Hold Time                                               | 2   | <u> </u> |                 | μs   |              |

| topp             | OE High to Output Float Delay                                | 0   |          | 130             | ns   | (Note 2)     |

| typs             | V <sub>PP</sub> Setup Time                                   | 2   |          |                 | μs   |              |

| tycs             | V <sub>CC</sub> Setup Time                                   | 2   |          |                 | μs   | <u> </u>     |

| t <sub>CES</sub> | CE Setup Time                                                | 2   |          |                 | μs   | ļ            |

| tpw              | Program Pulse Width                                          | 95  | 100      | 105             | μs   | Quick-Pulse™ |

| toE              | OE to Output Delay                                           |     |          | 150             | ns   |              |

### A.C. CONDITIONS OF TEST

| Input Rise and Fall Times (10% to 90%) 10 ns | Input Timing Reference Level0.8V and 2.0V |

|----------------------------------------------|-------------------------------------------|

| Input hise and tall times (10 to 10 to 1)    | - · · · · · · · · · · · · · · · · · · ·   |

| Input Pulse Levels 0.45V to 2.4V             | Output Filling Flororonous activities     |

- 1. V<sub>CC</sub> must be applied to the 27F64 before V<sub>PP</sub> and removed from the device after V<sub>PP</sub>.

- 2. This parameter is only sampled and is not 100% tested. Output Float is defined as the point where data is no longer driven-see timing diagram.

- 3. The maximum current value is with the outputs unloaded during vertication.

- 4. V<sub>H</sub> is the third logic level. The range of V<sub>H</sub> encompasses the traditional 11.5V-12.5V, as well as the Quick-Pulse Programming V<sub>PP</sub> range 12.5V-13.0V.

- 5. Forcing V<sub>H</sub> on pin A9 and the proper levels on the control pins puts the device into the int<sub>B</sub>ligent Identifier mode.

6. This specification applies to both programming and verification. See timing waveforms for PGM and OE test conditions.

- 7. During program verify, the output leakage current  $I_{LO}=\pm 10~\mu A$  maximum.  $V_{OUT}=V_{CC}$  or GND.

transients which can damage the device.

Figure 4. Conventional Programming/Program Verify Waveforms

## Table 6. Conventional Quick-Erase™/Verify Operation

## D.C. CHARACTERISTICS $T_A = 25^{\circ}C \pm 15^{\circ}C$

|                  |                                      | 1     | Limits                | Unit | Test Conditions                                             |  |

|------------------|--------------------------------------|-------|-----------------------|------|-------------------------------------------------------------|--|

| Symbol           | Parameter                            | Min   | Max                   |      |                                                             |  |

| 1 <sub>L1</sub>  | Input Leakage Current                |       | ±1.0                  | μΑ   | $V_{IN} = V_{CC} \text{ or } GND^{(7)}$                     |  |

| VIL              | Input Low Voltage                    | - 0.5 | 0.8                   | V    | (Note 1)                                                    |  |

| VIH              | Input High Voltage                   | 2.0   | V <sub>CC</sub> + 0.5 | V    | (Note 1)                                                    |  |

| V <sub>OL</sub>  | Output Low Voltage                   |       | 0.45                  | V    | I <sub>OL</sub> = 1.6 mA                                    |  |

| Voh              | Output High Voltage                  | 2.4   | Vcc                   | V    | $I_{OH} = -400 \mu\text{A} \text{ at V}_{OH} \text{ (min)}$ |  |

| Іссз             | V <sub>CC</sub> Erase Current        |       | 10                    | mA   | $\overline{CE} = V_{IL}(5, 6)$                              |  |

| I <sub>PP3</sub> | V <sub>PP</sub> Erase/Verify Current |       | 10                    | mA   | CE = V <sub>IL</sub>                                        |  |

| V <sub>CC3</sub> | V <sub>CC</sub> Erase/Verify Supply  | 3.0   | 3.50                  | V    | $\overline{CE} = V_{IL}^{(6)}$                              |  |

| V <sub>PP3</sub> | V <sub>PP</sub> Erase/Verify Supply  | 12.5  | 13.0                  | V    | $\overline{CE} = V_{IL}^{(6)}$                              |  |

### A.C. CHARACTERISTICS TA = 25°C ±15°C

|                  | D                                                               | Liı | nits | Unit | Test Conditions           |

|------------------|-----------------------------------------------------------------|-----|------|------|---------------------------|

| Symbol           | Parameter                                                       | Min | Max  |      |                           |

| t <sub>VPS</sub> | V <sub>PP</sub> Setup Time                                      | 2   |      | μs   | (Note 2)                  |

| tvcs             | V <sub>CC</sub> Setup Time                                      | 2   |      | μs   | (Note 2)                  |

| tces             | CE Setup Time                                                   | 2   |      | μs   |                           |

| tew              | Erase Pulse Width                                               | 1   | 1855 | ms   | (Note 3)                  |

| toes             | OE Setup Time                                                   | 2   |      | μs   |                           |

| t <sub>PO</sub>  | OE to V <sub>IH</sub> from PGM Hi                               | 11  |      | μs   |                           |

| tACC             | Address to Output Delay                                         | 2   |      | μs   | CE = OE = V <sub>IL</sub> |

| toE              | OE to Output Delay                                              | 2   |      | μs   | CE = V <sub>IL</sub>      |

| t <sub>OH</sub>  | Output Hold from Address, CE<br>or OE, Whichever Occurred First | 0   |      | ns   |                           |

| t <sub>DFE</sub> | OE High to Output<br>Float Delay                                | 0   | 130  | ns   | (Note 4)                  |

### A.C. CONDITIONS OF TEST

|                                    | Input Timing Reference Level0.8V and 2.0V |

|------------------------------------|-------------------------------------------|

|                                    |                                           |

| Input Pulse Levels 0.45 V to 2.4 V | Output Timing Hererence Level             |

- 1. Minimum D.C. input voltage is -0.5V. During transitions, the inputs may undershoot to -2.0V for periods less than 20 ns. Maximum D.C. voltage on output pins is V<sub>CC</sub> + 0.5V, which may overshoot to V<sub>CC</sub> + 2V for periods less than 20 ns.

- 2. V<sub>CC</sub> must be applied to the 27F64 before V<sub>PP</sub> and removed from the device after V<sub>PP</sub>.

- 3. Erase pulse width varies with pulse number. (See Quick-Erase Algorithm.)

- 4. This parameter is only sampled and not 100% tested.

- 5. The maximum current value is with the outputs unloaded during verification.

- 6. This specification applies to both erasure and verification. See timing waveforms for PGM and OE test conditions.

- 7. During erase verify, the output leakage current  $I_{LO} = \pm 10~\mu A$  maximum.  $V_{OUT} = V_{CC}$  or GND.

Figure 5. Conventional Quick-Erase™/Verify Waveforms

### ON-BOARD OPERATION

Board level designers and manufacturers prefer to delay EPROM programming until the last possible moment. Benefits include the ability to change code between testing and end-of-line configuration, inventory control, and reduced costs. Efficient algorithms, such as Intel's Quick-Pulse Programming algorithm, enable EPROM programming to take place during the board assembly process, or afterwards with the EPROM in-circuit.

Intel's 27F64 flash memory simplifies in-module programming\* by offering designers the On-Board modes. These modes transfer the non-TTL voltages to pins generally unused in EPROM-based system design: PGM and VPP. VCC maintains 5.0V throughout all operations. Internal circuitry derives the erase and program reference levels from Vpp instead of from V<sub>CC</sub>. Since systems rarely connect PGM to a common bus with other types of memory, the On-Board modes select certain features with PGM at V<sub>H</sub> rather than OE at V<sub>H</sub>. A similar argument holds for specifying a new inteligent Identifier mode that maintains A<sub>9</sub> at TTL logic levels.

### Differences in mode implementation have been highlighted in Table 7 for your convenience.

\*A few issues arise from programming EPROMs onboard. EPROMs should be programmed and verified at an elevated V<sub>CC</sub> to insure proper cell margins and long term data retention. PROM programmers can accommodate this V<sub>CC</sub> voltage easily; however, other logic devices populating the board might not operate predictably. One solution to this problem involves running separate V<sub>CC</sub> traces to the edge connector. The 3.25V V<sub>CC</sub> level needed for the conventional Quick-Erase algorithm poses similar problems. Specifying  $A_9$  at a  $V_H$  level to read the inteligent Identifier, and  $\overline{OE}$  at  $V_H$  to erase, forces the board designer to add extra buffering and isolation circuitry.

Table 7. On-Board Mode Selection

| Pins                        | CE                  | ŌĒ              | PGM             | A <sub>9</sub>      | A <sub>0</sub>      | V <sub>PP</sub>                | Vcc  | Outputs          |

|-----------------------------|---------------------|-----------------|-----------------|---------------------|---------------------|--------------------------------|------|------------------|

| Mode                        |                     |                 |                 |                     |                     |                                |      |                  |

| Read                        | V <sub>IL</sub>     | VIL             | V <sub>IH</sub> | X(1)                | X                   | Vcc                            | 5.0V | D <sub>OUT</sub> |

| Output Disable              | VIL                 | VIH             | V <sub>IH</sub> | ×                   | X                   | V <sub>CC</sub>                | 5.0V | High Z           |

| Standby                     | VIH                 | X               | Х               | Х                   | Х                   | Vcc                            | 5.0V | High Z           |

| Program/Erase Inhibit       | X                   | X               | Х               | Х                   | Х                   | V <sub>CC</sub> <sup>(4)</sup> | 5.0V |                  |

| Program                     | VIL                 | VIH             | VIL             | Х                   | Х                   | 12.75V                         | 5.0V | D <sub>IN</sub>  |

| Program Verify              | VIL                 | VIL             | VH(2)           | Х                   | Х                   | 6.25V                          | 5.0V | D <sub>OUT</sub> |

| Quick-Erase                 | V <sub>IL</sub> (5) | VIH             | VH              | Х                   | Х                   | 12.75V                         | 5.0V | High Z           |

| Erase Verify                | VIL                 | VIL             | VH              | Х                   | X                   | 3.25V                          | 5,0V | D <sub>OUT</sub> |

| Inteligent ID™ Manufacturer | VIL                 | VIL             | VIL             | V <sub>IL</sub> (3) | V <sub>IL</sub> (3) | Vcc                            | 5.0V | 89H              |

| Inteligent ID™ Device       | VIL                 | V <sub>IL</sub> | VIL             | Λ <sup>IΓ</sup> (3) | V <sub>IH</sub> (3) | V <sub>CC</sub>                | 5.0V | 03H              |

- 1. X can be VIL or VIH-

- 2.  $11.5 \le V_H \le 13.0V$ .

- 3.  $A_1 A_{12} = V_{IL}$ .

- 4. With  $\dot{V}_{PP} \leq \dot{V}_{CC}$  the 27F64 inhibits all erase and program functions.

- CE controls the erase pulse width.

## SIMILARITIES TO CONVENTIONAL MODES

The On-Board read, output disable, standby, and program/erase inhibit modes all operate identically to the conventional equivalent modes. See appropriate conventional mode sections for descriptions and details.

### PROGRAM MODE

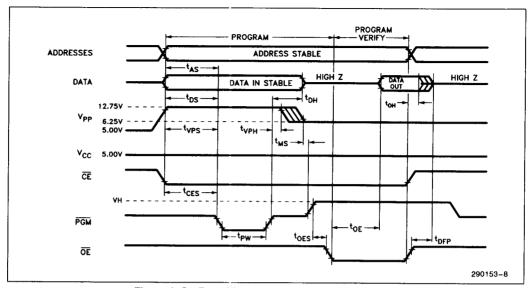

With the exception of  $V_{CC}$  specified at 5V, the On-Board program mode functions exactly like its standard EPROM counterpart. Programming with  $V_{CC}$  at 5V eliminates the need for dual  $V_{CC}$  power buses for in-circuit programming. Users of On-Board programming still enjoy all the benefits attributed to Intel's Quick-Pulse Programming algorithm. (See Figure 8. Quick-Pulse Programming Algorithm, and Figure 6. On-Board Programming/Verify Waveforms.)

### **PROGRAM VERIFY MODE**

After completing each program pulse ( $\overline{PGM}$  transition from logic 0 to 1), lower V<sub>PP</sub> to 6.25V, raise  $\overline{PGM}$  to V<sub>H</sub> level (11.5V-13.0V), and set  $\overline{OE}$  to V<sub>IL</sub> to enter the program verify mode. Invalid data indicates the need for another program pulse; lower  $\overline{PGM}$  from V<sub>H</sub> to V<sub>IH</sub> prior to raising V<sub>PP</sub> to 12.75V. Valid data indicates completion of the programming loop.

The Quick-Pulse Programming algorithm (Figure 8) requires a final array verify after completion of byte programming. The system should verify the entire array with V<sub>PP</sub> at 6V, and  $\overline{PGM}$  at V<sub>H</sub>.

### QUICK-ERASETM MODE

To select the Quick-Erase mode, set  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  to V<sub>IH</sub>, V<sub>C</sub> to 5.0V, V<sub>PP</sub> to 12.75V, and  $\overline{\text{PGM}}$  to V<sub>H</sub> (11.5V-13.0V). Toggle  $\overline{\text{CE}}$  low for the predetermined erase pulse width. Note that  $\overline{\text{CE}}$  controls the erase time in the On-Board mode, not  $\overline{\text{PGM}}$ . (See Figure 7. On-Board Erase/Verify Waveforms and Figure 9. Quick-Erase Algorithm.)

#### **ERASE VERIFY MODE**

To transition from Quick-Erase to erase verify mode, raise  $\overline{CE}$  to  $V_{IH}$  for 1  $\mu$ s, then lower  $V_{PP}$  below 2V, and  $\overline{CE}$  to  $V_{IL}$  for 2  $\mu$ s. Raise  $V_{PP}$  to the 3.25V erase verify level, place the address to be verified on the bus, and gate the data from the device outputs by lowering  $\overline{OE}$  to  $V_{IL}$ . Continue checking through the array until an address does not verify, and then raise  $\overline{CE}$  to  $V_{IH}$  to set up for the next erase pulse.

### inteligent Identifier MODE

Board programmers can read the On-Board int<sub>0</sub>ligent Identifier<sup>TM</sup> by setting V<sub>CC</sub> and V<sub>PP</sub> to 5.0V, A<sub>1</sub>-A<sub>12</sub> to V<sub>IL</sub>, and  $\overline{\text{CE}}$ ,  $\overline{\text{OE}}$ , and  $\overline{\text{PGM}}$  to V<sub>IL</sub>. Byte 0 (A<sub>0</sub> = V<sub>IL</sub>) represents the manufacturer's code (89H) and byte 1 (A<sub>0</sub> = V<sub>IH</sub>) represents the device identifier (03H).

## Table 8. On-Board Program/Program Verify Operation

## D.C. CHARACTERISTICS $T_A = 25^{\circ}C \pm 15^{\circ}C$ (Notes 1, 2)

| Symbol                               | Parameter                              | Lim  | nits | Unit | Test Conditions                      |

|--------------------------------------|----------------------------------------|------|------|------|--------------------------------------|

|                                      |                                        | Min  | Max  |      |                                      |

| I <sub>CC4</sub>                     | V <sub>CC</sub> Program/Verify Current |      | 30   | mA   | $\overline{CE} = V_{IL}^{(4, 5, 6)}$ |

| Ipp4                                 | V <sub>PP</sub> Program/Verify Current |      | 30   | mA   | $\overline{CE} = V_{IL}^{(4, 5, 6)}$ |

| V <sub>CC4</sub>                     | V <sub>CC</sub> Program/Verify Supply  | 4.50 | 5.50 | V    | $\overline{CE} = V_{IL}^{(5, 6)}$    |

| V <sub>CC4</sub><br>V <sub>PP4</sub> | V <sub>PP</sub> Program Supply         | 12.5 | 13.0 | V    | CE = V <sub>IL</sub> (6)             |

| VPP4<br>VPPV4                        | V <sub>PP</sub> Verify Supply          | 6.0  | 6.5  | . V  | CE = V <sub>IL</sub> (6)             |

### A.C. CHARACTERISTICS TA = 25°C ±15°C

| Symbol           | Parameter                                                          | Lin | nits | Unit | Test Conditions      |

|------------------|--------------------------------------------------------------------|-----|------|------|----------------------|

|                  |                                                                    | Min | Max  |      |                      |

| tas              | Address Setup Time                                                 | 2   |      | μs   |                      |

| t <sub>DS</sub>  | Data Setup Time                                                    | 2   |      | μs   |                      |

| t <sub>VPS</sub> | V <sub>PP</sub> Setup Time                                         | 2   |      | μs   |                      |

| tCES             | CE Setup Time                                                      | 2   |      | μs   |                      |

| tpw              | Program Pulse Width                                                | 95  | 105  | μs   |                      |

| <sup>t</sup> DH  | Data Hold Time                                                     | 2   |      | μs   |                      |

| t <sub>VPH</sub> | V <sub>PP</sub> Hold Time from PGM = V <sub>IH</sub>               | 0   |      | μs   |                      |

| t <sub>MS</sub>  | Margin Setup Time                                                  | 0   |      | μs   |                      |

| toes             | OE Setup Time                                                      | 2   |      | μs   |                      |

| toE              | OE to Output Delay                                                 |     | 150  | ns   | CE = V <sub>IL</sub> |

| t <sub>OH</sub>  | Output Hold from Address, CE<br>or OE, Whichever Occurred<br>First | 0   |      |      |                      |

| tDFP             | OE High to Output Float Delay                                      | 0   | 130  | ns   | (Note 3)             |

### A.C. CONDITIONS OF TEST

Input Timing Reference Level ......0.8V and 2.0V Output Timing Reference Level . . . . . 0.8V and 2.0V

Input Rise and Fall Times (10% to 90%) . . . . . 10 ns

#### NOTES:

1.  $V_{CC}$  must be applied to the 27F64 before  $V_{PP}$  and removed from the device after  $V_{PP}$ .

2. See Conventional and On-Board Read Operation D.C. Characteristics tables for I<sub>LI</sub>, I<sub>LO</sub>, V<sub>IL</sub>, V<sub>IH</sub>, V<sub>OL</sub> and V<sub>OH</sub> values.

3. This parameter is only sampled and is not 100% tested. Output Float is defined as the point where data is no longer driven.

4. The maximum current value is with the outputs unloaded during verification.

5. This specification applies to both programming and verification.6. See timing waveforms for PGM and OE test conditions.

Figure 6. On-Board Programming/Verify Waveforms

## Table 9. On-Board Quick-Erase™/Erase Verify Operation

## D.C. CHARACTERISTICS T<sub>A</sub> = 25°C ±15°C (Notes 1, 2)

| Symbol                               |                                      | Limits |      | Unit | Test Conditions                   |

|--------------------------------------|--------------------------------------|--------|------|------|-----------------------------------|

|                                      | Parameter                            | Min    | Max  |      |                                   |

|                                      | V <sub>CC</sub> Erase Current        |        | 10   | mA   | $\overline{CE} = V_{IL}^{(5, 7)}$ |

| ICC5                                 | V <sub>CC</sub> Erase/Verify Current |        | 30   | mA   | $\overline{CE} = V_{IL}^{(5, 7)}$ |

| CCV5                                 | V <sub>PP</sub> Erase/Verify Current |        | 10   | mA   | $\overline{CE} = V_{IL}(5, 6, 7)$ |

| V <sub>CC5</sub>                     | V <sub>CC</sub> Erase/Verify Supply  | 4.50   | 5.50 | V    | $\overline{CE} = V_{IL}^{(6, 7)}$ |

| V <sub>CC5</sub><br>V <sub>PP5</sub> | V <sub>PP</sub> Erase Supply         | 12.5   | 13.0 | V    | $\overline{CE} = V_{IL}^{(7)}$    |

| V <sub>PPV5</sub>                    | V <sub>PP</sub> Verify Supply        | 3.0    | 3.50 | ٧    | $\overline{CE} = V_{1L}^{(7)}$    |

## A.C. CHARACTERISTICS $T_A = 25^{\circ}C \pm 15^{\circ}C$

| Symbol           | Parameter                                                             | Lir | nits | Unit | Test Conditions      |

|------------------|-----------------------------------------------------------------------|-----|------|------|----------------------|

|                  |                                                                       | Min | Max  |      |                      |

| t <sub>VPS</sub> | V <sub>PP</sub> Setup Time                                            | 2   |      | μs   |                      |

| tces             | CE Setup Time                                                         | 2   |      | μs   |                      |

| tegs             | PGM Setup Time                                                        | 2   |      | μs   |                      |

| tew              | Erase Pulse Width                                                     | 1   | 1855 | ms   | (Notes 3, 8)         |

| t <sub>VPH</sub> | V <sub>PP</sub> Hold Time from $\overline{\text{CE}} = V_{\text{IH}}$ | 1   |      | μs   |                      |

| t <sub>VR</sub>  | V <sub>PP</sub> Recovery Time                                         | 2   |      | μs   |                      |

| tcr              | CE Recovery Time                                                      | 2   |      | μs   |                      |

| toes             | OE Setup Time                                                         | 2   |      | μs   |                      |

| toE              | OE to Output Delay                                                    | 150 |      | ns   | CE = V <sub>IL</sub> |

| ф                | Output Hold from Address CE<br>or OE, Whichever Occurred<br>First     | 0   |      |      |                      |

| tDFE             | OE High to Output Float Delay                                         | 0   | 130  | ns   | (Note 4)             |

### A.C. CONDITIONS OF TEST

| Aloi Collection                              |                                             |

|----------------------------------------------|---------------------------------------------|

| Input Rise and Fall Times (10% to 90%) 10 ns | Input Timing Reference Level0.8V and 2.0V   |

| input Rise and Fair Times (10 % to 50 %)     | O 8V and 2 OV                               |

| Input Pulse Levels 0.45V to 2.4V             | Output Timing Reference Level 0.8V and 2.0V |

- 1.  $V_{CC}$  must be applied to the 27F64 before  $V_{PP}$  and removed from the device after  $V_{PP}$ .

- 2. See conventional and On-Board Read Operation D.C. Characteristics for I<sub>LI</sub>, I<sub>LO</sub>, V<sub>IL</sub>, V<sub>IH</sub>, V<sub>OL</sub> and V<sub>OH</sub> values.

- 3. Erase pulse width varies with pulse number. (See Quick-Erase algorithm.)