Data Sheet June 2003 FN2766.6

# 80MHz, High Slew Rate, High Output Current, Video Operational Amplifier

The HA-2842 is a wideband, high slew rate, operational amplifier featuring an outstanding combination of speed, bandwidth, and output drive capability. This amplifier's performance is further enhanced through stable operation down to closed loop gains of +2, the inclusion of offset null controls, and by its excellent video performance.

The capabilities of the HA-2842 are ideally suited for high speed cable driver circuits, where low closed loop gains and high output drive are required. With a 6MHz full power bandwidth, this amplifier is well suited for high frequency signal conditioning circuits and video amplifiers. Gain flatness of 0.035dB, combined with differential gain and phase specifications of 0.02%, and 0.03 degrees, respectively, make the HA-2842 ideal for component and composite video applications.

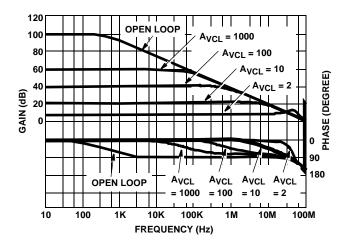

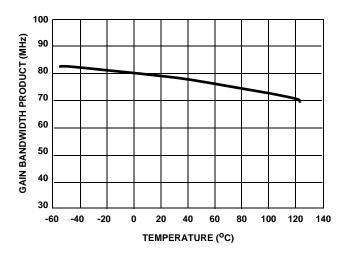

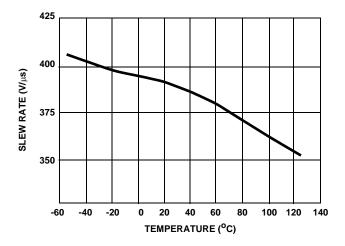

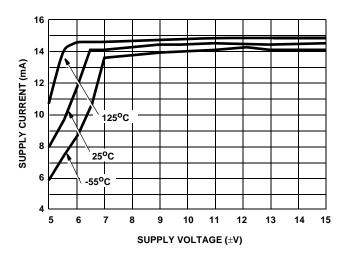

A zener/nichrome based reference circuit, coupled with advanced laser trimming techniques, yields a supply current with a low temperature coefficient and low lot-to-lot variability. For example, the average  $I_{CC}$  variation from  $85^{\circ}C$  to  $-40^{\circ}C$  is  $<\!600\mu A$  ( $\pm2\%$ ), while the standard deviation of the  $I_{CC}$  distribution is  $<\!0.1\text{mA}$  (0.8%) at  $25^{\circ}C$ . Tighter  $I_{CC}$  control translates to more consistent AC parameters ensuring that units from each lot perform the same way, and easing the task of designing systems for wide temperature ranges. Critical AC parameters, Slew Rate and Bandwidth, each vary by less than  $\pm5\%$  over the industrial temperature range (see Typical Performance Curves)

## Ordering Information.

| PART NUMBER             | TEMP.      | PACKAGE   | PKG.  |

|-------------------------|------------|-----------|-------|

| (BRAND)                 | RANGE (°C) |           | DWG.# |

| HA9P2842-5<br>(H2842F5) | 0 to 75    | 8 Ld SOIC | M8.15 |

#### **Features**

- · Stable at Gains of 2 or Greater

- · Low AC Variability Over Process and Temperature

- a Lligh Output Current (Min)

- Differential Gain/Phase . . . . . . . 0.02%/0.03 Degrees

- Enhanced Replacement for AD842

## **Applications**

- · Pulse and Video Amplifiers

- Wideband Amplifiers

- · Coaxial Cable Drivers

- Fast Sample-Hold Circuits

- · High Frequency Signal Conditioning Circuits

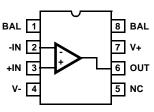

## **Pinout**

#### **Absolute Maximum Ratings**

| Voltage Between V+ and V- Terminals | 35V   |

|-------------------------------------|-------|

| Differential Input Voltage          | . 6V  |

| Output Current (Notes 3, 4)         | 5mA   |

| 100mA (50% Duty C                   | ycle) |

## **Operating Conditions**

| Temperature Range                |               |

|----------------------------------|---------------|

| HA-2842-5                        | 0°C to 75°C   |

| Recommended Supply Voltage Range | ±6.5V to ±15V |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 2)                | $\theta_{JA}$ (°C/W)  |

|-----------------------------------------------------|-----------------------|

| 8 Lead SOIC Package                                 | 160                   |

| Maximum Junction Temperature (Die)                  | 175 <sup>0</sup> C    |

| Maximum Junction Temperature (Plastic Package, Note | 1) 150 <sup>o</sup> C |

| Maximum Storage Temperature Range6                  | 65°C to 150°C         |

| Maximum Lead Temperature (Soldering 10s)            | 300°C                 |

| (Lead Tips Only)                                    |                       |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- Maximum power dissipation, including output load, must be designed to maintain the maximum junction temperature below 150°C for plastic packages. By using Application Note AN556 on Safe Operating Area equations, along with the packaging thermal resistances listed in the Thermal Information section, proper load conditions can be determined.

- 2.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

- 3. V<sub>O</sub> = ±5V, R<sub>L</sub> Unconnected, Duty cycle ≤ 50%. For information about using high output current amplifiers, please refer to Application Note AN556 (Thermal Safe-Operating-Areas For High Current Op Amps), and the "Power Dissipation Considerations" section in the "Application Information" section of this datasheet.

- 4. Maximum continuous (100% Duty Cycle) output current is 50mA. For currents >50mA, Duty Cycle must be derated accordingly.

## $\textbf{Electrical Specifications} \qquad \text{V}_{SUPPLY} = \pm 15 \text{V}, \ \text{R}_L = 1 \text{k}\Omega, \ \text{C}_L \leq 10 \text{pF}, \ \text{Unless Otherwise Specified}$

|                                       |                                     | TEMP (°C) | HA-2842-5 |        |     |                    |

|---------------------------------------|-------------------------------------|-----------|-----------|--------|-----|--------------------|

| PARAMETER                             | TEST CONDITIONS                     |           | MIN       | TYP    | MAX | UNITS              |

| INPUT CHARACTERISTICS                 |                                     |           |           |        |     |                    |

| Offset Voltage (Note 10)              |                                     | 25        | -         | 1      | 3   | mV                 |

|                                       |                                     | Full      | -         | -      | 6   | mV                 |

| Average Offset Voltage Drift          |                                     | Full      | -         | 13     | -   | μV/ <sup>o</sup> C |

| Bias Current (Note 10)                |                                     | 25        | -         | 5      | 10  | μА                 |

|                                       |                                     | Full      | -         | -      | 15  | μА                 |

| Average Bias Current Drift            |                                     | Full      | -         | 20     | -   | nA/ <sup>o</sup> C |

| Offset Current                        |                                     | 25        | -         | 0.5    | 1.0 | μА                 |

|                                       |                                     | Full      | -         | -      | 1.5 | μА                 |

| Average Offset Current Drift          |                                     | Full      | -         | 1.3    | -   | nA/ <sup>o</sup> C |

| Input Resistance                      |                                     | 25        | -         | 170    | -   | kΩ                 |

| Input Capacitance                     |                                     | 25        | -         | 1      | -   | pF                 |

| Common Mode Range                     |                                     | Full      | ±10       | -      | -   | V                  |

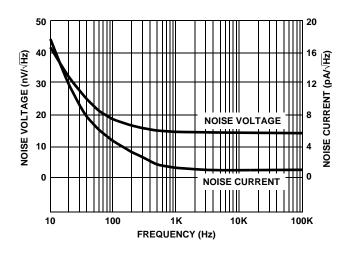

| Input Noise Voltage                   | 10Hz to 1MHz                        | 25        | -         | 16     | -   | μV <sub>RMS</sub>  |

| Input Noise Voltage Density           | $f = 1kHz, R_{SOURCE} = 0\Omega$    | 25        | -         | 16     | -   | nV∕√Hz             |

| Input Noise Current (Note 10)         | $f = 1kHz, R_{SOURCE} = 100k\Omega$ | 25        | -         | 2      | -   | pA/√Hz             |

| TRANSFER CHARACTERISTICS              |                                     |           |           |        |     | 1                  |

| Large Signal Voltage Gain             | V <sub>O</sub> = ±10V               | 25        | 50        | 100    | -   | kV/V               |

|                                       |                                     | Full      | 30        | 60     | i   | kV/V               |

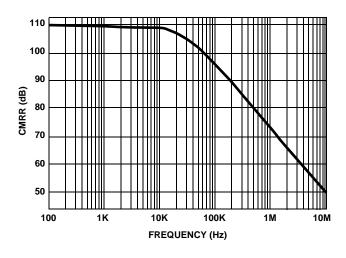

| Common-Mode Rejection Ratio (Note 10) | V <sub>CM</sub> = ±10V              | Full      | 80        | 110    | -   | dB                 |

| Minimum Stable Gain                   |                                     | 25        | 2         | -      | -   | V/V                |

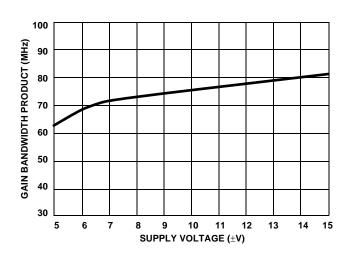

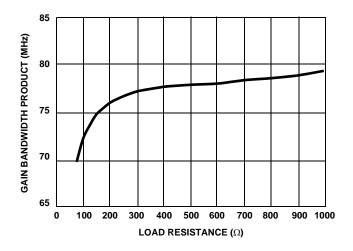

| Gain Bandwidth Product (Note 10)      | A <sub>VCL</sub> = 100              | 25        | -         | 80     | ,   | MHz                |

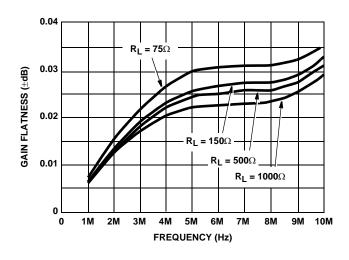

| Gain Flatness to 10MHz (Note 10)      | $R_L \ge 75\Omega$                  | 25        | -         | ±0.035 | -   | dB                 |

## $\textbf{Electrical Specifications} \qquad \text{$V_{SUPPLY}$ = $\pm 15$V, $R_L$ = $1$k$\Omega$, $C_L \le 10$pF, Unless Otherwise Specified} \qquad \textbf{(Continued)}$

|                                        |                                     |           | HA-2842-5 |      |     |         |

|----------------------------------------|-------------------------------------|-----------|-----------|------|-----|---------|

| PARAMETER                              | TEST CONDITIONS                     | TEMP (°C) | MIN       | TYP  | MAX | UNITS   |

| OUTPUT CHARACTERISTICS                 |                                     |           |           |      |     |         |

| Output Voltage Swing (Note, 10)        | V <sub>O</sub> = ± 10V              | Full      | ±10       | ±11  | -   | V       |

| Output Current (Note 10)               | (Note 3)                            | Full      | 100       | -    | -   | mA      |

| Output Resistance                      |                                     | 25        | -         | 8.5  | -   | Ω       |

| Full Power Bandwidth (Note 6)          | $V_O = \pm 10V$                     | 25        | 5.2       | 6    | -   | MHz     |

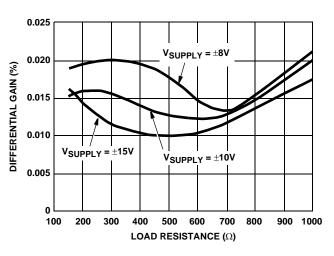

| Differential Gain (Note 10)            | (Note 5)                            | 25        | -         | 0.02 | -   | %       |

| Differential Phase (Note 10)           | (Note 5)                            | 25        | -         | 0.03 | -   | Degrees |

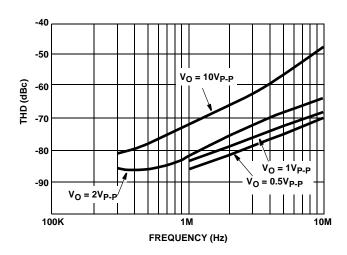

| Harmonic Distortion (Note 10)          | $V_O = 2V_{P-P}, f = 1MHz, A_V = 2$ | 25        | -         | >81  | -   | dBc     |

| TRANSIENT RESPONSE (Note 7)            |                                     |           |           |      |     |         |

| Rise Time                              |                                     | 25        | -         | 4    | -   | ns      |

| Overshoot                              |                                     | 25        | -         | 25   | -   | %       |

| Slew Rate (Notes 9, 10)                | A <sub>V</sub> = +2                 | 25        | 325       | 400  | -   | V/μs    |

| Settling Time                          | 10V Step to 0.1%                    | 25        | -         | 100  | -   | ns      |

| POWER REQUIREMENTS                     |                                     |           |           |      |     |         |

| Supply Current (Note 10)               |                                     | 25        | -         | 14.2 | -   | mA      |

|                                        |                                     | Full      | -         | 14.3 | 15  | mA      |

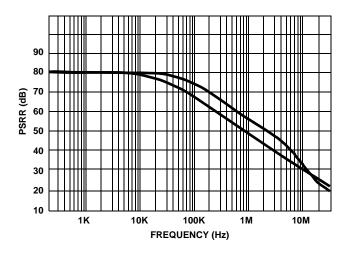

| Power Supply Rejection Ratio (Note 10) | (Note 8)                            | Full      | 70        | 80   | -   | dB      |

#### NOTES:

- 5. Differential gain and phase are measured with a VM700A video tester, using a NTC-7 composite VITS. R<sub>F</sub> = R<sub>1</sub> = 1kΩ, R<sub>L</sub> = 700Ω.

6. Full Power Bandwidth guaranteed based on slew rate measurement using FPBW = Slew Rate / 2πV PEAK ; V<sub>PEAK</sub> = 10V.

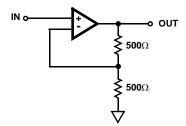

7. Pefor to Toot Circuits section of this data sheet

- 7. Refer to Test Circuits section of this data sheet.

- 8.  $V_{SUPPLY} = \pm 10V$  to  $\pm 20V$ .

- 9. This parameter is not tested. The limits are guaranteed based on lab characterization and reflect lot-to-lot variation.

- 10. See "Typical Performance Curves" for more information.

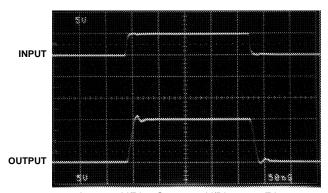

## **Test Circuits and Waveforms**

#### NOTES:

- 11.  $V_S = \pm 15V$ .

- 12.  $A_V = +2$ .

- $13. \ C_L \leq 10 pF$

#### **TEST CIRCUIT**

Input = 5V/Div., Output = 5V/Div., 50ns/Div.

# 188×0 INPUT OUTPUT 100+0

Input = 100 mV/Div., Output = 100 mV/Div., 50 ns/Div.

**SMALL SIGNAL RESPONSE**

#### LARGE SIGNAL RESPONSE

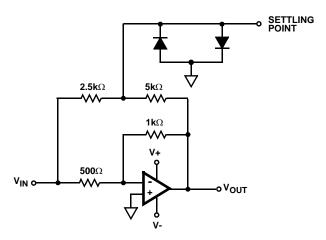

## NOTES:

- 14.  $A_V = -2$ .

- 15. Feedback and summing resistors must be matched (0.1%).

- 16. HP5082-2810 clipping diodes recommended.

- 17. Tektronix P6201 FET probe used at settling point.

- 18. For 0.01% settling time, heat sinking is suggested to reduce thermal effects and an analog ground plane with supply decoupling is suggested to minimize ground loop errors.

**SETTLING TIME TEST CIRCUIT**

SUGESTED OFFSET VOLTAGE ADJUSTMENT

## Application Information

The Intersil HA-2842 is a state of the art monolithic device which also approaches the "ALL-IN-ONE" amplifier concept. This device features an outstanding set of AC parameters augmented by excellent output drive capability providing for suitable application in both high speed and high output drive circuits.

Primarily intended to be used in balanced  $50\Omega$  and  $75\Omega$  coaxial cable systems as a driver, the HA-2842 could also be used as a power booster in audio systems as well as a power amp in power supply circuits. This device would also be suitable as a small DC motor driver.

### **Prototyping Guidelines**

For best overall performance in any application, it is recommended that high frequency layout techniques be used. This should include:

- 1. Mounting the device through a ground plane.

- 2. Connecting unused pins (NC) to the ground plane.

- Mounting feedback components on Teflon standoffs and/or locating these components as close to the device as possible.

- 4. Placing power supply decoupling capacitors from device supply pins to ground.

#### **Power Dissipation Considerations**

At high output currents, especially with the 8 lead SOIC package, care must be taken to ensure that the Maximum Junction Temperature (T $_J$ , see "Absolute Maximum Ratings" table) isn't exceeded. As an example consider the HA-2842 in the SOIC package, with a required output current of 50mA at  $V_{OUT} = 10V$  with  $\pm 15V$  supplies. The power dissipation is the quiescent power (450mW = 30V x 15mA) plus the power dissipated in the output stage

(P<sub>OUT</sub> = 250mW = 50mA x (15V - 10V)), or a total of 700mW. The thermal resistance (θ<sub>JA</sub>) of the SOIC package is 157°C/W, which increases the junction temperature by 110°C over the ambient temperature (T<sub>A</sub>). Remaining below T<sub>JMAX</sub> requires that T<sub>A</sub> be restricted to ≤ 40°C (150°C - 110°C). Heatsinking would be required for operation at ambient temperatures greater than 40°C.

MAX  $P_{OUT}$  WITHOUT HEATSINK ( $V_S = \pm 15V$ )

| T <sub>A</sub> | 8 LEAD SOIC<br>(θ <sub>JA</sub> = 157°C/W) |  |  |  |

|----------------|--------------------------------------------|--|--|--|

| 85°C           | Heatsink Required                          |  |  |  |

| 70°C           | 60mW                                       |  |  |  |

| 25°C           | 350mW                                      |  |  |  |

Allowable output power can be increased by decreasing the quiescent dissipation via lower supply voltages.

For more information please refer to Application Note AN556, Thermal Safe Operating Areas for High Current Op Amps.

**Typical Performance Curves**  $T_A = 25^{\circ}C$ ,  $V_{SUPPLY} = \pm 15V$ ,  $R_L = 1k\Omega$ ,  $C_L < 10pF$ , Unless Otherwise Specified

FIGURE 1. FREQUENCY RESPONSE FOR VARIOUS GAINS

FIGURE 2. GAIN BANDWIDTH PRODUCT vs SUPPLY VOLTAGE

# $\textbf{Typical Performance Curves} \quad \text{$T_A=25^{\circ}C$, $V_{SUPPLY}=\pm15V$, $R_L=1$k$\Omega$, $C_L<10$pF, Unless Otherwise Specified (Continued) and the support of the property of the$

FIGURE 3. GAIN BANDWIDTH PRODUCT vs TEMPERATURE

FIGURE 5. PSRR vs FREQUENCY

FIGURE 7. SLEW RATE vs TEMPERATURE

FIGURE 4. CMRR vs FREQUENCY

FIGURE 6. INPUT NOISE vs FREQUENCY

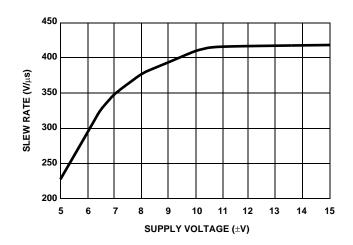

FIGURE 8. SLEW RATE vs SUPPLY VOLTAGE

## $\textbf{Typical Performance Curves} \quad \text{T}_{A} = 25^{o}\text{C}, \ \text{V}_{SUPPLY} = \pm 15\text{V}, \ \text{R}_{L} = 1\text{k}\Omega, \ \text{C}_{L} < 10\text{pF}, \ \text{Unless Otherwise Specified (Continued)}$

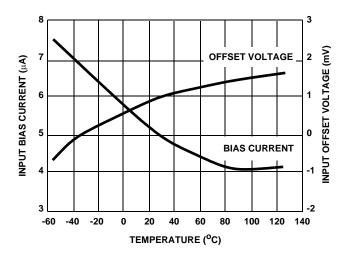

FIGURE 9. INPUT OFFSET VOLTAGE AND INPUT BIAS CURRENT VS TEMPERATURE

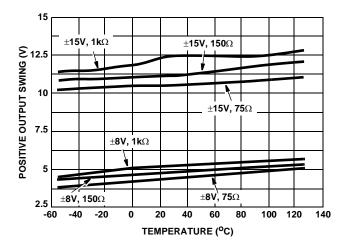

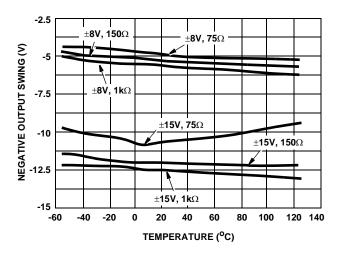

FIGURE 11. POSITIVE OUTPUT SWING vs TEMPERATURE

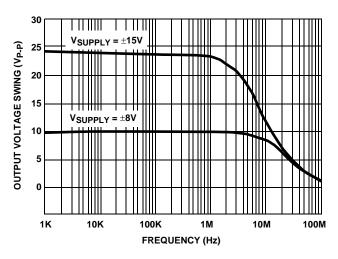

FIGURE 13. MAXIMUM UNDISTORTED OUTPUT SWING vs FREQUENCY

FIGURE 10. SUPPLY CURRENT vs SUPPLY VOLTAGE

FIGURE 12. NEGATIVE OUTPUT SWING vs TEMPERATURE

FIGURE 14. TOTAL HARMONIC DISTORTION vs FREQUENCY

# $\textbf{Typical Performance Curves} \quad \text{$T_A=25^{\circ}$C, $V_{SUPPLY}=\pm15$V, $R_L=1$k$\Omega$, $C_L<10$pF, Unless Otherwise Specified (Continued) and $T_{SUPPLY}=\pm15$V.}$

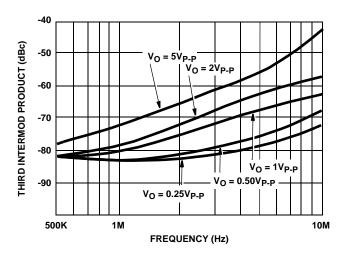

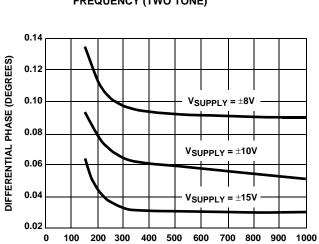

FIGURE 15. INTERMODULATION DISTORTION vs **FREQUENCY (TWO TONE)**

FIGURE 17. DIFFERENTIAL PHASE vs LOAD RESISTANCE

LOAD RESISTANCE ( $\Omega$ )

400

600 700 800 900

100

200 300

FIGURE 16. DIFFERENTIAL GAIN vs LOAD RESISTANCE

FIGURE 18. GAIN FLATNESS vs FREQUENCY (A<sub>VCL</sub> = 2)

1000

FIGURE 19. GAIN BANDWIDTH PRODUCT vs LOAD RESISTANCE

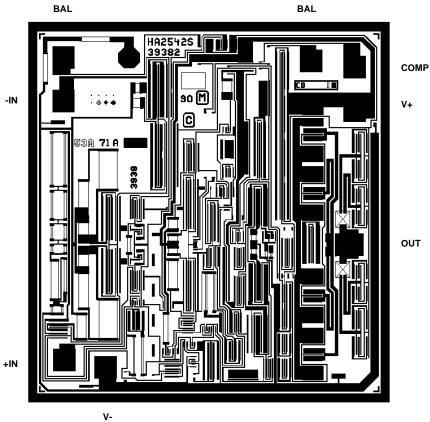

## Die Characteristics

## **DIE DIMENSIONS:**

77 mils x 81 mils x 19 mils  $1960\mu m \times 2060\mu m \times 483\mu m$

## **METALLIZATION:**

Type: Aluminum, 1% Copper Thickness: 16kÅ ±2kÅ

## **PASSIVATION:**

Type: Nitride over Silox Silox Thickness: 12kÅ ±2kÅ Nitride thickness: 3.5kÅ ±1kÅ

## SUBSTRATE POTENTIAL (POWERED UP):

V-

## TRANSISTOR COUNT:

58

## PROCESS:

High Frequency Bipolar Dielectric Isolation

## Metallization Mask Layout

HA-2842

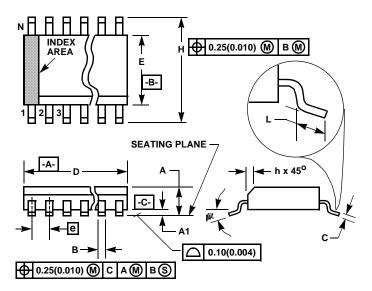

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M8.15 (JEDEC MS-012-AA ISSUE C) 8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INC    | INCHES         |      | MILLIMETERS    |   |  |

|--------|--------|----------------|------|----------------|---|--|

| SYMBOL | MIN    | MAX            | MIN  | MIN MAX        |   |  |

| Α      | 0.0532 | 0.0688         | 1.35 | 1.75           | - |  |

| A1     | 0.0040 | 0.0098         | 0.10 | 0.25           | - |  |

| В      | 0.013  | 0.020          | 0.33 | 0.51           | 9 |  |

| С      | 0.0075 | 0.0098         | 0.19 | 0.25           | - |  |

| D      | 0.1890 | 0.1968         | 4.80 | 5.00           | 3 |  |

| Е      | 0.1497 | 0.1574         | 3.80 | 4.00           | 4 |  |

| е      | 0.050  | 0.050 BSC      |      | 1.27 BSC       |   |  |

| Н      | 0.2284 | 0.2440         | 5.80 | 6.20           | - |  |

| h      | 0.0099 | 0.0196         | 0.25 | 0.50           | 5 |  |

| L      | 0.016  | 0.050          | 0.40 | 1.27           | 6 |  |

| N      | 8      | 3              | 8    |                | 7 |  |

| α      | 0°     | 8 <sup>0</sup> | 0°   | 8 <sup>0</sup> | - |  |

Rev. 0 12/93

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com