# Large Current External FET Controller Type Switching Regulators

# Step-down, High-frequency Switching Regulator (Controller type)

**BD63536FJ** No.09028EAT09

#### Description

The BD63536FJ is a gate direct drive switching regulator operational at a power supply voltage from 3V. This regulator uses a compact package SOP-J8 and operates as a switching regulator for the voltage control type of step-down DC/DC converter. The regulator features reliable design with  $\pm 1\%$  reference voltage accuracy, built-in current limit function ( $\pm 4\%$ ), and a variety of built-in protection circuits.

#### Features

- 1) Gate direct drive available (External Pch FET, Vcc-5.4V)

- 2) Built-in current limit function (150mV±4%)

- 3) Built-in gate-off function

- 4) Error amplifier reference voltage (1.25V±1%)

- 5) Built-in soft start

- 6) 2.5V regulator output

- 7) External oscillation frequency variable

- 8) Built-in thermal shutdown circuit

#### Applications

Laser beam printers, MFPs, PPCs, etc.

Absolute maximum ratings (Ta=25°C)

| Item                                                  | Symbol                           | Rating            | Unit |

|-------------------------------------------------------|----------------------------------|-------------------|------|

| Power supply voltage                                  | V <sub>CC</sub>                  | -0.2 to 32.0      | V    |

| Current detection pin                                 | V <sub>CS</sub>                  | -0.2 to 32.0      | V    |

| V <sub>CC</sub> -V <sub>CS</sub> potential difference | V <sub>CC</sub> -V <sub>CS</sub> | -0.2 to 5.0       | V    |

| Output current (DC)                                   | I <sub>OUT</sub>                 | 30 <sup>*1</sup>  | mA   |

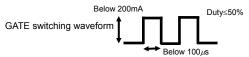

| Output current (peak)                                 | I <sub>OUTPEAK</sub>             | 200 <sup>*2</sup> | mA   |

| Power dissipation 1                                   | Pd1                              | 563 <sup>*3</sup> | mW   |

| Power dissipation 2                                   | Pd2                              | 675 <sup>*4</sup> | mW   |

| Operating temperature range                           | $T_{opr}$                        | -25 to 85         | Ĵ    |

| Storage temperature range                             | T <sub>stg</sub>                 | -55 to 150        | °C   |

| Junction temperature                                  | $T_{jmax}$                       | 150               | °C   |

<sup>1</sup> Should not exceed Pd value.

<sup>\*2</sup> Should not exceed Pd value when Pulse width tw≤100μs and Duty≤50%.

- Ratings for the IC alone. To use the IC at temperatures over Ta=25°C, derate power rating by 4.5mW/°C.

- \*4 Mounted on a glass epoxy of 70 mm × 70 mm × 1.6 mm. To use the IC at temperatures over Ta=25°C, derate power rating by 5.4mW/°C.

#### ●Operating conditions (Ta=-25 to +85°C)

| Itom                  | Cumbal |      | Unit |      |       |

|-----------------------|--------|------|------|------|-------|

| Item                  | Symbol | Min. | Тур. | Max. | Offic |

| Power supply voltage  | Vcc    | 3    | 24   | 30   | V     |

| Oscillation frequency | Fosc   | -    | -    | 300  | kHz   |

● Electrical characteristics (Unless otherwise specified, Ta=25°C, V<sub>CC</sub> =24V)

| Item                               | Symbol             | Limit                  |                        |                        | Unit  | Condition                        |

|------------------------------------|--------------------|------------------------|------------------------|------------------------|-------|----------------------------------|

| item                               | Symbol             | Min.                   | Тур.                   | Max.                   | Offic | Condition                        |

| General                            |                    |                        |                        |                        |       |                                  |

| Circuit current                    | I <sub>CC</sub>    | -                      | 2                      | 4                      | mA    | V <sub>OSC</sub> =0V             |

| Current limit block                |                    |                        |                        |                        |       |                                  |

| Switching voltage                  | V <sub>CL</sub>    | V <sub>CC</sub> -0.156 | V <sub>CC</sub> -0.150 | V <sub>CC</sub> -0.144 | V     | V <sub>CS</sub> : sweep down     |

| Output OFF switching voltage       | $V_{OOFF}$         | V <sub>CC</sub> -1.3   | V <sub>CC</sub> -1.0   | V <sub>CC</sub> -0.7   | V     | V <sub>CS</sub> : sweep down     |

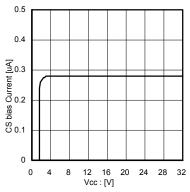

| CS input bias current              | I <sub>CS</sub>    | -                      | 0.3                    | 1.0                    | μΑ    | V <sub>CS</sub> =V <sub>CC</sub> |

| Output block                       |                    |                        |                        |                        |       |                                  |

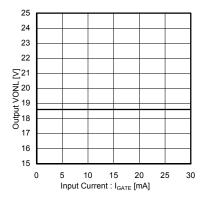

| GATE H voltage                     | $V_{ONH}$          | V <sub>CC</sub> -0.10  | V <sub>CC</sub> -0.05  | -                      | V     | I <sub>GATE</sub> =-10mA         |

| GATE L voltage                     | V <sub>ONL</sub>   | V <sub>CC</sub> -6.20  | V <sub>CC</sub> -5.40  | V <sub>CC</sub> -4.60  | V     | I <sub>GATE</sub> =10mA          |

| Reference voltage block            |                    |                        |                        |                        |       |                                  |

| VREF output voltage                | $V_{REF}$          | 2.375                  | 2.500                  | 2.625                  | V     | I <sub>VREF</sub> =-0.1mA        |

| Low input malfunction prevention   | circuit block      |                        |                        |                        |       |                                  |

| Threshold voltage                  | V <sub>UVLO</sub>  | 2.3                    | 2.5                    | 2.7                    | V     | V <sub>CC</sub> : sweep up       |

| Hysteresis voltage                 | ∠V <sub>UVLO</sub> | 0.05                   | 0.15                   | 0.25                   | V     |                                  |

| Triangular waveform oscillator blo | ck                 |                        |                        |                        |       |                                  |

| Oscillation H voltage              | Vosh               | 1.26                   | 1.40                   | 1.54                   | V     | V <sub>OSC</sub> : sweep up      |

| Oscillation L voltage              | V <sub>OSL</sub>   | 0.9                    | 1.0                    | 1.1                    | V     | V <sub>OSC</sub> : sweep down    |

| Error amplifier block              |                    |                        |                        |                        |       |                                  |

| Input bias current                 | I <sub>IN-</sub>   | -0.3                   | -0.1                   | -                      | μA    | IN-=0V                           |

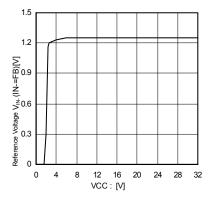

| Reference voltage                  | V <sub>IN-</sub>   | 1.237                  | 1.250                  | 1.263                  | V     | FB=V <sub>IN-</sub>              |

| Feedback H voltage                 | $V_{FBH}$          | 1.6                    | 1.9                    | -                      | V     | I <sub>FB</sub> =-100μA          |

| Feedback L voltage                 | $V_{FBL}$          | -                      | 0.6                    | 0.9                    | V     | I <sub>FB</sub> =100μA           |

● Reference Characteristics (Unless otherwise specified, Ta=25°C, Vcc =3V)

| Itom           | Symbol           | Reference value       |                       |       | Linit     | Condition               |

|----------------|------------------|-----------------------|-----------------------|-------|-----------|-------------------------|

| Item Symbol    | Min.             | Тур.                  | Max.                  | Unit  | Condition |                         |

| Output block   |                  |                       |                       |       |           |                         |

| GATE H voltage | V <sub>ONH</sub> | V <sub>CC</sub> -0.02 | V <sub>CC</sub> -0.01 | -     | V         | I <sub>GATE</sub> =-1mA |

| GATE L voltage | V <sub>ONL</sub> | -                     | 0.075                 | 0.150 | V         | I <sub>GATE</sub> =1mA  |

$<sup>\</sup>circ\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{^{''}}}\mbox{\ensuremath{$

#### ● Reference characteristics data (Unless otherwise specified, Ta=25°C, V<sub>CC</sub> =24V)

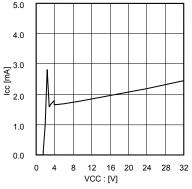

Fig.1 Circuit current

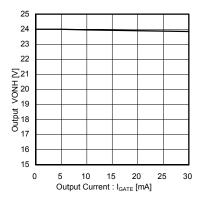

Fig.3 H voltage (Output block)

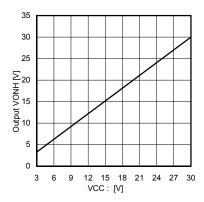

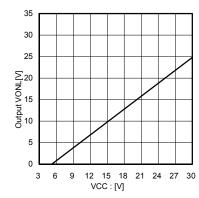

Fig.5 H voltage (Output block)

Fig.2 CS current

Fig.4 L voltage (Output block)

Fig.6 L voltage (Output block)

#### ● Reference characteristics data (Unless otherwise specified, Ta=25°C, VCC =24V)

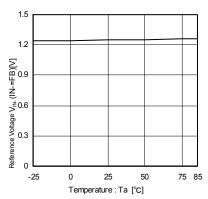

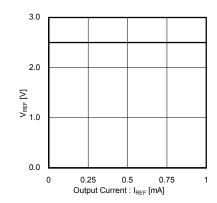

Fig.7 Reference Voltage (Error amplifier block)

Fig.8 Reference Voltage (Error amplifier block)

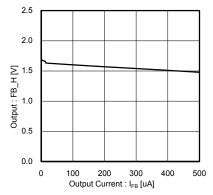

Fig.9 FB\_H voltage

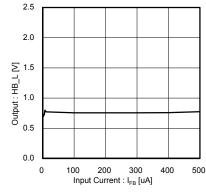

Fig.10 FB\_L voltage

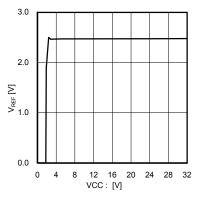

Fig.11 Reference Voltage (Reference voltage block)

Fig.12 Reference Voltage (Reference voltage block)

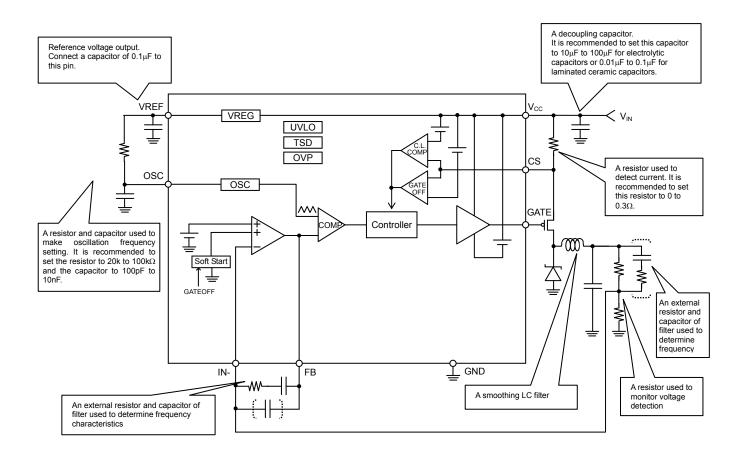

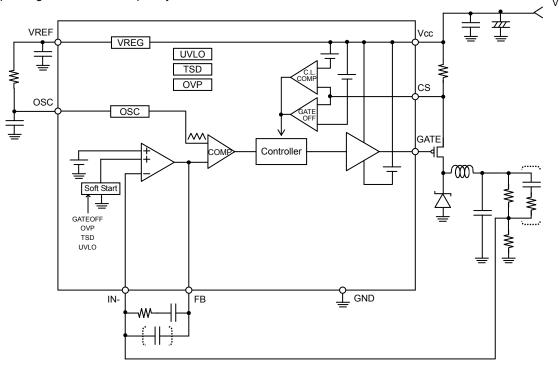

### ●Pin functions / Block diagram / Application circuit diagram / I/O equivalent circuit diagram Vcc

| PIN NO. | Pin Name | Function               |

|---------|----------|------------------------|

| 1       | osc      | PWM frequency setting  |

| 2       | VREF     | 2.5V regulator output  |

| 3       | FB       | Error amplifier output |

| 4       | IN-      | Error amplifier input  |

| 5       | GATE     | Gate output            |

| 6       | CS       | Current limit input    |

| 7       | Vcc      | Power supply           |

| 8       | GND      | Ground                 |

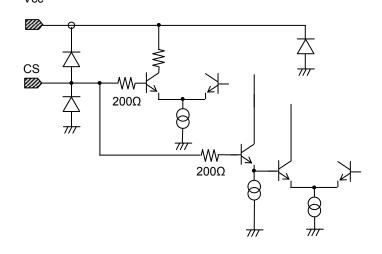

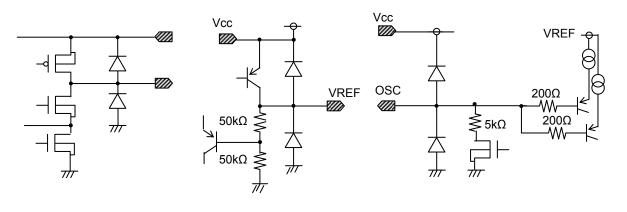

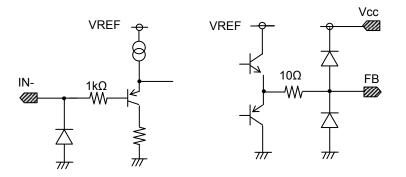

Fig.13 I/O equivalent circuit diagram

Fig.14 Typical block diagram / application circuit

#### Description of pins and functions

#### OVcc: Power supply pin

To apply large drive currents, provide thick and short low impedance wiring, and make current adjustment with careful attention paid to PWM switching noise so that  $V_{CC}$  voltage will be stable. It is also possible to arrange laminated ceramic capacitors of approximately  $0.01\mu$  to  $0.1\mu$ F in parallel with the aim of reducing power supply impedance in a broad frequency band. Take extra care for  $V_{CC}$  voltage so that it will not exceed its rating even for a moment. The  $V_{CC}$  pin has a built-in clamp element for electrostatic breakdown protection. If a sudden pulse signal or voltage such as a surge exceeding the absolute maximum rating is applied, this clamp element may be activated to lead to breakdown. To avoid this, NEVER exceed the absolute maximum rating. It is also effective to mount a zener diode having a rating approximate to the absolute maximum rating. In addition, note that since a diode for electrostatic breakdown protection is inserted between the  $V_{CC}$  pin and the GND pin, if an inverse voltage is applied to the  $V_{CC}$  pin and the GND pin, the IC may lead to breakdown.

#### OGND: Ground pin

In order to reduce noises due to switching current and stabilize the internal reference voltage of IC, minimize wiring impedance from this pin and maintain the potential at the minimum level in any operating state. In addition, design patterns so that the pin has no common impedance to other GND patterns.

#### OVREF: 2.5V regulator output pin

The VREF pin is a pin used to output internal reference voltage 2.5V (typ.) generated from power supply voltage input to the  $V_{CC}$  pin. In order to stabilize power supply, be sure to connect a  $0.1\mu F$  capacitor. This pin is also used as a bias power supply. For this application, set a load current to approximately 1mA or less. In addition, note that grounding this pin may pass a large current through the IC, causing it to break down.

#### OFB: Error amplifier output pin

The FB pin is an output pin of the feedback error amplifier.

#### OIN-: Error amplifier input pin

The IN- pin is an input pin of the feedback error amplifier.

#### OGATE: External FET drive pin

This GATE pin is a pin used to drive the external FET gate. Since output H voltage is " $V_{CC}$  voltage – 0.05V (typ)" and output L voltage is " $V_{CC}$  voltage – 5.4V (typ)", the pin is able to directly drive the external FET gate. Provide thick and short low impedance wiring from this pin. The GATE pin has a built-in clamp element for electrostatic breakdown protection. If a sudden pulse signal or voltage such as a surge exceeding the absolute maximum rating is applied, this clamp element may be activated to lead to breakdown. To avoid this, NEVER exceed the absolute maximum rating. It is also possible to make switching rate adjustment by mounting a resistor between the GATE pin and the external FET. In addition, note that since the GATE pin is designed to connect the internal regulator to CMOS output, if voltages between the  $V_{CC}$  pin and the GATE pin causes a significant difference by grounding or else, the IC may lead to breakdown.

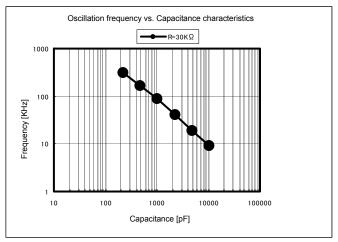

# OOSC: PWM oscillation frequency setting capacitance connection pin

The OSC pin is a pin used to produce a triangular waveform for output PWM oscillation frequency and connect an external resistor and capacitor. By connecting the external resistor and capacitor to this pin, perform charge and discharge. Since H level for a triangular waveform is 1.4V (typ) and L level is 1.0V (typ), a triangular waveform having an amplitude of  $\Delta$ OSC=0.4V (typ) is produced. The resistor determines a charge current, and the current is discharged inside the IC through resistance of 5k $\Omega$  (typ). However, at high frequencies in excess of several hundred kHz,  $\Delta$ OSC amplitude may exceed 0.4V (typ) due to delay in the internal circuit. To operate the IC at high frequencies, pay careful attention to the frequencies. The following section shows a characteristics table of capacitance when the external resistor is set to 30k $\Omega$ . For example, when the capacitor is set to 1000pF, frequency "f" will come to 91 [kHz].

Fig.15 Typical oscillation frequency characteristics

A calculation formula used to make oscillation frequency setting is shown below.

$$f = \frac{1}{C(0.31R + 1980) + 2e - 7}$$

Note that the formula shown above is a reference formula for calculations in the setting range of 470p to 2200pF for the capacitor and 30k to  $100k\Omega$  for the resistor. On application boards, oscillation frequencies may be influenced by wiring capacitance or the capacity of an oscilloscope used to monitor the frequencies and thereby calculated values may become different from actual values. Consequently, make it principle to use this formula as a guide for making oscillation frequency setting.

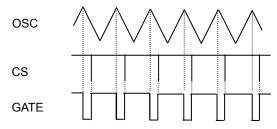

#### OCS: Current detection comparator input pin

The CS pin is an input pin of overcurrent detection circuit comparator. This IC has a built-in overcurent detection circuit (current limit function) used to turn OFF output current if an abnormal overcurrent such as short-circuited output current flows through the IC. This circuit monitors the currents of external FET such as current-sense resistor to input them to the CS pin. When a voltage input to the CS pin reaches "V<sub>CC</sub> voltage – 0.15V (typ)", the current limit function will be activated. And when it reaches the current limit voltage, the CS pin will turn OFF output current according to the set resistance and current values. Subsequently, the pin will be automatically reset when the OSC pin reaches its peak voltage. As just described, the CS pin is of the automatic resetting type. The CS pin is reset at the peak voltage of the OSC pin and, when the voltage reaches the set current limit voltage, reset at the same peak voltage again. Then, the CS pin repeats such resetting cycle. Since superimposing noises onto this pin may cause malfunctions, masking time of approximately 300ns has been internally set. In addition, it is possible to prevent noises form jumping in the CS pin by adding a capacitor to this pin. Since delay time of approximately 700ns including the said masking time of approximately 300ns is provided after the current limit is input until it reaches the GATE pin, if the IC is controlled at a duty cycle of 700ns or less, the current limit function will not be activated. Normally, no current setting seems to be made to the extent that the CS pin reaches the current limit voltage in the period of approximately 700ns. However, pay utmost attention to the current setting because it also depends on the external FET. If the overcurrent detection circuit is not used, short-circuit the CS pin to the  $V_{CC}$  pin. If a current exceeds the absolute maximum rating of the CS pin, the IC may break down. To avoid this, pay utmost attention to the current.

A current for the current limit function is set to "0.15V  $\div$  Resistance". For example, when resistance is 75m $\Omega$ , the set current for the current limit function will come to "2A".

Fig.16 Current limit operation

If a voltage to be input to the CS pin falls below " $V_{CC}$  voltage - 1V (typ)", the gate-off function will be activated to turn OFF output current. When the CS pin exceeds a voltage of " $V_{CC}$  voltage - 1V (typ)", the output current will be reset by the soft start function.

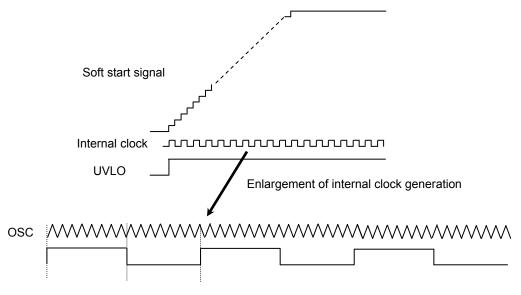

#### **OSOFT START**

This IC has a built-in soft start function. This function is used to generate a clock in sync with oscillation inside the IC and operate the internal 6bitDAC with this clock. Soft start time depends on the oscillation frequency. Taking a frequency 8 times as high as the oscillation frequency as a reference clock, raise the output voltage at a rate of 40mV/count. The output voltage will exceed approximately 1.25V at 32 counts. For example, when oscillation frequency  $f_{OSC}$  is set to 100 kHz, a period of time required to raise the voltage from 0V to 1.25V will come to approximately 2.56ms from " $10\text{yps} \times 8 \times 32$  counts".

Fig.17 Soft start operation

#### Protection circuits

#### OThermal shutdown (TSD) circuit

This IC has a built-in thermal shutdown (TSD) circuit as overheat protection. When the IC chip temperature exceeds 175°C (typ), GATE output will be turned OFF. When the temperature falls below 155°C (typ), the IC will return to the normal operation. In this case, the normal operation starts up in the soft start sequence. However, if external heat is continually applied to the IC even when the TSD circuit is in operation, the IC may cause thermal runaway, resulting in breakdown.

#### OOvercurrent protection circuit (Current limit function)

This IC has a built-in overcurrent protection circuit. This circuit is a circuit absolutely intended to protect the IC from breakdown due to overcurrent in abnormal states such as output short circuit, not intended to protect or guarantee sets with the overcurrent protection circuit incorporated. Consequently, do not design the protection of sets making use of the function of this circuit. For practical use, take physical safety measures such as use of fuses.

#### OUndervoltage lockout (UVLO) function

This IC has a built-in undervoltage lockout circuit to prevent malfunctions such as IC output at low power supply voltages. If power supply voltage falls below the operating voltage range, this UVLO function will be activated. However, if a voltage applied to the  $V_{CC}$  pin reaches 2.35V (typ), the UVLO function will turn OFF the Gate output once. The switching voltage is provided with hysteresis of approximately 0.15V (typ) in order to prevent malfunctions such as noises. If the UVLO function is cleared, the IC will start up in the soft start sequence.

#### OOvervoltage protection (OVP) function

This IC has a built-in overvoltage protection function as a protection circuit for a rise in power supply voltage. If power supply voltage exceeds the absolute maximum rating, this OVP function will be activated. However, if a voltage applied to the  $V_{CC}$  pin exceeds 33.5V (typ), the OVP function will turn OFF the Gate output once. The switching voltage is provided with hysteresis of approximately 1V (typ) in order to prevent malfunctions such as noises. If the OVP function is reset, the IC will start up in the soft start sequence.

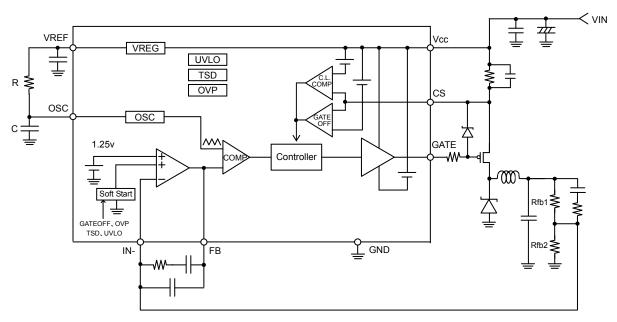

#### Switching regulator control

Fig. 18 shows the basic configuration of a switching regulator application. The error amplifier determines an output duty cycle so that a voltage used to monitor output voltage will become equal to the internal reference voltage. The output driver switches frequency at the said duty cycle, smoothes the switching voltage through the LC filter, and outputs Vout. This IC has an internal reference voltage of 1.25V (typ) and a recommended output voltage range of 3.3V to 5V. Note that if the output voltage is set to below 3.3V, for example to 1.25V, the output switching duty cycle may become narrow to disable current limit setting, depending on oscillation frequency to be used.

Fig.18 Switching regulator block diagram

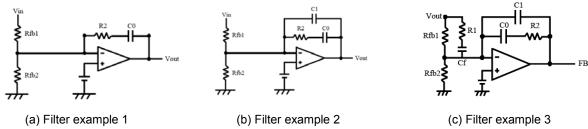

#### <Typical filter circuit>

When considering a filter circuit used to determine phase characteristics with the application of this IC, the three patterns shown in Fig. 19 below are available as a popular way to arrange the filter circuits. The selective use of these circuits is determined by the relationship between the PWM frequency to be used and the second pole of LC filter, the zero point at ESR of output capacitor, and ripple elimination rate at the PWM switching frequency to be used.

Fig.19 Examples of filter circuits used to determine phase characteristics

The circuit (a) is the simplest pattern and available for use if the output capacitor has high ESR.

The circuit (b) is a pattern designed by adding a capacitor to the pattern of (a) and available for use if the output capacitor has high ESR and the voltage ripple elimination rate at the PMW frequency needs to be increased from that of the pattern of (a). The circuit (c) is a pattern designed by adding two zero-points and thereby available for use even if the output capacitor has small ESR.

Selectively use the circuits according to the requirement specifications and situations for inductors, capacitors, and PWM frequency using the patterns shown above.

#### <Typical application design>

The following section shows a typical application design.

Fig.20 Typical application design

#### <Example of simple design>

The following section shows a design example of constants targeting the applications listed below. Power supply voltage=24V, Output voltage=3.3V, Coil=47 $\mu$ F, Output capacitor=2200 $\mu$ F, Resr=0.015 $\Omega$ , PWM frequency=80 kHz, and Load resistance=10 $\Omega$

#### 1. Determination of values of output voltage detecting resistance

The internal reference voltage is 1.25V and the maximum IN-bias current is  $2\mu A$ . Consequently, to output Vout of 3.3V, select resistance values enough to keep from the influence of this bias current, that is, Rfb1=33k $\Omega$  and Rfb2=20k $\Omega$ . In this case, the ratio of Rfb1 to Rfb2 cannot be changed, but the number of digits of resistance values can be changed.

#### 2. Setting of R (resistance) and C (capacitance) used to make PWM frequency setting

When setting C to 1000pF and R to 39kΩ, the PWM frequency will come to approximately 80 kHz.

# 3. Determination of L (inductance) and C (capacitance) in accordance with characteristic requirements This design example is based on L=47 $\mu$ F, C=2200 $\mu$ F, and Resr=0.015 $\Omega$ .

#### <Reference>

Determine a value for the coil to the extent that the system does not enter intermittent mode until it reaches the minimum value of the preset output current. In this case, however, careful attention should be paid not to cause the coil to become saturated when the maximum current flows.

Reference formula:  $L=(Vi-Vo)VoT/\Delta ILVi$  [H], where  $\Delta IL=$  Ripple current of coil, T=1/S witching frequency

Determine a value for the output capacitor from ESR and output ripple voltage. It is recommended to use a capacity taking into account enough margin to a value meeting the specification.

Reference formula:  $\Delta Vout \approx \Delta IL \times Resr$ , where Resr = Equivalent series resistance of capacitor

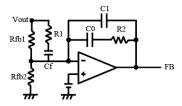

#### 4. Selection of filter circuit

For the selection of a filter type, PWM frequency, second pole of LC: " $f\omega p$ ", and zero point at ESR: "fzesr" are important. This design example is based on the following:

$$f\omega p = \frac{1}{2\pi\sqrt{LC(1 + \frac{\text{Re } sr}{R0})}} = \frac{1}{2\pi\sqrt{47u \times 2200u(1 + \frac{0.015}{10})}} = 495Hz$$

$$fz = \frac{1}{2\pi\ C\text{Re } sr} = \frac{1}{2\pi \times 2200u \times 0.015} = 4.823kHz$$

For this design, PWM frequency is 80 kHz. When looking at unity gain frequency in a total loop with consideration given to ripple elimination at this frequency, the unity gain frequency should be set in the range of 1/5 to 1/10 of the PWM frequency, i.e., 8 kHz to 16 kHz. This frequency comes to 10 or more times as high as that for  $f_{\mu\nu}$ , however the return of zero point at ESR cannot be expected particularly in the range of 8 kHz to 16 kHz because fz is set to 4.823 kHz. As a result, design the filter circuit based on the Example (c) shown on the previous page.

Fig.21 Example (c) of filter circuit used to determine phase characteristics

#### 5. Determination of filter constant

Look at the design example based on (c). Making an approximate calculation by taking " $\infty$ " as the open loop gain of the amplifier in this circuit will come to the following formula.

$$G(j\omega) = \frac{Vout}{Vin} = -\frac{1}{j\omega \bullet \left(C0 + C1\right)Rfb1} \bullet \underbrace{\left(1 + j\omega C0R2\right)\!\left(1 + j\omega Cf(Rfb1 + R1)\right)}_{\left[1 + j\omega(C0)/C1\right)R2\right] \bullet \left(1 + j\omega R1Cf\right)}_{\left[1 + j\omega(C0)/C1\right)R2} \bullet \underbrace{\left(1 + j\omega C0R2\right)\!\left(1 + j\omega R1Cf\right)}_{\left[1 + j\omega(C0)/C1\right)R2} \bullet \underbrace{\left(1 + j\omega C0R2\right)\!\left(1 + j\omega Cf(Rfb1 + R1)\right)}_{\left[1 + j\omega(C0)/C1\right)R} \bullet \underbrace{\left(1 + j\omega(C0)/C1\right)Rfb1}_{\left[1 + j\omega(C0)/C1\right)R} \bullet \underbrace{\left(1 + j\omega(C0)/C1\right)R}_{\left[1 + j\omega(C0)/C1\right)R} \bullet \underbrace{\left(1 + j\omega(C0)/C1\right)R}_{\left$$

| DC gain          | $Gain = \frac{1}{(C0 + C1)Rfb1}$                                      |  |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|--|

| Zero point       | $fz1 = \frac{1}{2\pi (R1 + Rfb1)Cf}$ $fz = \frac{1}{2\pi R 2C0}$      |  |  |  |  |

| Cutoff frequency | $fp 1 = \frac{1}{2 \pi R 1Cf}$ $fp 2 = \frac{1}{2 \pi R 2(C0 // C1)}$ |  |  |  |  |

The transfer functions of this circuit are shown above. Two zero points can be set. Look at the filter constant using this circuit as shown below. Approximating phase characteristics in the whole loop with the use of this circuit will come to the following formula.

Phase = Second pole of LC filter + Zero point of LC filter + First pole of error amplifier

- + Second pole + -90° (1/s) of error amplifier + First zero-point of error amplifier

- + Second zero-point

Make calculations by converting these items into a formula and supposing that unity gain frequency is 8 kHz and phase margin is  $51^{\circ}$ . Since directly calculating constants results in values in too small digits, the values need to be rounded off. Then, the constants come to Rfb1=33k $\Omega$ , Rfb2=20k $\Omega$ , R1=10k $\Omega$ , R2=120k $\Omega$ , C0=220pF, C1=51pF, and Cf=1nF. In this case, when looking at the LC filter on the ideal basis of only the second pole + zero point, the unity gain frequency will be calculated to 10 kHz and the phase margin to approximately 54°. Actually, the inductance and capacitance of printed circuit board will be added, and thereby errors will be caused in calculation results depending on the printed circuit board used. Consequently, it is considered acceptable to make fine adjustment of resistance and the capacitance of capacitor with FRA according to the calculation results and then determine the constants.

#### Notes for Use

#### (1) Absolute maximum ratings

An excess in the absolute ratings such as applied voltage, operating temperature range, etc. can break down devices, thus making it impossible to identify a destruction state such as short or open circuit mode. If any special mode to exceed the absolute maximum ratings is expected, consider adding circuit protection devices such as fuses.

#### (2) Reverse connection of power supply connector

Making a reverse connection of the power supply connector can cause the IC to break down.

#### (3) Power supply line

If current regenerated by back electromotive force flows back, consider adding protection devices such as insertion of a capacitor between the power supply and ground as a path of regenerative current and thoroughly check capacitance for any problems with characteristics such as lack of capacitance of electrolytic capacitors caused at low temperatures, and then determine the power supply line.

#### (4) GND potential

The potential of the GND pin should be maintained at the minimum level in any operating state.

#### (5) Transient changes

In this IC, the GATE pin L voltage is set to " $V_{CC}$  voltage -5.4V (typ)" with the internal regulator of the IC. If output makes a sudden change due to high switching speed, the voltage can cause transient deviation in excess of " $V_{CC}$  voltage -6.2V (max)". To avoid this and also protect between the gate and the source of external MOS-FET, it is recommended to insert and clamp a proper zener diode between the GATE pin and the power supply pin.

#### (6) Thermal design

Provide thermal design having a sufficient margin in consideration of power dissipation (Pd) in the practical operating conditions. Use the thermal design providing as wide radiation pattern as possible in thorough consideration of practical operating conditions.

#### (7) Inter-pin shorts and mounting errors

To mount the IC on printed circuit boards, pay utmost care to the direction and the displacement of the IC. The IC may get damaged if there is any mounting error or if a short circuit is established due to foreign matter entered between pins. In addition, thoroughly note that this IC may also get damaged if the VREF pin or GATE pin reaches low potential or is grounded.

#### (8) Operation in strong magnetic field

This IC is not designed for operation in the presence of strong magnetic field. To use the IC in a strong magnetic field, ensure that such use causes the IC not to malfunction.

#### (9) Thermal-protection circuit (TSD circuit)

This IC has a built-in thermal-protection circuit (TSD circuit). If chip temperature rises beyond  $T_{jmax}$ =150°C, the GATE pin will output high voltage and turn OFF the external output transistor. The thermal-protection circuit (TSD circuit) is a circuit absolutely intended to protect the IC from thermal runaway under abnormal conditions beyond  $T_{jmax}$ =150°C, not intended to protect or guarantee sets. Consequently, do not design the protection of sets making use of the function of this circuit

| TSD ON temperature [°C] (typ.) | Hysteresis temperature [°C] (typ.) |

|--------------------------------|------------------------------------|

| 175                            | 25                                 |

#### (10) Testing on application board

When testing the IC on an application board with a capacitor connected to the pin, the IC can be subjected to stress. In this case, be sure to discharge the capacitor after each process. For static electricity protection, ground the IC during the assembly process, and further pay utmost attention to the transport and storage of the IC. In addition, to connect the IC to a jig up to the testing process, be sure to turn OFF prior to connection, and disconnect the IC only after turning OFF the power supply.

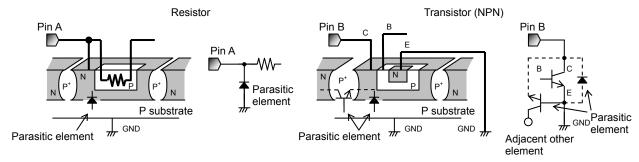

#### (12) IC pin input

This monolithic IC contains P + Isolation and P substrate layers between adjacent elements in order to keep them isolated. P-N junctions are formed at the intersections of these P layers and the N layers of other elements, thus making up different types of parasitic elements.

For example, if a resistor and a transistor is connected with pins respectively as shown in Fig. 22,

OWhen GND>(Pin A) for the resistor, or when GND>(Pin B) for the transistor (NPN),

P-N junctions operate as a parasitic diode.

OWhen GND>(Pin B) for the transistor (NPN),

the parasitic NPN transistor operates by the N layer of other element adjacent to the parasitic diode aforementioned. Due to the structure of the IC, parasitic elements are inevitably formed depending on the relationships of potential. The operation of parasitic elements can result in interferences in circuit operation, leading to malfunctions and eventually breakdown of the IC. Consequently, pay utmost attention not to use the IC for any applications by which the parasitic elements are operated, such as applying a voltage lower than that of GND (P substrate) to the input pin.

Fig.22 Pattern diagram of parasitic elements

#### (13) Wiring patterns

Give thorough consideration to power supply and ground wirings, for example, reduce the common impedance and minimize ripple.

If there are large-current ground and small-signal ground, it is recommended to isolate the large-current ground pattern from the small-signal ground pattern and ground these patterns to a single reference point on the set so that fluctuations in voltage due to the resistance of pattern wiring and large current will not result in fluctuations in the voltage of the small-signal ground. In addition, pay careful attention to the ground wiring patterns of external parts so that no fluctuations in voltage will be caused.

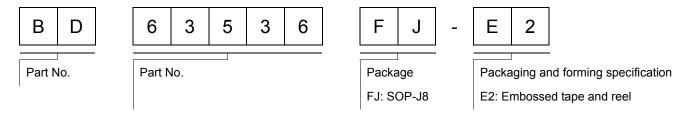

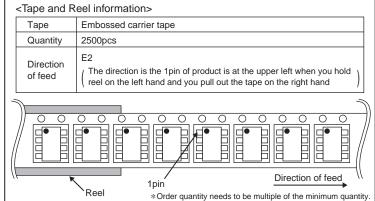

## Ordering part number

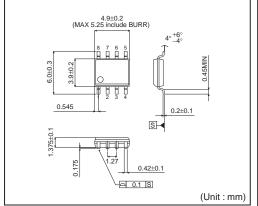

#### SOP-J8

#### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations.

More detail product informations and catalogs are available, please contact us.

# ROHM Customer Support System

http://www.rohm.com/contact/