# 300 MHz Clock Generator for RAMBUS™ Systems

## **General Description**

The ICS9111-01 is a high speed clock generator designed to support the 600Mbit/line data transfer rates made possible by local phase alignment technologies such as RAMBUS<sup>TM</sup> style systems. Generating RCLK rates as high as 280 MHz in 3V systems from either a 20 MHz crystal or external system reference, the ICS9111-01 is ideal for graphics applications.

The RCLK open collector buffer output impedance is less than  $10\Omega$  to allow external terminating impedance and voltage combinations for RAMBUS style systems. Cycleto-cycle jitter is less than 100ps and output skew is less than 50ps and the 50% duty cycle is maintained to within  $\pm 5\%$  for series terminations to  $V_{term}$ .

#### **Features**

- 300 MHz RCLK covers RAMBUS speeds to 600Mbit/line at 3.3V±5%.

- Output capable of running between 60 to 280 MHz with 3.3 V  $\pm$  10% V<sub>DD</sub>; up to 300 MHz for 3.3 V  $\pm$  5% V<sub>DD</sub>

- Less than 100ps cycle-to-cycle jitter (RCLK2) (150ps for RCLK1)

- $50 \pm 5\%$  duty cycle

- Open drain drivers allow matched termination

- Drives 20-50  $\Omega$  transmission lines

- Nominal 18.0 MHz crystal or extended reference (5 to 21.4 MHz)

- On-chip loop filter components

- 3.0V 3.6 V supply range

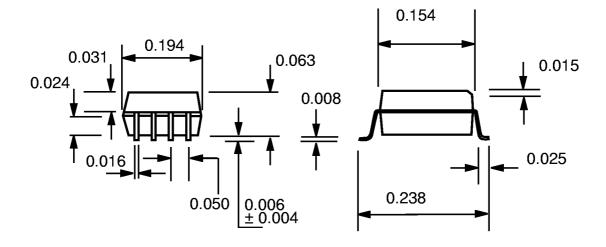

- 8-pin 150-mil SOIC package

- Custom options capable

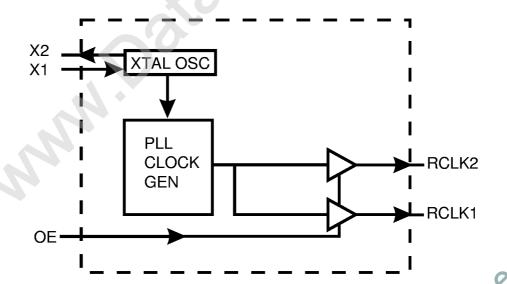

## **Block Diagram**

RAMBUS is a trademark of Rambus, Inc.

# ICS9111-01

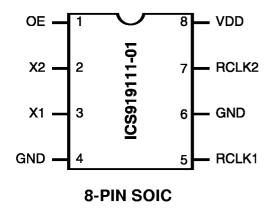

# Pin Configuration

# **Functionality**

| RCLK Ratio | X1, X2<br>(MHz) | OE | RCLK (MHz) |

|------------|-----------------|----|------------|

| X1*14      | 18.0            | 1  | 252        |

|            | 18.0            | 0  | Tristate   |

# Pin Descriptions

| PIN NUMBER | PIN NAME    | ТҮРЕ | DESCRIPTION                                                                                                                                                      |

|------------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | OE          | IN   | Output enable causes all outputs to tristate when at a low level; has a pull-up.                                                                                 |

| 2          | X2          | IN   | Crystal drive output from device, which includes crystal load capacitance.                                                                                       |

| 3          | X1          | IN   | Crystal or external clock input to device. This input includes crystal load capacitance and feedback bias resistor for a 12 to 24 MHz crystal, nominally 18 MHz. |

| 4, 6       | GND         | PWR  | Ground connection for logic, PLL and output buffers.                                                                                                             |

| 5, 7       | RCLK(1,2)   | OUT  | Output buffer pins, device has open-drain N-channel MOSFET device going to ground. See application information for pull-up/termination recommendations.          |

| 8          | $ m V_{DD}$ | PWR  | $V_{\text{DD}}$ positive power supply.                                                                                                                           |

\* External crystal components are optional. Device contains on-chip loadcapacitors and feedback resistor.

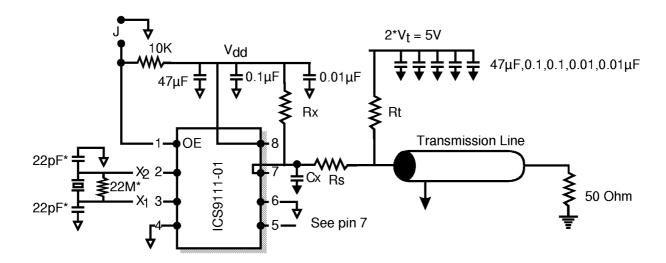

## Figure 1

#### Note:

The series resistor,  $R_s$ , sets the signal swing and the pull-up resistor,  $R_x$ , sets reference bias level, rise and fall times, and duty cycle of the signal waveform.

The recommended values for  $R_t$  and  $R_s$  are:

$R_t = 50$  or 25 Ohms,  $R_s = 8$  to 12 Ohms.

## ICS9111-01

## **Absolute Maximum Ratings**

| AV <sub>DD</sub> , V <sub>DD</sub> referenced to GND | 7V                                     |

|------------------------------------------------------|----------------------------------------|

| Operating temperature under bias                     | 0 to +70 °C                            |

| Storage temperature                                  | 65 to +150 °C                          |

| Voltage on I/O pins referenced to GND                | GND - 0.5 V to V <sub>DD</sub> + 0.5 V |

| Power dissipation                                    | 0.5 Watts                              |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

### **Electrical Specifications at 3.3V**

VDD =  $3.3V \pm 10\%$ ,  $T_A = 0.70$  °C, unless otherwise stated

| DC Characteristics                           |                     |                                |                       |       |       |        |  |

|----------------------------------------------|---------------------|--------------------------------|-----------------------|-------|-------|--------|--|

| PARAMETER                                    | SYMBOL              | CONDITION                      | MIN                   | TYP   | MAX   | UNIT   |  |

| Input Low Voltage                            | $ m V_{IL}$         |                                | -                     | -     | 0.2V  | V      |  |

| Input High Voltage                           | $V_{ m IH}$         |                                | $0.7~\mathrm{V_{DD}}$ | -     | -     | V      |  |

| Input Low Current <sup>2</sup>               | $I_{\mathrm{I\!L}}$ | V = 0                          | -5.0                  | 0     | 5.0   | μA     |  |

| Input High Current                           | $I_{ m IH}$         | VIN = VDD                      | -5.0                  | 0     | 5.0   | μA     |  |

| Input Pull-up<br>Resistor Value <sup>2</sup> | $R_{ m PU}$         | $V_{\rm IN} = V_{\rm DD}$ -1 V | 50.0                  | 140.0 | 400.0 | K Ohms |  |

| Output Impedance <sup>1</sup>                | R <sub>OUT</sub>    |                                | -                     | 5.0   | 10.0  | Ohms   |  |

| Supply Current                               | $I_{DD}$            | Unloaded                       | -                     | 47.0  | 60.0  | mA     |  |

#### **Notes:**

- 1 Parameter is guaranteed by design and characterization. Not subject to product testing.

- 2 The pull-up on the OE pin is measured at  $V_{DD}$ -1 V. The pull-up current switches off at inputs  $\ll V_{DD}$ /3.

## **Electrical Characteristics at 3.3 V**

VDD =  $3.3V \pm 10\%$ ,  $T_A = 0.70$  °C, unless otherwise stated

| AC Characteristics                                          |               |                                  |        |       |       |        |  |

|-------------------------------------------------------------|---------------|----------------------------------|--------|-------|-------|--------|--|

| PARAMETER                                                   | SYMBOL        | CONDITION                        | MIN.   | TYP.  | MAX.  | UNIT   |  |

| Output Frequency                                            | Fout1         |                                  | 60.0   | 250.0 | 280.0 | MHz    |  |

| Output Frequency                                            | <b>F</b> оит2 | V <sub>DD</sub> ≥3.15            | 60.0   | 250.0 | 300.0 | MHz    |  |

| Output Signal Swing <sup>1,2</sup>                          | Vs            |                                  | 1.2    | 1.4   | 1.6   | V      |  |

| Output Asymmetry                                            | Aco           |                                  | -15.0  | 0     | 15.0  | %      |  |

| Locking Time <sup>1</sup>                                   |               |                                  | -      | 2.0   | 10.0  | ms     |  |

| Output Skew <sup>1</sup>                                    | Skew          | RCLK2 to RCLK1                   | -      | -     | 50.0  | ps     |  |

| Absolute Jitter <sup>1</sup>                                | Tjabs         | @ 252 MHz 10,000 cycles RCLK2    | -100.0 | 50.0  | 100.0 | ps     |  |

| Absolute fitter                                             |               | @ 252 MHz 10,000 cycles RCLK1    | -150.0 | 60.0  | 150.0 | ps     |  |

| Cycle-to-Cycle Jitter <sup>1</sup>                          | Tjee          | @ 252 MHz 8,250 cycles RCLK2     | -      | -     | 100.0 | ps p-p |  |

| Peak-Peak                                                   |               | @ 252 MHz 8,250 cycles RCLK1     | -      | -     | 150.0 | ps p-p |  |

| Accumulated Jitter <sup>1</sup> over                        | Tr            | @ 252 MHz 10,000 intervals RCLK2 | -      | -     | 150.0 | ps p-p |  |

| 3 Cycles Peak - Peak                                        | Tjtot3        | @ 252 MHz 10,000 intervals RCLK1 | -      | -     | 180.0 | ps p-p |  |

| Accumulated Jitter <sup>1</sup> over 40 Cycles Peak - Peak  | Tjtot40       | @ 252 MHz 10,000 intervals       | -      | 150.0 | 250.0 | ps p-p |  |

| Accumulated Jitter <sup>1</sup> over 256 Cycles Peak - Peak | Tjtot256      | @ 252 MHz 10,000 intervals       | -      | -     | 300.0 | ps p-p |  |

| Narrowband Signal to<br>Noise Ratio <sup>1</sup>            | SNRn          | @ 252 MHz                        | -40.0  | 1     | 1     | dBc    |  |

| Narrowband Cut-off<br>Frequency <sup>1</sup>                | $f_n$         | @ 252 MHz                        | 1      | 1     | 50.0  | MHz    |  |

| Wideband Signal to<br>Noise Ratio <sup>1</sup>              | SNRw          | @ 252 MHz                        | -100.0 | -     | -     | dBc/Hz |  |

| Duty Cycle <sup>1,2</sup>                                   |               | @ 50%/V <sub>REF</sub>           | 45.0   | 50.0  | 55.0  | %      |  |

| Output Rise and Fall<br>Time <sup>1,2</sup>                 | Tr, Tf        | 20-80%                           | 300.0  | -     | 500.0 | ps     |  |

#### **Notes:**

- 1 Parameter is guaranteed by design and characterization. Not subject to product testing.

- 2 See Figure 1 page 3

8-Pin SOIC

# **Ordering Information**

#### ICS9111M-01

Example: