# HD61945MP

### PLL Synthesizer IC

The HD61945MP for PLL synthesizer Ic has been developed for cellular radio applications.

#### **Features**

- Incorporates an 11-bit counter for standard frequency, a 10-bit main counter for the comparative frequency and a 7-bit swallow counter.

- · Low power dissipation in intermittent operation mode.

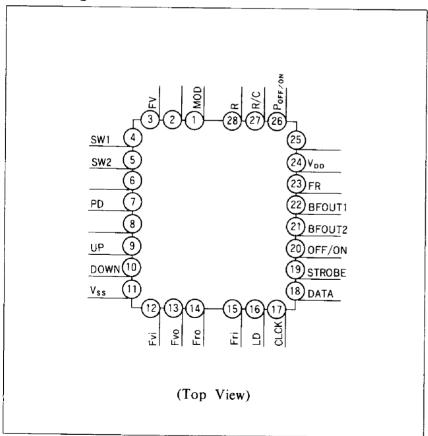

## Pin Arrangement

## Absolute Maximum Ratings (Published specifications) (Ta = 25°C, Vss = 0 V)

| Item                                | Symbols             | HD61945MP                | Unit | Notes |

|-------------------------------------|---------------------|--------------------------|------|-------|

| Supply voltage                      | V <sub>DD</sub> max | 7.0                      | V    | *2    |

| Input terminal voltage range        | V <sub>IN</sub>     | $-0.3$ to $V_{DD} + 0.3$ | V    |       |

| Power dissipation                   | Pd                  | 500                      | mW   | *1    |

| Operating ambient temperature range | Topr                | -30 to +75               | °C   |       |

| Storage temperature range           | Tstg                | -55 to +125              | °C   |       |

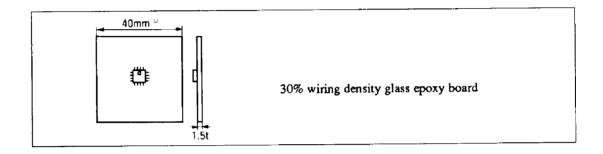

Notes: \*1. For Ta = 75°C when mounted on a glass epoxy board.

\*2. Standard operating voltage should be  $5.0 \pm 0.25$  V.

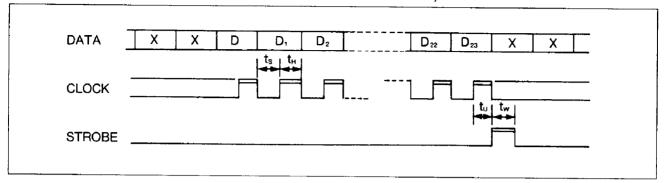

## Data, Clock, Strobe Timing Chart

(ts, th  $\cong$  500 ns or > 400 ns, tw  $\cong$  500 ns or > 400 ns, tv  $\cong$  500 ns or > 0 ns)

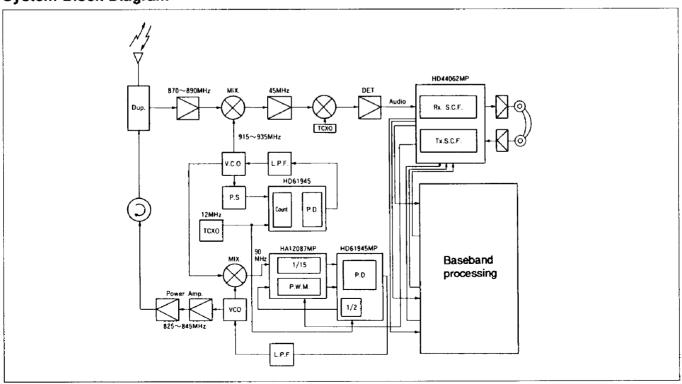

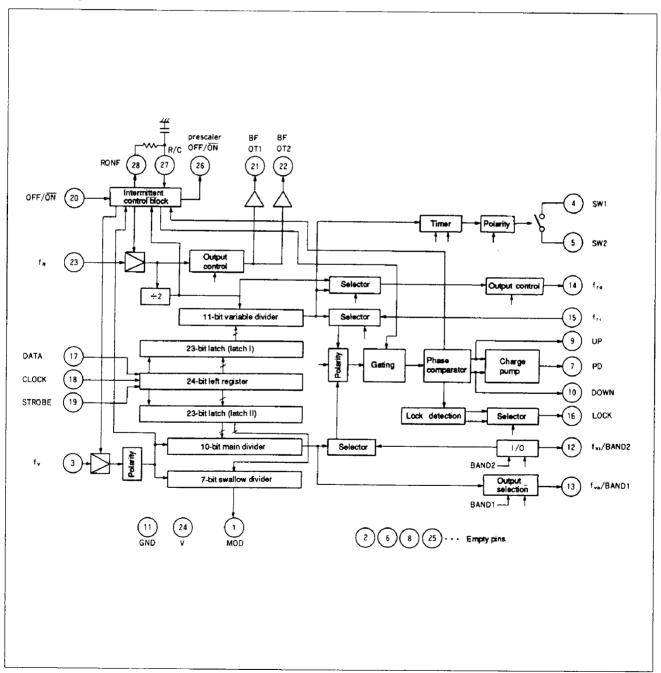

#### **Block Diagram**

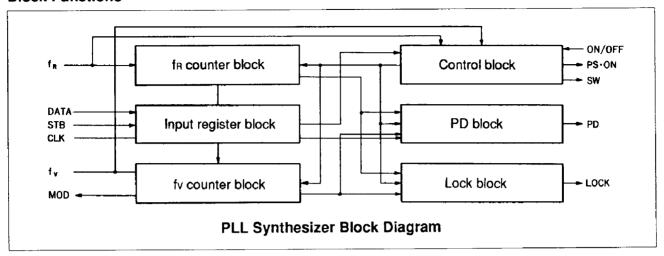

#### **Block Functions**

fix counter block: The fix consists of an 11-bit counter and a half divider. Reference frequency fix is divided by the dividend at the input register pins.

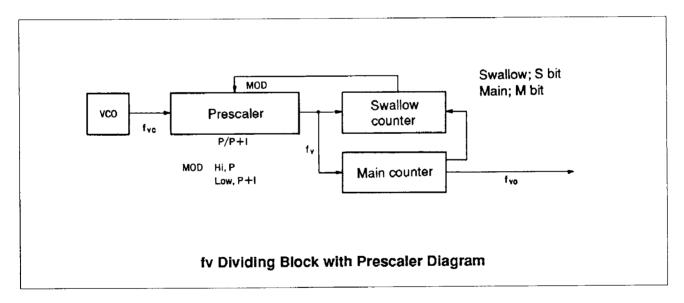

fv counter block: The fv counter block consists of a 10-bit main counter 7-bit swallow counter. It determines the dividend with an external prescaler.

Input register block: The input register block has two 24-bit registers and determines block setting values. It converts serial input signals to parallel format for input register.

PD block: The PD block sends acceleration or deceleration signals to VCO with a phase detector. It can reverse external inputs and signals, depending on values set at the input register.

Lock block: The lock block detects PLL lock status.

Control block: The control block controls block timing operations.

#### **Pin Functions**

| Pin No. | Pin Name  | I/O         | Description                                                                                                                                                                                                                                                                                                                                                                                                | Remarks                                |

|---------|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1       | MOD       | 0           | Control signal output pin for the dual-modulus prescaler connected externally.                                                                                                                                                                                                                                                                                                                             | Set to "L" when<br>pin 20 is "H."      |

| 2       | NC        | _           |                                                                                                                                                                                                                                                                                                                                                                                                            |                                        |

| 3       | FV        | I           | Input pin for the comparison divider. To connect to the prescaler, ac connection should be used because the amplifier incorporates a bias circuit.                                                                                                                                                                                                                                                         |                                        |

| 4       | SW1       | _           | An analog switch is incorporated between pins 4 and 5. It switches on or off according to the strobe signals (pin 19) for the serial-data latch or the synchronous signals from the intermittent control block. Polarity is determined by D20 of the control register II. Switching time can be set to four modes by D21 and D22. Therefore, the switches can be used to change the VCOLPF characteristic. | Refer to Control register I and II.    |

| 5       | SW2       |             |                                                                                                                                                                                                                                                                                                                                                                                                            |                                        |

| 6       | NC        | _           |                                                                                                                                                                                                                                                                                                                                                                                                            |                                        |

| 7       | PD        | 0           | Built-in charge pump output pin. Output polarity is set by D21 of control register I. PD output determined by the relation between reference divider output phase \$\phi\$ r and comparison divider output phase \$\phi\$ is shown in the chart below.                                                                                                                                                     | Refer to Control<br>register I.        |

|         |           |             | D <sub>21</sub> set value $\phi r > \phi v$ $\phi r = \phi v$ $\phi r < \phi v$                                                                                                                                                                                                                                                                                                                            |                                        |

|         |           |             | "0" "H" HiZ "L" "1" "L" HiZ "H"                                                                                                                                                                                                                                                                                                                                                                            |                                        |

| 8       | NC        |             |                                                                                                                                                                                                                                                                                                                                                                                                            |                                        |

| 9       | UP        | 0           | External charge pump output pin. Output polarity can be changed by D21 of control register I. Output determined by the relation between reference divider output phase of and comparison divider output phase of is shown in the chart below.                                                                                                                                                              | Refer to Control register I.           |

| 10      | DOWN      | O           | Pin Name D <sub>21</sub> set value $\phi r > \phi v$ $\phi r = \phi v$ $\phi r < \phi$                                                                                                                                                                                                                                                                                                                     | <u>v</u>                               |

|         |           |             | UP "0" "L" "H" "H"                                                                                                                                                                                                                                                                                                                                                                                         | _                                      |

|         |           |             | "1" "H" "H" "L"  DOWN "0" "H" "H" "L"                                                                                                                                                                                                                                                                                                                                                                      | _                                      |

|         |           |             | "1" "H" "H" "H"                                                                                                                                                                                                                                                                                                                                                                                            |                                        |

| 11      | Vss       | <del></del> |                                                                                                                                                                                                                                                                                                                                                                                                            |                                        |

| 12      | Fvi/BAND2 | I/O         | When D18 of control register I is "0," pin 12 is in output mode and outputs the state of D19 of control register II to switch VCO band over. When D18 is "1," pin 12 is in input mode and external fv can be input to the phase comparator instead of the internal fv from the comparison divider.                                                                                                         | Refer to Control<br>register I and II. |

| 13      | Fvo/BAND1 | 0           | When D19 of the control register is "0," pin 13 outputs the state of the control register II to switch VCO band over. When D19 is "1," the output from the comparison divider can be output from this pin.                                                                                                                                                                                                 | Refer to Control register I and II.    |

| 14      | FR0       | 0           | When Do of the control register is "0," fr from the reference divider is output from pin 14. When Do is "1," the reference frequency input from pin 23 is reduced by half and is output from pin 14.                                                                                                                                                                                                       | Refer to Control register I.           |

## Pin Functions (continued)

| Pin No.  | Pin Name         | I/O | Description                                                                                                                                                                                                    | Remarks                                             |

|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 15       | FR1              | I   | External fr input pin. When D20 of control register I is "1," input signals from this pin are input to the phase comparator instead of the fr output signals from the reference divider.                       | Refer to Control register I.                        |

| 16       | LOCK             | O   | phase comparator lock detection pin. Outputs "H" when synchronizing. For output mode, either level output or pulse output can be chosen by D22 of control register I.                                          | Refer to Control register I.                        |

| 17       | CLOCK            | I   | Reference clock input pin for serial data input to control registers I and II.                                                                                                                                 | Pull down                                           |

| 18       | DATA             | I   | Input pin for serial data to be input to control registers I and II. The last data D23 determines whether the data is latched into control register I or II.                                                   | Refer to Control<br>register I and II.<br>Pull down |

| 19       | STROB            | I   | Strobe signal input pin to latch the data into the control register.  (Data is fetched when "H" signal is input.)                                                                                              | Pull down                                           |

| 20       | OFF/ON           | I   | Phase synchronous dividing control signal input pin. When "L" is input, phase synchronous dividing is started and the state becomes operation mode. When "H" is input, the state becomes receive waiting mode. | Pull down                                           |

| 21<br>22 | BFOUT2<br>BFOUT1 | 0   | Pin 23 fR inputs are output through the buffer. When D12 = "1," output is prohibited ("L" is fixed). Whe D12 = "0," signals are output through the butter.                                                     | Refer to Control register I and II.                 |

| 23       | FR               | I   | Reference signal(12 MHz) input pin. AC connection should be done with TCXO because the amplifier incorporates a bias circuit.                                                                                  |                                                     |

| 24       | $V_{DD}$         | _   |                                                                                                                                                                                                                |                                                     |

| 25       | NC               |     |                                                                                                                                                                                                                |                                                     |

| 26       | D OFF/ON         | 0   | Prescaler power on/off signal input pin. Input P off/on = "L" signal                                                                                                                                           |                                                     |

| 27       | R/C              | I   | to turn on the prescaler power.                                                                                                                                                                                |                                                     |

| 28       | RONF             | 0   | Connect a register between pins 27 and 28 and ground a capacitor at pin 27. Then, set operation timing between the prescaler and this IC with a constant.                                                      |                                                     |

| _    |

|------|

| ᅙ    |

| ټ    |

| d    |

|      |

| Se   |

| Ø    |

| =    |

| _    |

| 0    |

| -    |

| >    |

| ¥o¥  |

| 0    |

| Ť    |

|      |

| 10   |

| 뽀    |

| য    |

| 1945 |

| ~    |

| 9    |

| 561  |

| ☱    |

| ᅩ    |

|                               | I date I                                      | arch I (Crandord divider fr                                     | HU61945 HOW to USE Latch          | o use Lato      |                                 |                                   | ć                  |

|-------------------------------|-----------------------------------------------|-----------------------------------------------------------------|-----------------------------------|-----------------|---------------------------------|-----------------------------------|--------------------|

| 1.0                           | T - 1                                         | - 1                                                             | 7 110)                            |                 | Laich                           | ivider: Iv                        | → rv U)            |

| Bit<br>Name                   |                                               | Latch input data                                                | - Remarks                         | N.              | Lat                             | Latch input data                  |                    |

|                               | 0                                             | 1                                                               | NCHIMI KS                         | ivame           | 0                               | 1                                 | _ Kemarks          |

| ,                             | Output fr = fr + 2N                           | Output fr = fr + 2                                              |                                   | LSB             |                                 |                                   |                    |

| D2 LSB                        | $Nm = 2 \times N$                             |                                                                 | When $2N/ + 2 = "1"$              |                 | Total dividing frequency Ntv    | uency Ntv                         |                    |

| 3 2                           | N is specified as a binary number.            | inary number.                                                   | and $f_REXT = "1,"$               |                 | is specified as a binary        | ıary                              |                    |

| 1 2                           |                                               |                                                                 | D1 to D11 are                     |                 | number when the latch is        | atch is                           |                    |

| ]<br>30<br>30                 | When $2N/ + 2 = "0,"$ Note that the specified | When $2N/+2 = "0$ ,"  Note that the specified as binous another | disregarded.                      | 1               | combined with the prescaler     | prescaler                         |                    |

| D7                            | INIK CALI DE SPECIILE                         | i as omary number.                                              |                                   |                 | 128/129.                        |                                   |                    |

| D8                            |                                               |                                                                 | When $2N/ + 2 = "1"$              | e               | (Ntv max = 2'' - 1)             |                                   |                    |

| 2                             |                                               |                                                                 | and $fEXT = "0,"$                 | JaC<br>         |                                 |                                   |                    |

| D10                           |                                               |                                                                 | f = f + 2N is                     | I gr            |                                 |                                   |                    |

| D11 MSB                       |                                               |                                                                 | provided to PD.                   | ribi v          |                                 |                                   |                    |

| D12 fx Buffer<br>OUT          | Output fix to outside                         | Not output fix to outside                                       | fk: Output buffer                 | Dia             |                                 |                                   |                    |

| D13<br>D14 for<br>D15 testing | 0                                             | Prohibited                                                      |                                   |                 |                                 |                                   |                    |

| D16 for<br>POLARITY           | Falling clock                                 | Rising clock                                                    | In combination<br>with prescaler  | MSB             |                                 |                                   |                    |

| D17 fv<br>OITTPIFF            | Not output fy to                              | Output fy to                                                    | fv0 outputting                    | (Reserve)       | - 70.00                         |                                   |                    |

| 101100                        | anismo                                        | outside                                                         |                                   |                 |                                 |                                   |                    |

| D18 fv<br>EXTERNAL            | Internal fv                                   | External fv                                                     | fv PD input<br>selection          | BANDI           |                                 |                                   | fv OUTPUT = "0"    |

| D19 fr<br>OUTPUT              | Not output fr to outside                      | Output fr to<br>outside                                         | fr 0 outputting                   | BAND 2          | VCO band                        | VCO band switch data              | fv EXTERNAL = "0"  |

| D20 fr<br>EXTERNAL            | Internal fr                                   | External fr                                                     | fr PD input<br>selection          | SWITCH<br>POLA  | Switch is "ON" when timer is on | Switch is "OFF" when timer is on. | Analog switch      |

| D21 PD<br>POLARITY            | φr≥φv: "H"                                    | φr>φν: "L"                                                      | PD polarity<br>(UP/DN) selection  | LSB             | "0": T = 16 t                   | "2": T = 64 t                     | 3, 6               |

| D22 LOCK<br>DETECT            | Level output                                  | Pulse output                                                    | "H" outputs during synchronizing. | Tim<br>MSB      | "1": $T = 32\tau$               | "3": $T = 128 \tau$               | JI/I = 1           |

| D23 LATCH<br>SELECT           | 1                                             | 0                                                               | Latch I selection                 | LATCH<br>SELECT | 0                               | -                                 | Latch II selection |

|                               |                                               |                                                                 |                                   |                 |                                 |                                   |                    |

# **Electrical Characteristics** (Ta = 25°C, VDD = 5.0 V, VSS = 0 V)

| Item                            | Symbol           | Test<br>Conditions       | Min                   | Тур  | Max                 | Unit | Applicable pins   | Notes |

|---------------------------------|------------------|--------------------------|-----------------------|------|---------------------|------|-------------------|-------|

| Supply voltage                  | $V_{DD}$         |                          | 4.75                  | 5.00 | 5.25                | V    | 24                |       |

| Input voltage (1)               | VIHI             |                          | $0.7 \times V_{DD}$   |      |                     | ν    | 3, 15, 17, 18,    |       |

| Input voltage (2)               | VIL1             |                          |                       |      | $0.3 \times V_{DD}$ | V    | 19, 20, 23        |       |

| Output voltage (1)              | Vон              | -Iон = $0.4  mA$         | V <sub>DD</sub> - 0.4 | _    |                     | V    | 1, 7, 9, 10, 12,  |       |

| Output voltage (2)              | Vol              | IoL = 0.4  mA            | _                     | _    | 0.4                 | V    | 13, 14, 16, 21,   |       |

|                                 |                  |                          |                       |      |                     |      | 22, 26, 28        |       |

| Input leakage current (1)       | Int (1)          | $V_{IN} = 5.0 V$         |                       |      | 1                   | μA   | 4, 5, 12          |       |

| Input leakage current (2)       | IIL (2)          | $V_{IN} = 0 V$           | -1                    |      |                     | μA   | 4, 5, 12, 15, 17, | ,     |

|                                 |                  |                          |                       |      |                     |      | 18, 19, 20, 27    |       |

| Operating current               | Icc              | $V_{DD} = 5.0 \text{ V}$ |                       | 7.5  | 12.0                | μΑ   | 30                | *1    |

| Three-state leakage current (1) | ) Izh            | $V_7 = 5.0 \text{ V}$    | <del></del>           |      | 1                   | μΑ   | 7                 |       |

| Three-state leakage current (2) | ) Izl            | V7 = 0 V                 | -1                    | _    |                     | μΑ   | 7                 |       |

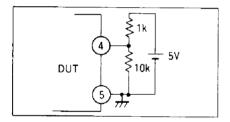

| Switch-on voltage               | I40N             |                          | _                     |      | 1                   | V    | 4                 | *2    |

| Switch-off voltage              | I40FF            |                          | 4.2                   | 4.5  | _                   | V    | 4                 | *2    |

| Input voltage (3)               | V <sub>IH2</sub> |                          | 4.1                   |      | -                   | V    | 12                |       |

| Input voltage (4)               | VIL2             |                          |                       |      | 0.8                 | V    | 12                | · · · |

Notes: \*1. Value when CH1 is locked (Rx = 915.03 MHz)

<sup>\*2.</sup> Test with the measurement circuit in figure 1.

Figure 1

| Pin No.  1 2 3 4 5 6 | Clock Power Source | Input<br>(N.C) | Output<br>MOD |   |

|----------------------|--------------------|----------------|---------------|---|

| 2<br>3<br>4<br>5     |                    |                |               | · |

| 3<br>4<br>5          |                    |                |               |   |

| 5                    |                    |                |               |   |

| 5                    |                    | FV             |               |   |

|                      |                    |                | SW1           |   |

| 6                    |                    |                | SW2           |   |

|                      |                    | (N.C)          |               |   |

| 7                    |                    |                | PD            |   |

| 8                    |                    | (N.C)          |               |   |

| 9                    |                    |                | UP            |   |

| 10                   |                    |                | DOWN          |   |

| 11                   | Vss                |                |               |   |

| 12                   |                    | Fvi            | BAND2         |   |

| 13                   |                    |                | Fvo           |   |

| 14                   |                    |                | Fro           |   |

| 15                   |                    | Fri            |               |   |

| 16                   |                    |                | LD            |   |

| 17                   | Clock              | CLOCK          |               |   |

| 18                   |                    | DATA           |               |   |

| 19                   |                    | STROBE         |               |   |

| 20                   |                    | OFF/ON         |               |   |

| 21                   |                    |                | BF OUT2       |   |

| 22                   |                    |                | BF OUT1       |   |

| 23                   |                    | FR             |               |   |

| 24                   | $V_{DD}$           |                |               |   |

| 25                   |                    | (N.C)          |               |   |

| 26                   |                    |                | P OFF/ON      |   |

| 27                   |                    | R/C            |               |   |

| 28                   |                    |                | R             |   |

Notes on denotation: Terminals are denoted by tij, and non-used terminals are denoted by NC.

### System Block Diagram