ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

# **VORTEX CHIPSET**

# DSLAM REFERENCE DESIGN: SYSTEM DESIGN

RELEASED

Issue 4

December, 2000

© 2000 PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 Phone 604.415.6000 FAX 604.415.6200

This document is for the internal use of PMC-Sierra, Inc. and PMC-Sierra, Inc. customers only.

In any event, no part of this document may be reproduced in any form without the express written consent of PMC-Sierra, Inc.

PMC-Sierra, Inc. RELEASED REFERENCE DESIGN PMC-1990832 **ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

# **REVISION HISTORY**

| Issue<br>No. | Issue Date     | Details of Change                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4            | December 2000  | Replaced "metadriver" with "VORTEX Chipset Driver" for consistency with software driver documents.  Better LVDS hot swap explanation and cell transfer, which is affected by setting OCAEN bit in register 0x0A of the S/UNI-DUPLEX at the very end of the chipset activation. Register write sequence is required. The sequence is already implemented with the VORTEX Chipset Driver on CD-ROM Ver 3.0. |

| 3            | September 2000 | Updated with WAN Card Issue 3, Line Card Issue 3, Core Card Issue 3 and release of VORTEX chipset metadriver. Removed errors and typos. Updated LED description on front panel. Updated current supply to each DSLAM card.                                                                                                                                                                                |

| 2            | February 2000  | Block Diagram of Wan Card updated to include changes made to Wan Card reference design. Updated most obvious deficiencies and inconsistencies with present knowledge about DSLAM reference design. Also: replaced phrase "DSLAM chipset" with "VORTEX chipset", replaced Core Card Block Diagram with updated one, updates to front panel drawings and shelf drawings.                                    |

| 1            | August 1999    | Creation of Document                                                                                                                                                                                                                                                                                                                                                                                      |

© 2000 PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 Phone 604.415.6000 FAX 604.415.6200

This document is for the internal use of PMC-Sierra, Inc. and PMC-Sierra, Inc. customers only.

In any event, no part of this document may be reproduced in any form without the express written consent of PMC-Sierra, Inc.

#### DSLAM REFERENCE DESIGN: SYSTEM DESIGN

# **CONTENTS**

| 1. | TECHI | NOLOGY OVERVIEW                                              | 1  |

|----|-------|--------------------------------------------------------------|----|

|    | 1.1.  | Introduction                                                 | 1  |

|    | 1.2.  | DSLAM Reference Design Features                              | 1  |

|    | 1.3.  | Example of a DSLAM Connection in an ADSL Application         | 2  |

|    | 1.4.  | DSLAM Block Diagram                                          | 3  |

|    | 1.5.  | CompactPCI Shelves                                           | 4  |

|    |       | 1.5.1. Shelf Types                                           | 4  |

|    |       | 1.5.2. DSLAM Shelf                                           | 4  |

|    |       | 1.5.3. Rear Panel I/O                                        | 4  |

|    |       | 1.5.4. Hot Swap on cPCI backplane                            | 5  |

|    | 1.6.  | DSLAM Reference Design Package                               | 5  |

|    | 1.7.  | VORTEX Chipset Development Kits                              | 5  |

| 2. | DSLA  | M REFERENCE DESIGN SHELF                                     | 6  |

|    | 2.1.  | DSLAM Reference Design Architecture                          | 6  |

|    |       | 2.1.1. DSLAM Reference Design Architecture Block Diagram     | 6  |

|    |       | 2.1.2. Core Card Architecture Block Diagram                  | 7  |

|    | 2.2.  | DSLAM Shelf Configuration                                    | 9  |

|    |       | 2.2.1. DSLAM System Block Diagram                            | 10 |

|    |       | 2.2.2. Front Plates on DSLAM Cards                           | 12 |

|    | 2.3.  | LVDS Interface                                               | 13 |

|    |       | 2.3.1. LVDS Introduction                                     | 13 |

|    |       | 2.3.2. DSLAM High-Speed LVDS Serial Interface                | 16 |

|    |       | 2.3.3. ATM Cell on High-speed Link                           | 18 |

|    |       | 2.3.4. Inband Communication Channel Over the High-speed Link | 20 |

|    |       | 2.3.5. Example of LVDS Layout on Core Card                   | 21 |

|    | 2.4.  | 8kHz Interface and System Synchronization                    | 22 |

| 3. | REFE  | RENCE DESIGN CARDS                                           | 26 |

|    | 3.1.  | Core Card                                                    | 26 |

|    |       | 3.1.1. Block Diagram                                         | 26 |

|    |       | 3.1.2. Core Card Software/Firmware                           | 28 |

|    | 3.2.  | WAN Card                                      |      |  |  |

|----|-------|-----------------------------------------------|------|--|--|

|    |       | 3.2.1. Block Diagram                          | . 30 |  |  |

|    |       | 3.2.2. WAN Card Software/Firmware             | . 32 |  |  |

|    | 3.3.  | Line Card                                     | . 33 |  |  |

|    |       | 3.3.1. Line Card Software/Firmware            | . 34 |  |  |

|    | 3.4.  | CPU Card                                      | . 35 |  |  |

|    | 3.5.  | LEDs on the Front Panel                       | . 35 |  |  |

|    | 3.6.  | Card Hot-Swap                                 | . 36 |  |  |

|    |       | 3.6.1. Power Rail Hot Swap Control            | . 36 |  |  |

|    |       | 3.6.2. PCI Interface                          | . 37 |  |  |

|    |       | 3.6.3. LVDS Interface                         | . 37 |  |  |

|    | 3.7.  | Power Supply Requirement                      | . 38 |  |  |

| 4. | FRONT | T PANEL LEDS                                  | . 40 |  |  |

|    | 4.1.  | Core Card LEDs                                | . 40 |  |  |

|    | 4.2.  | Line Card LEDs                                | . 41 |  |  |

|    | 4.3.  | WAN Card LEDs                                 | . 42 |  |  |

|    | 4.4.  | Example of the LED Placement                  | . 43 |  |  |

| 5. | DSLAM | / SHELF BACKPLANE                             | . 45 |  |  |

|    | 5.1.  | Introduction                                  | . 45 |  |  |

|    | 5.2.  | Reference Design Backplane                    | . 46 |  |  |

|    |       | 5.2.1. Example DSLAM Shelf Backplane          | . 46 |  |  |

|    |       | 5.2.2. LVDS-Backplane                         | . 47 |  |  |

|    | 5.3.  | DSLAM Cards vs. LVDS-Backplane                | . 49 |  |  |

|    | 5.4.  | Example of a Card Interface to LVDS-Backplane | . 50 |  |  |

|    | 5.5.  | LVDS Termination on DSLAM Shelf               | . 52 |  |  |

|    |       | 5.5.1. Power Rails on the LVDS-Backplane      | . 54 |  |  |

| 6. | CONN  | ECTOR PINOUT ON DSLAM BACKPLANE               | . 55 |  |  |

|    | 6.1.  | P51 at Slot 1                                 | . 56 |  |  |

|    | 6.2.  | P52 at Slot 2                                 | . 57 |  |  |

|    | 6.3.  | P53 at Slot 3                                 | . 58 |  |  |

|    | 6.4.  | P54 at Slot 4                                 | . 59 |  |  |

|    | 6.5.  | P55 at Slot 5                                 | . 60 |  |  |

|    |       |                                               |      |  |  |

#### ISSUE 4

|     | 6.6. | P56 at Slot 6                  | 61 |

|-----|------|--------------------------------|----|

|     | 6.7. | P57 at Slot 7                  | 63 |

|     | 6.8. | P58 at Slot 8                  | 64 |

| 7.  | PINO | JT ON DSLAM CARDS              | 66 |

|     | 7.1. | Line Card Backplane Conenctors | 67 |

|     |      | 7.1.1. J5 on Line Card         | 67 |

|     |      | 7.1.2. J4 on Line Card         | 68 |

|     |      | 7.1.3. J3 on Line Card         | 68 |

|     |      | 7.1.4. J2 on Line Card         | 68 |

|     |      | 7.1.5. J1 on Line Card         | 68 |

|     | 7.2. | WAN Card Pinout                | 69 |

|     |      | 7.2.1. J5 on WAN Card          | 69 |

|     |      | 7.2.2. J4 on WAN Card          | 70 |

|     |      | 7.2.3. J3 on WAN Card          | 70 |

|     |      | 7.2.4. J2 on WAN Card          | 70 |

|     |      | 7.2.5. J1 on WAN Card          | 70 |

|     | 7.3. | Core Card Pinout               | 70 |

|     |      | 7.3.1. J5 on Core Card         | 70 |

|     |      | 7.3.2. J4 on Core Card         | 72 |

|     |      | 7.3.3. J3 on Core Card         | 72 |

|     |      | 7.3.4. J2 on Core Card         | 72 |

|     |      | 7.3.5. J1 on Core Card         | 72 |

|     | 7.4. | LVDS Interface on Card Front   | 73 |

| 8.  | HARD | WARE                           | 74 |

|     | 8.1. | LVDS-backplane                 | 74 |

|     | 8.2. | Shelf Metal-work               | 75 |

|     | 8.3. | Switching Power Supply         | 75 |

| 9.  | SOFT | WARE                           | 76 |

|     | 9.1. | Drivers for the VORTEX chipset | 76 |

|     | 9.2. | Microprocessor Firmware        | 76 |

|     | 9.3. | Programmable Logic Devices     | 76 |

| 10. | APPE | NDIX – A: REAR PANEL I/O       | 77 |

|     |      |                                |    |

| ISSUE | 4 |

|-------|---|

|-------|---|

| 11. | APPE  | NDIX- B: DSLAM DUAL-BACKPLANE SHELF             | 78 |

|-----|-------|-------------------------------------------------|----|

|     | 11.1. | DSLAM Demonstration Shelf                       | 78 |

|     | 11.2. | Example Dual Backplane Shelf Connection Diagram | 79 |

| 12. | GLOS  | SSARY                                           | 81 |

REFERENCE DESIGN

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

# **LIST OF FIGURES**

| FIGURE 1.  | DSLAM-ADSL in the Public Telephone/Data Network     | 2  |

|------------|-----------------------------------------------------|----|

| FIGURE 2.  | DSLAM Overview                                      | 3  |

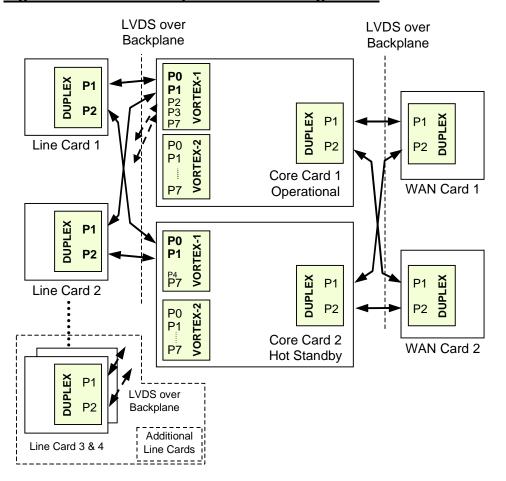

| FIGURE 3.  | DSLAM Shelf Architecture Block Diagram              | 7  |

| FIGURE 4.  | Core Card Architecture Block Diagram                | 8  |

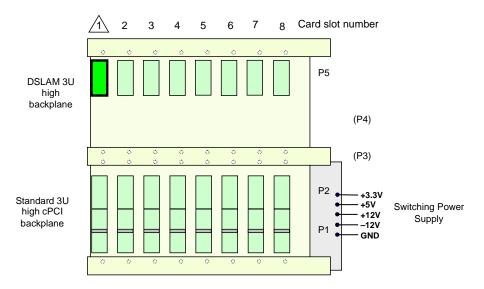

| FIGURE 5.  | Development Shelf Configuration                     | 9  |

| FIGURE 6.  | DSLAM Reference Design Shelf Block Diagram          | 10 |

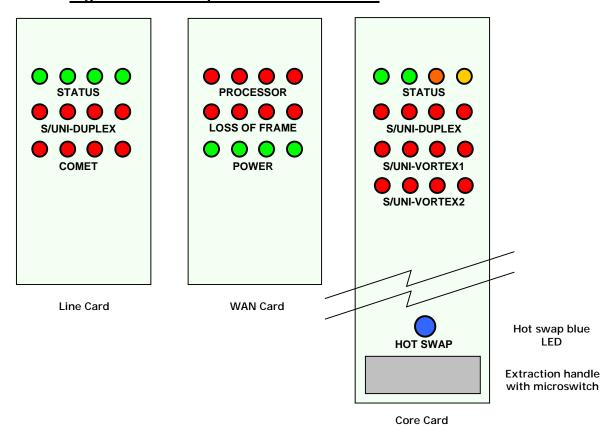

| FIGURE 7.  | Front Plate for WAN, LC and CC Cards                | 12 |

| FIGURE 8.  | Differential Voltage Swings                         | 14 |

| FIGURE 9.  | LVDS Interface                                      | 15 |

| FIGURE 10. | Low Voltage Differential Signal Output levels       | 16 |

| FIGURE 11. | High-Speed Serial Link Data Structure               | 18 |

| FIGURE 12. | LVDS on Core Card                                   | 21 |

| FIGURE 13. | Prepend Fields                                      | 22 |

| FIGURE 14. | Example of 8kHz Synchronization                     | 23 |

| FIGURE 15. | Core Card Block Diagram                             | 27 |

| FIGURE 16. | Core Card Top View                                  | 28 |

| FIGURE 17. | WAN Card Block Diagram                              | 30 |

| FIGURE 18. | WAN Card Top View                                   | 31 |

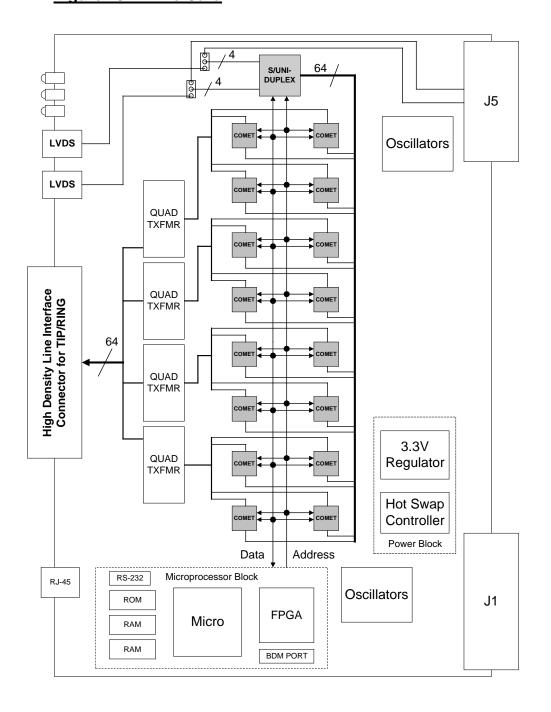

| FIGURE 19. | Line Card                                           | 33 |

| FIGURE 20. | Example of LEDs Placement                           | 43 |

| FIGURE 21. | Example DSLAM Backplane                             | 46 |

| FIGURE 22. | LVDS-backplane Basic Configuration                  | 47 |

| FIGURE 23. | LVDS-Backplane                                      | 48 |

| FIGURE 24. | Line Card and Core Card interface to LVDS-Backplane | 51 |

| FIGURE 25. | Example of WAN Card and Core Card Connection        | 52 |

| FIGURE 26. | Unconnected LVDS Termination                        | 53 |

| FIGURE 27. | LVDS Pinout on DSLAM Cards                          | 73 |

| FIGURE 28. | PCB                                                 | 74 |

| FIGURE 29. | Rear Panel I/O                                      | 77 |

| FIGURE 30. | Optional Demonstration DSLAM Shelf                  | 78 |

| FIGURE 31. | Dual Backplane Shelf Connection Diagram             | 79 |

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## **REFERENCES**

- 1. PMC-Sierra Inc., PMC-1990815, "DSLAM Reference Design: Core Card", June 1999.

- 2. PMC-Sierra Inc., PMC-1990354, "DSLAM Reference Design: Line Card", Issue 3, July 2000.

- PMC-Sierra Inc., PMC-1990474, "DSLAM Reference Design: WAN Card", Issue 3, July 2000.

- **4.** PMC-Sierra Inc., PMC-1990816, "DSLAM Apps Note: Signal Integrity and Timing Simulation for VORTEX Chipset", June 1999.

- 5. PMC-Sierra Inc., PMC-970127, "Synchronization for Wide Area Networks with S/UNI-PLUS Reference Design", PMC-Sierra Document, Issue 1, May 1997.

- **6.** PMC-Sierra Inc., PMC-981025, "S/UNI-VORTEX and S/UNI-DUPLEX Technical Overview", Issue2, June 1999.

- 7. PMC-Sierra Inc., PMC-2000504, "DSLAM Reference Design: Line Card Software Manual", Issue1, May 2000.

- **8.** PMC-Sierra Inc., PMC-2000684, "DSLAM Reference Design: WAN Card Software Manual", Issue1, May 2000.

- 9. PMC-Sierra Inc., PMC-1991454, S/UNI-APEX H/W Programmer's Guide, Issue 2, April 2000.

- **10.** Bell Communications Research "SONET Transport Systems: Common Generic Criteria," GR-253-CORE, Issue 2, December 1995.

- 11. Bell Communications Research "Clocks for the Synchronized Network: Common Generic Criteria" GR-1244-CORE, Issue 1, June 1995.

- 12. ITU-T-"The control of jitter and wander within digital networks which are based on the synchronous digital hierarchy (SDH)", March 1993.

- **13.** PCI Industrial Computers manufacturers Group (PICMG) "CompactPCI Specification", PICMG 2.0 R2.1, September 2, 1997.

- 14. PCI Industrial Computers manufacturers Group (PICMG) "Hot Swap Specification", PICMG 2.1 R1.0, May 14, 1998. (Draft not approved)

- 15. ADSL Forum, Web Page, <a href="http://www.adsl.com">http://www.adsl.com</a> .

- **16.** PMC-Sierra Inc., general web page <a href="http://www.pmc-sierra.bc.ca">http://www.pmc-sierra.bc.ca</a>.

- **17.** Montrose, Mark I., "Printed Circuit Board Design Techniques for EMC Compliance", IEEE Press, 1996.

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## 1. TECHNOLOGY OVERVIEW

#### 1.1. Introduction

PMC-Sierra's Digital Subscriber Line Access Multiplexer (DSLAM) is a network element that supports high bandwidth applications in the public telephone network and provides both data and voice over existing subscriber lines. DSLAMs are typically installed in a Telco central office (CO) or similar location, and provide the required ATM link to numerous xDSL (Digital Subscriber Line) modems. The Digital Subscriber Line solves the bandwidth bottleneck to homes or businesses, over existing twisted pair old copper telephone lines (POTS). Loading coils, typically present in those lines, must be removed, because they do not allow xDSL to be transported. This section of the network is known as the *Last Mile Solution* in digital data services.

The DSLAM Reference Design presents a multi-device entity that comprises rack-mounted shelves with 6U high plug-in cards. It also provides an overview of the DSLAM architecture based on the VORTEX chipset. The VORTEX chipset includes the following:

- PM7350 S/UNI-DUPLEX multiplexer

- PM7351 S/UNI-VORTEX multiplexer

- PM7326 S/UNI-APEX traffic manager (switch)

- Also, PM7324 S/UNI-ATLAS ATM layer solution (traffic policing device), which supplements VORTEX Chipset.

The DSLAM Reference Design shelf is a stand-alone entity that shows how the PMC-Sierra VORTEX chipset operates. The PMC-Sierra VORTEX chipset provides a cost-effective and compact solution for manufacturers of high-speed Internet access equipment.

## 1.2. DSLAM Reference Design Features

The DSLAM Reference Design features:

- traffic management, policing and OAM functionality with the S/UNI-APEX and S/UNI-ATLAS

- in-system demonstration of PMC-Sierra's 8- or 16-bit ANY-PHY Interface (extended Utopia L2, at up to 50 MHz clock rate)

- high-speed Low Voltage Differential Signaling (LVDS) interface up to 200 Mb/s

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

- 1:1 protection switching between the Core Card, the WAN up-link cards and the Line Cards

- 8 kHz synchronization method for the whole DSLAM system, including loop entities

- hot swap capability on all cards: power rails hot swap on WAN and Line Cards; power rails hot swap and software ready hot swap on Core Card.

## 1.3. Example of a DSLAM Connection in an ADSL Application

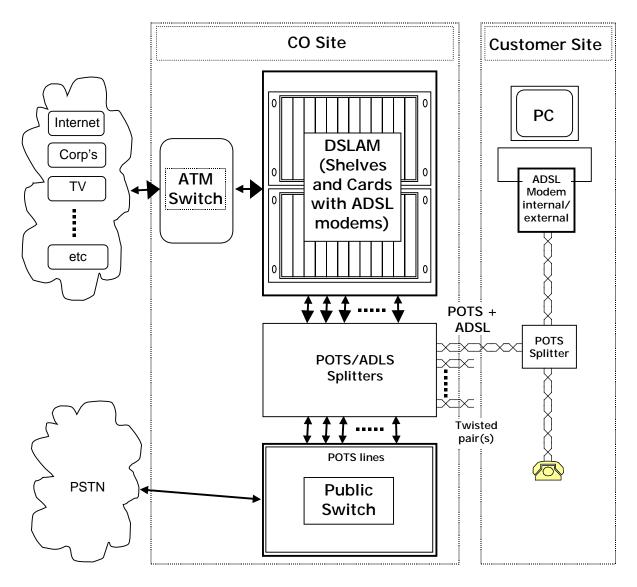

Figure 1 shows an example of a DSLAM connection in an ADSL application.

Figure 1. DSLAM-ADSL in the Public Telephone/Data Network

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

In the example, the DSLAM shelf is associated with a Public Switch of a telephony network. The downstream data flows from an ATM switch that connects different service providers to the xDSL network. POTS and xDSL signals are delivered to the customer over a twisted pair.

## 1.4. DSLAM Block Diagram

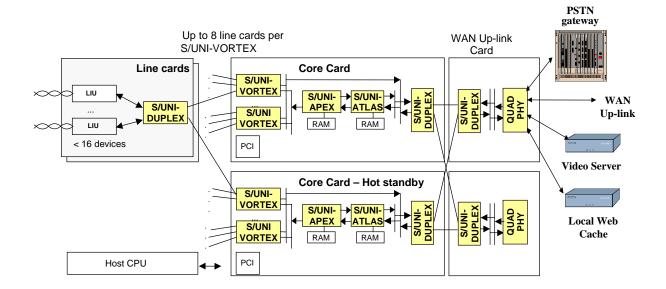

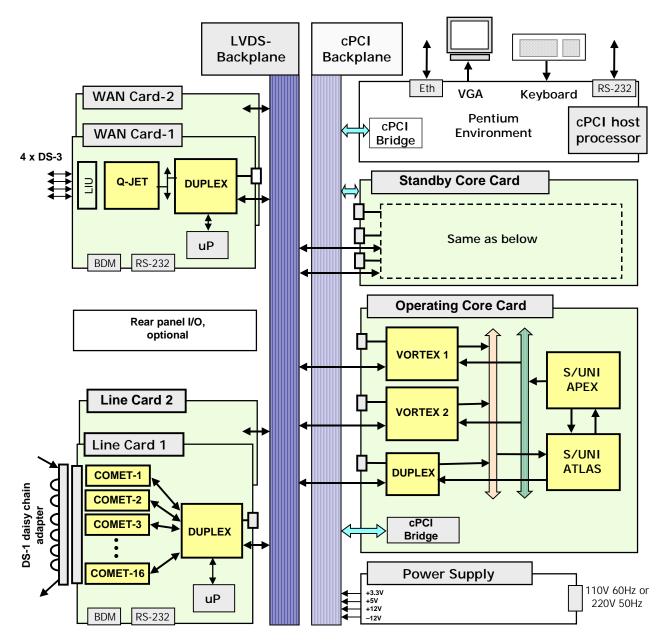

Figure 2 shows a typical application for the S/UNI-DUPLEX, S/UNI-VORTEX, S/UNI-APEX, and S/UNI-ATLAS. The system shows two Core Cards operating in a protection mode. One of the cards is in hot standby mode.

The DSLAM Reference Design Line Card supports sixteen LIU devices. The S/UNI-DUPLEX loop side that interfaces with the LIU is set to Data-and-clock. The WAN Card supports the S/UNI-DUPLEX with the Utopia L2 interface towards the Quad-PHY and WAN direction.

Figure 2. DSLAM Overview

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## 1.5. CompactPCI Shelves

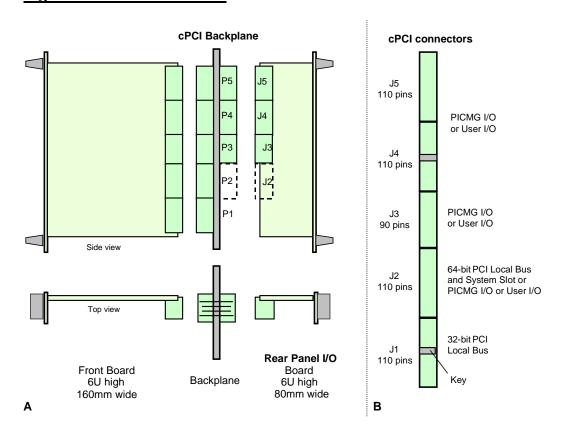

The DSLAM Reference Design is based on the CompactPCI shelf form factor.

## 1.5.1. Shelf Types

Vendors provide various CompactPCI shelves, which are typically described as development shelves, system shelves, and portable shelves. Development shelves usually support four to eight card slots. System shelves usually support eight or sixteen card slots. Portable shelves support four to eight slots, and focus on developing a package that is easy to transport and provides protection against mechanical damage.

#### 1.5.2. DSLAM Shelf

The DSLAM Reference Design shelf is built as a development shelf. The development shelf is basically a skeleton of the shelf, equipped with a backplane, a switching power supply, and minimal metal work, which allows for easier access to components for troubleshooting and development.

The DSLAM Reference Design cards and shelves are scalable entities with demonstration capability of as little as three cards in a single shelf, and a maximum size of sixteen Line cards, two WAN Cards and two Core Cards. 19-inch rack-mounted cPCI shelves with 20 cards. A single shelf solution shows limited functionality, but is built for ease of system demonstration. Each DSLAM Reference Design shelf, accommodating a Core Card, is equipped with a CPU card. This CPU is the PCI bus host processor.

The current DSLAM design uses a custom-made backplane (LVDS-backplane) to optimize connectivity for LVDS interfaces. This design may restrict some of the DSLAM cards to work on other types of the cPCI shelves. This Reference Design is an excellent example of a DSLAM entity, which proves DSLAM architecture can be used by customers as a starting point for building larger systems.

#### 1.5.3. Rear Panel I/O

The custom LVDS-backplane is equipped with a rear panel I/O conenctor, at the first slot, allowing connection of periipherals for the host processor card. An example of the Rear Panel I/O interface is described in APPENDIX – A: REAR PANEL I/O.

PMC-1990832 ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## 1.5.4. Hot Swap on cPCI backplane

The hot swap functionality is another important features built into the cPCI shelves. The cPCI connectors have staged pins and a mechanical switch built into the extraction handle. This enables a card in an operating shelf to be inserted or removed without data corruption to the system. The DSLAM Reference Design cards are hot swap compatible. The cards are hot-swap-ready as stated in the *Hot Swap Specification* (Draft) with limited functionality on backplane connectors. The WAN Card and Line Cards use only +5 V rails on the cPCI backplane and have the appropriate voltage/current ramping serial MOSFET transistors. Those cards have no PCI bus interface. The Core Card is equipped with +5 V and +3.3 V voltage/current ramping serial MOSFETs. The card is equipped with a precharging network on the PCI bus, as stated in the *Hot Swap Specification* (Draft). The Core Card is equipped with an ejector microswitch, blue LED, and active ENUM# line, making card hardware and softwarehot-swap-ready.

## 1.6. DSLAM Reference Design Package

Issue 3\* of the DSLAM System Reference Design package includes the following contents:

- DSLAM System Reference Design document

- Reference Design documents for each card

- Schematics and layout for each card, accompanied with a bill of material

- Software driver for each PMC-Sierra's chip on the Core Card, VORTEX Chipset Driver (board level driver or metadriver) and some test routines.

#### 1.7. VORTEX Chipset Development Kits

The VORTEX Chipset Development Kits are available on request from PMC-Sierra, Inc., while quantity lasts. Two types of development sets are available: KitA – the Core Card only, and KitB - the Core Card and WAN Card.

<sup>\*</sup> See the PMC-Sierra web site for the latest documents.

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## 2. DSLAM REFERENCE DESIGN SHELF

This section introduces Core Card architecture, DSLAM Reference Design architecture, and a physical concept of the DSLAM Reference Design.

## 2.1. DSLAM Reference Design Architecture

The DSLAM Reference Design comprises four separate, application-specific card types:

- Core Card

- Line Card

- Wan Card and

- LVDS-backplane

#### 2.1.1. DSLAM Reference Design Architecture Block Diagram

Figure 3 shows the block diagram that depicts the basics of this DSLAM Reference Design Shelf.

The very basic DSLAM configuration supported with this Reference Design consists of two Line Cards, two Core Cards, and two WAN Cards. The backplane allows a number of LVDS interfaces to be run with copper traces. Other LVDS connections can be done with external cables.

Ports P[1] on both WAN Cards are connected to corresponding ports P[1] on Core Cards. The Core Card can switch between the two WAN Cards by toggling S/UNI-DUPLEX ports. On the Loop side, Line Cards switch between Core Cards also by toggling S/UNI-DUPLEX ports.

The preferred interface between Line Cards and Core Cards, via the backplane, is through the S/UNI-VORTEX-1 (ports 1 and 2) on both Core Cards. A system built with more Line Cards uses up the remaining ports on S/UNI-VORTEX-1 and then on S/UNI-VORTEX-2.

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

LVDS over LVDS over Core Card 1 Backplane Backplane Operational VORTEX-1 DUPLEX P1 S/UNI-S/UNI-P2 **APEX ATLAS** P1 **X** P2 **A** P8 P1 Line Card 1 VORTEX-2 P2 SRAM **SRAM** P8 WAN Card 1 DUPLEX P1 P2 S/UNI-S/UNI-**APEX ATLAS** DUPLEX P'8 Р1 👸 P1 Line Card 2 P2 **A** P2 VORTEX-2 P2 SRAM **SRAM** WAN Card 2 P8 Core Card 2 Hot Standby DUPLEX LVDS over Cable Optional equipment mounted on Line Card 16 additional shelf

Figure 3. DSLAM Shelf Architecture Block Diagram

# 2.1.2. Core Card Architecture Block Diagram

This Reference Design is built around a single S/UNI-ATLAS with the S/UNI-APEX architecture used on the Core Card.

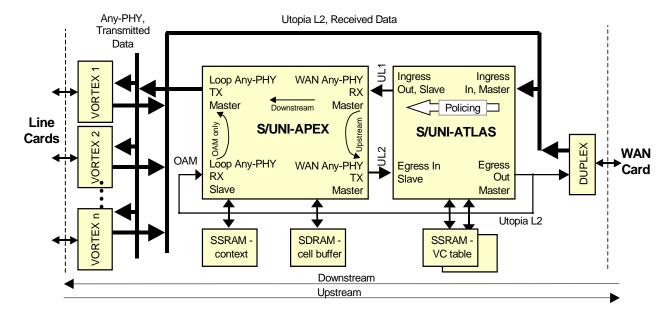

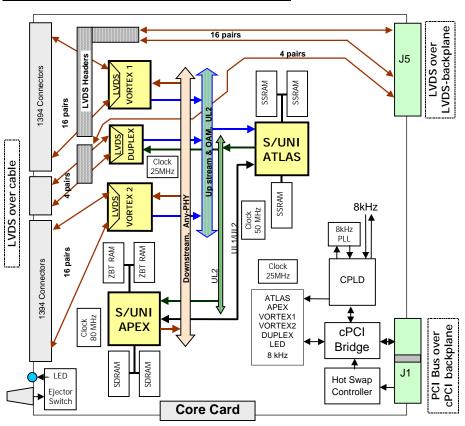

Figure 4 shows the Reference Design Core Card with the VORTEX chipset architecture.

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

Figure 4. Core Card Architecture Block Diagram

The S/UNI-APEX and S/UNI-ATLAS are the focus point of this design. The downstream and upstream cells interfaces with the S/UNI-ATLAS through the same "Ingress In" port. The S/UNI-ATLAS communicates with the S/UNI-APEX via the UL1 port, in the Ingress direction. The "Loop Any-PHY Rx Slave" port on the S/UNI-APEX is connected to the WAN direction "Egress Out", allowing flow of the OAM cells. The S/UNI-APEX switches data to the "Loop Any-PHY TX" or to the "WAN Any-PHY TX" ports as required for the cell destination. The Core Card communicates with Line Cards through a set of S/UNI-VORTEX devices. The interface to the network is done through the S/UNI-DUPLEX, followed by a WAN Card. The large size of the RAMs associated with the S/UNI-APEX and S/UNI-ATLAS supports ATM traffic management, traffic policing, OAM cell flow, and cell switching up to 2048 ports. For more information about the Core Card, see document [1].

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## 2.2. DSLAM Shelf Configuration

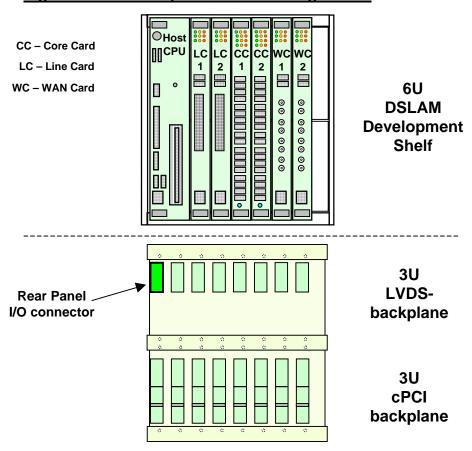

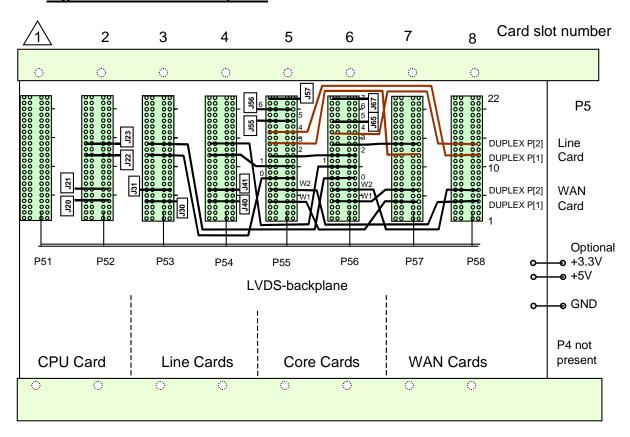

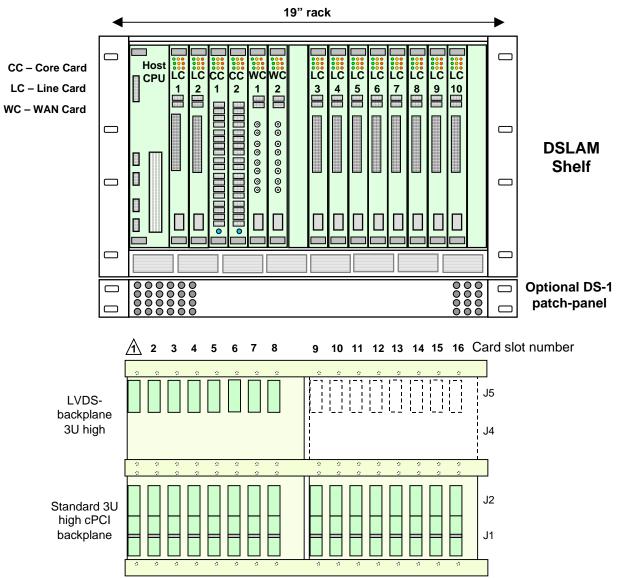

Figure 5 shows an example of card placement on the DSLAM Reference Design development shelf.

Figure 5. Development Shelf Configuration

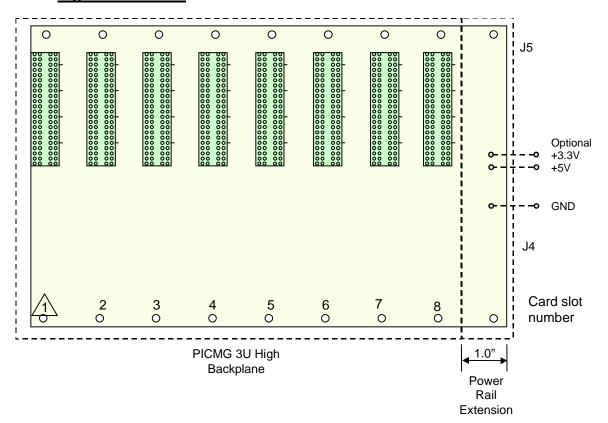

The shelf is shown with a host processor card, two Line Cards (LC1, LC2), two Core Cards (CC1, CC2), and two WAN Cards (WC1, WC2). Backplanes are shown below the shelf. The upper 3U high board is a custom made entity that supports LVDS over the backplane. This board is called the "LVDS-backplane" throughout this document. The lower 3U high standard cPCI backplane supports PCI bus and power lines, and it is purchased on the market. The DSLAM LVDS-backplane is developed by PMC-Sierra, Inc., and it is a custom made design, specific to this DSLAM Reference Design.

The DSLAM Shelf may require forced air cooling system, if all cards are placed on the shelf. The host processor card may have forced airflow cooling at the Intel Pentium<sup>™</sup>.

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## 2.2.1. DSLAM System Block Diagram

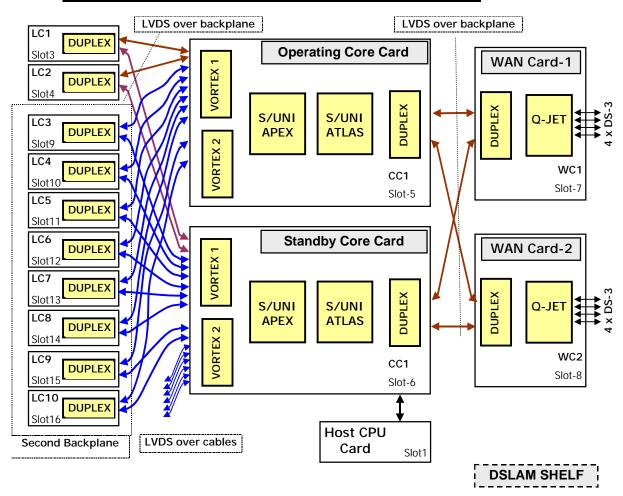

Figure 6 shows block diagram of an example DSLAM Reference Design Shelf.

Figure 6. DSLAM Reference Design Shelf Block Diagram

The DSLAM Reference Design shelf assembly shown in Figure 5 and the shelf configuration shown in Figure 6 supports the following PMC-Sierra devices:

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

S/UNI-DUPLEX, S/UNI-VORTEX, S/UNI-APEX, S/UNI-ATLAS, S/UNI-QJET, and COMET.

The DSLAM Shelf includes the following Reference Design cards:

- Operating Core Card with two S/UNI-VORTEX'es, S/UNI-DUPLEX, S/UNI-ATLAS, and S/UNI-APEX.

- Standby Core Card same as the Operating Core Card

- Line Card 1-2 with 16 COMETs and one S/UNI-DUPLEX on each card

- WAN Card 1-2 with S/UNI-DUPLEX and S/UNI-QJET

- DSLAM Backplane custom backplane with J4 and J5

The purchased off-the-shelf components are:

ISSUE 4

- 6U high, aluminium shelf

- CPU card based on the 233 MHz MMX Intel Pentium

- cPCI backplane with J1 and J2 connectors

- Power Supply

- Peripheral devices: VGA monitor and keyboard

- during development phase, additional PC and network server were used (PC with a Tcl/Tk environment interfacing with the host CPU through the serial port; the Lab Server allowing the download of metadriver test routines through the Ethernet port).

The clock-and-data interface on the S/UNI-DUPLEX is shown with sixteen COMETs (bit aligned serial data and clock). The Utopia L2 interface on the S/UNI-DUPLEX is shown with S/UNI-QJET on the WAN Card.

Both Core Cards are assembled and programmed to be identical. Core Cards interface with the CPU card via a 32-bit cPCI bus. The LVDS interface on Core Cards can be connected to the LVDS-backplane via the jumper field, which is set manually before card insertion. The jumper field configuration is shown in the schematic associated with the Core Card Reference Design document [1]. Core Cards can be placed into slots 5 or 6 on the DSLAM shelf and must be associated with host CPU card at slot 1.

The CPU card can only be at slot 1. This slot is always marked with a "\Delta" (triangle).

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

Line Cards 1 and 2 are identical. Cards can be placed primarily into slots 3 and 4, and, optionally, into any slot. The LVDS interface (on the Line Card) can be programmed for the backplane, if the Core Card is present on the shelf.

The WAN Cards are identical. Cards can be placed primarily into slot 7 or 8, and optionally into any slot. Slots 7 and 8 have additional WAN LVDS connections over the backplane to Core Card1 or Core Card2.

LVDS interface configuration on all cards is very flexible and can be configured to LVDS interface over the backplane only, over the front cables only, or mixed connection partially over the backplane and partially over cables. Any card can connect to another shelf over the front cable LVDS interface.

The jumper field configuration for Line Card and WAN Card are shown in corresponding schematics documents [2] and [3].

#### 2.2.2. Front Plates on DSLAM Cards

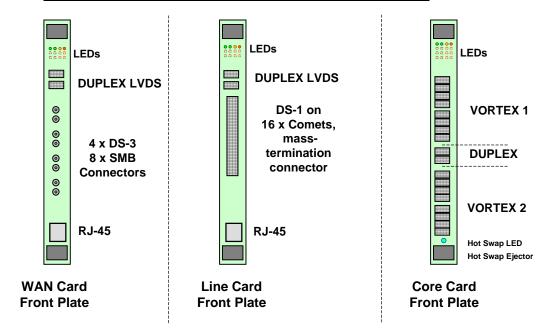

The front plates on each DSLAM card have external dimensions as specified in cPCI document [13]. Plates are mechanically customized for each card.

Figure 7 shows an example of the front plates.

Figure 7. Front Plate for WAN, LC and CC Cards

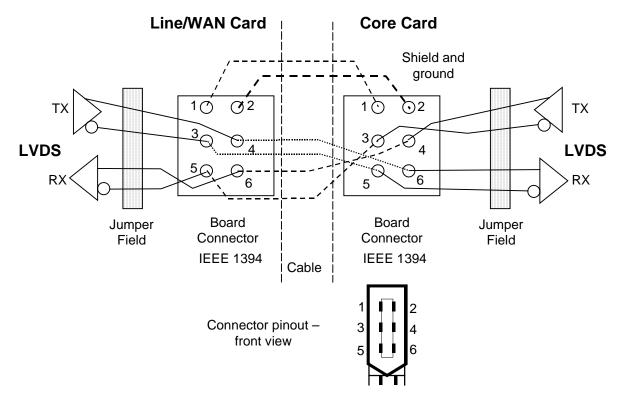

The WAN Card is equipped with eight SMB connectors supporting four DS-3 interfaces. The front plate has a cutout for two IEEE 1394 connectors for the

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

S/UNI-DUPLEX LVDS. The RJ-45 connector is used for the microprocessor serial port interface. Light emitting diodes (LEDs) show basic Card status. LEDs are placed at the top of the plate for best visibility.

The Line Card is equipped with a mass-termination connector that supports sixteen DS-1/E1 interfaces. The DS-1/E1 lines are connected in a daisy chain configuration with a custom connector sub-assembly. For more information, see the Line Card Reference Design document [2]. DS-1/E1 signals can be branched out of the mass-termination into individual DS-1/E1 bantam connectors with a cable harness or through a rack-mounted patch-panel. The Line Card is also equipped with two IEEE 1394 connectors that supports the S/UNI-DUPLEX LVDS connections. The RJ-45 connector is used for microprocessor serial port interface. The LEDs show basic Card status.

The Core Card is equipped with eighteen IEEE 1394 connectors (FireWire). The top eight connectors support S/UNI-VORTEX-1 LVDS. The center pair supports the S/UNI-DUPLEX LVDS, and the lower eight connectors support S/UNI-VORTEX-2 LVDS. The LEDs show basic status of the Core Card. The blue LED and lower ejection handle with a micro-switch are used for hot swap compatibility.

The 8 kHz timing reference (stratum clock) is supported only through internal header connectors, not accessible at the front panel.

The aluminum front plates are covered with silkscreen print. Labels identify connectors, LEDs, Card type, and manufacturer (PMC-Sierra, Inc.).

## 2.3. LVDS Interface

The LVDS interface is a key element in the DSLAM application using a highspeed serial communication link that runs up to 200 Mbps.

## 2.3.1. LVDS Introduction

Over the decades, the use of 5V power supply voltages has allowed simple interfacing between logic circuits of different technologies and manufacturers. However, lower supply voltages are required as integrated circuit technology migrates to a finer geometry. At the same time, the data rate has to be increased. Reducing supply voltages also reduces the power required to operate high-density IC circuits and therefore reduces the amount of heat that high-density circuits dissipate.

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

A perfect example of a reduced supply voltage and reduced logic voltage swing is the LVDS. The LVDS physical interface uses a 400mV signal swing around an offset voltage of 1.2V. In comparison, ECL and PECL signals use a 800mV signal swing and depend more on supply voltages. ECL requires a negative supply and PECL is referenced from the positive power supply rail (Vcc). Ground Referenced Impedance Matched (GRIM) Low Voltage Differential Signaling (GLVDS) is another method of fast data transfer with low power consumption and dissipation. GLVDS uses a 500mV power supply to provide a 250mV signal swing; however, the standards outlined here need verification.

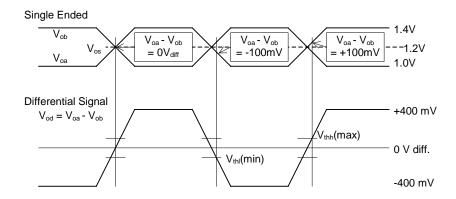

Figure 8 shows the differential voltage swing for different low voltage logic signals.

+5V **PECL** 3.3V 2.5V 3.3V PFCI 1.8V LVDS **GLVDS** 4.0 2.0 1.0 0.8 0.35 0.15 0.1 Microns 1996 2000 2004 1980 1984 1988 1992 Year

Figure 8. Differential Voltage Swings

The S/UNI-DUPLEX and S/UNI-VORTEX devices both use the LVDS interface to communicate serial data at speeds of up to 200 Mbps.

Two standards define LVDS:

- IEEE P1596.3 Low Voltage Differential Signaling (LVDS) for Scalable Coherent Interface (SCI)

- ANSI/TIA/EIA-644 Electrical Characteristics of LVDS.

Both standards define the electrical characteristics of LVDS. The IEEE standard defines encoding for packet switching in the SCI protocol. Also, each standard is specified as physical media independent, which means the interface will operate properly as long as the media delivers the signal to the receiver within the specified noise margin and skew tolerance range.

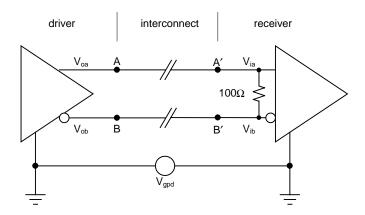

Figure 9 shows a typical LVDS interface.

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## Figure 9. LVDS Interface

Each differential pair is a point-to-point connection and consists of a driver, interconnect and receiver. The low voltage swing driver signals (400mV single-ended maximum) enable high-speed operation and minimize power dissipation. Differential signals provide the low voltage swing with adequate noise margin and a large reduction in power dissipation. The large reduction in power dissipation allows for the integration of multiple interface drivers and receivers in the same integrated circuit. This helps to reduce PCB real estate and costs. The S/UNI-VORTEX supports eight LVDS interfaces.

IEEE P1596.3-1995 allows for two variations of LVDS specifications; General Purpose Link and Reduced Range Link. The significant difference between the two specifications is the allowed ground potential difference (Vgpd). The General Purpose Link specifies the maximum Vgpd at 925mV while the reduced range link specifies the maximum Vgpd at 50mV. In effect, the reduced range link specification is directed towards links on PCBs or other similar environments where the ground potential difference is expected to remain below 50mV.

Figure 10 (below) shows two single-ended signals combined to create a differential pair. The single-ended Voa signal represents *true* and Vob is its *compliment* and the offset (common mode) voltage is 1.2V. The differential signal, Vod, results when the compliment is subtracted from the true signal.

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## Figure 10. Low Voltage Differential Signal Output levels

The peak-to-peak voltage swing across the LVDS differential pair is up to 800 mV. A single line swings with peak-to-peak amplitude up to 400 mV.

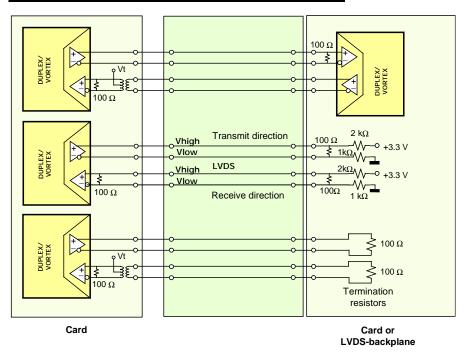

The differential receivers are capable of handling signal swings down to 100mV. A wide common mode range makes them compatible with LVDS signals. External termination resistors must be provided to match the cable impedance.

## 2.3.2. DSLAM High-Speed LVDS Serial Interface

The S/UNI-DUPLEX and S/UNI-VORTEX provides backplane interconnection through 100 to 200 Mbps serial links that use the LVDS standard. All data going to and coming from the cell processing on the Core Card are concentrated on these high-speed links. The LVDS transmitter/receiver supports UTP-5 cable lengths up to 10 m. Clock is transmitted and the receivers recover a local clock from the incoming data, to avoid clock skew issues. Transmitter outputs are internally terminated current mode drivers. Correct termination at the receiver provides appropriate signal levels.

Two bi-directional LVDS links are provided on the S/UNI-DUPLEX for redundancy. Each link is intended for routing to different Core Cards. Both LVDS transmitters carry identical traffic except for internally generated overhead. Both links are frequency locked to the single input reference clock, although their phase is not guaranteed to match. At the S/UNI-DUPLEX, LVDS receivers clock recovery and cell delineation are always active for both receivers to allow a quick switch to the redundant Core Card with minimal cell loss. The S/UNI-VORTEX LVDS interface recovers clock and data on each link independently. The transmit data on each port is synchronous to the same reference clock. The data edges are not guarantied to have the same phase. The cell delineation phase is different on each transmit and receive ports.

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

The internal transmit clock is synthesized from a 12.5 MHz to 25 MHz clock. The resulting data bit rate is eight times the frequency of the REFCLK input. All jitter below 1 MHz on REFCLK is passed unattenuated to the TXD1+/- and TXD2+/- outputs. The design of the loop filter and PLL is optimized for minimum intrinsic jitter. With a jitter free reference input and a low noise board layout, the intrinsic jitter is typically less than 0.01 UI RMS and 0.10 UI peak-to-peak, when measured using a band pass filter with 12 kHz and 1.3 MHz cutoff frequencies.

The receivers monitor for loss of signal (LOS) on the links. LOS is declared in 2048 bit periods (13.2  $\mu$ s at 155.52 Mb/s) without a signal transition in the scrambled data. Consequently, a status bit is set, a maskable interrupt is asserted, and the RDI (Remote Defect Indication) codeword is sent repetitively in the BOC bit in the corresponding downstream link. The LOS indication is cleared when a signal transition has occurred in each of the 16 consecutive intervals of 16 bit periods each.

Clock recovery is performed by a digital locked loop (DLL). The implementation is robust against operating condition variations and power supply noise. The receive link is constrained to be within 100 ppm of eight times the REFCLK frequency.

Both the S/UNI-DUPLEX and S/UNI-VORTEX provide LVDS loopback capability to aid in system diagnostics. The metallic loopback routes high-speed serial receive data to the transmitter. Both devices also provide diagnostic loopback, which allows loopback of data on the drop side. The loopbacks can be enabled individually or simultaneously, and each link can be looped back independent of the other.

The DSLAM Reference Design Line and WAN Cards have a hardwired provision for remote reset through the RSTBOB pin on the S/UNI-DUPLEX device. The reset function is one of the pre-programmed patterns. Other functionality is not implemented in this issue of the Reference Design.

#### NOTE:

The LVDS interface is fully hot swap compatible. The LVDS transmitters and receivers can stay active while other card is hot swap. Writing to corresponding registers on the S/UNI-DUPLEX or S/UNI-VORTEX can disable transmitters. IMPORTANT - Proper register write sequence is required to ensure cell transfer. The sequence is implemented in the VORTEX Chipset driver files vcs\_api1.c and dpx.c. The most critical is to make sure the OCAEN bit in register 0x0A in the S/UNI-DUPLEX stays disabled until S/UNI-ATLAS polling is enabled. The OCAEN is set to 1 as the very last write, enabling cell transfer from the S/UNI-DUPLEX at that interface. Software designers are required to observe sequencing in their drivers.

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## 2.3.3. ATM Cell on High-speed Link

The high-speed link supports a proprietary protocol with cells similar to the ATM cells with additional octets carrying interface overhead.

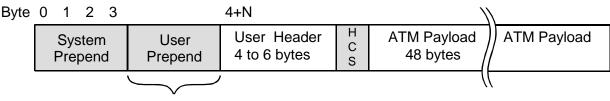

The serial LVDS link carries ATM cells with prepended bytes. Figure 11 shows the cell format.

Figure 11. High-Speed Serial Link Data Structure

N bytes, where N = 0 or 2

The S/UNI-DUPLEX and S/UNI-VORTEX appends the first four bytes and the Header Check Sequence (HCS) byte in LVDS transmit directions. At the receiver, the high-speed cell is stripped off the prepend and the remainder of the bytes in the data structure is transferred transparently. The high-speed transmit bytes are serialized most significant bit first. The bit stream is a simple concatenation of the extended cells. Cell rate decoupling is accomplished through introduction of stuff cells.

The transmitter inserts a correct CRC-8 that protects both the ATM cell header and prepended bytes in the HCS byte. Cells with an HCS in error are counted and then discarded. The receiver also uses the HCS byte for determining cell delineation. Failure to establish cell alignment results in a loss of the cell delineation (LCD) alarm. The entire bit stream is scrambled with a  $x^{43}$  + 1 self-synchronous scrambler. TABLE 1 summarizes the contents of the system prepended bytes.

TABLE 1. Prepended Fields

| Byte | Bits | Mnemonic | Description |

|------|------|----------|-------------|

|------|------|----------|-------------|

ISSUE 4

| Byte | Bits       | Mnemonic            | Description                                                                                                                                                                                                                                                                                                                                                                         |

|------|------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 7:0<br>7:0 | CA[15:8]<br>CA[7:0] | The CA[15:0] bits carry per-PHY flow control information in the upstream direction. To support 32 PHYs, the status for each PHY is sent every other cell; the CASEL indicates which half is represented. If CASEL is logic 0, CA[15:0] corresponds to those PHYs with addresses 0 through 15. If CASEL is logic 1, CA[15:0] corresponds to those PHYs with addresses 16 through 31. |

|      |            |                     | In the downstream direction, CA[15:0] communicates congestion of the upstream entity. The encoding is identical to the upstream direction. A logic 0 indicates the far end can accept no more cells for a specific logical channel. A logic 1 indicates the S/UNI-DUPLEX is free to send queued traffic for that logical channel immediately.                                       |

|      |            |                     | In the event of an errored header (as detected by an incorrect HCS), the CA bits will be assumed to be all zero. This ensures cells are not transmitted for which there is no buffer space.                                                                                                                                                                                         |

| 2    | 7          | CASEL               | The state of the CA select bit determines which half of the PHY devices the CA[15:0] bits correspond to. CASEL toggles with each cell transmitted.                                                                                                                                                                                                                                  |

| 2    | 6          | UPCA                | The UPCA bit carries flow control information for the microprocessor control channel. If this bit is one, control channel cells may be transferred.                                                                                                                                                                                                                                 |

|      |            |                     | In the event of an errored header, the UPCA bit will be assumed to be zero. This ensures cells are not transmitted for which there is no buffer space.                                                                                                                                                                                                                              |

| 2    | 5:0        | PHYID               | The PHY identifier determines to which PHY a cell is destined in the downstream direction and from which PHY it came in the upstream direction. It also indicates whether the cell is a stuff or control channel cell. The field is encoded as follows:                                                                                                                             |

|      |            |                     | "111111" – Stuff cell provided for cell rate decoupling. The payload carries no useful data and the cell shall be discarded.                                                                                                                                                                                                                                                        |

|      |            |                     | "11110" – Control channel cell. On the transmit serial link, PHYID equals this value for all cells inserted through the Microprocessor Cell Buffer. All cells received on the serial link with this encoding will be routed to the local microprocessor.                                                                                                                            |

|      |            |                     | "100000" to "111101" – Reserved                                                                                                                                                                                                                                                                                                                                                     |

|      |            |                     | "000000" to "011111" - Logical channel index for the PHY devices.                                                                                                                                                                                                                                                                                                                   |

| 3    | 7          | вос                 | The Bit Oriented Code (BOC) bit position carries a repeating 16 pattern that encodes one of 63 possible code words used for remote control and status reporting. Five codes are predefined to represent a remote defect, a loopback activate request, a loopback deactivate                                                                                                         |

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

| Byte | Bits | Mnemonic  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      |           | request, a reset activate request, and a reset deactivate request.  The remaining codes are either reserved or user defined. The receiver ensures the pattern is the same for 10 (default) or 5 repetitions before validating a new code word.  For more information, see the data sheet section.                                                                                                                                                                                                                                         |

| 3    | 6    | ACTIVE    | The link active bit indicates which of the redundant links is currently chosen. The S/UNI-DUPLEX will switch to the link that contains a one in this location for at least three consecutive cells. The local microprocessor can override this selection. If both links present a one in this location, the selection remains unchanged. To confirm which link is active, the transmitted ACTIVE bit will be a one if the associated receive link is selected.  In the event of a header in error, the previous ACTIVE value is retained. |

| 3    | 5:0  | TREF[5:0] | The timing reference encodes an 8 kHz signal inband that is independent of the serial bit rate.  The TREF[5:0] binary value represents the number of high-speed link bytes after the one in the timing reference is inferred. An all ones value indicates no timing mark is associated with this cell.                                                                                                                                                                                                                                    |

## 2.3.4. Inband Communication Channel Over the High-speed Link

The Inband Communication Channel (ICC) allows building custom communication channel between two DSLAM entities, and in turn, the whole DSLAM system can be in-system reprogrammed and controlled from a single processing center.

The channel allows insertion, identification, and removal of cells at Any-PHY/SCI-PHY interfaces on both sides of the LVDS link. The ICC channel is dedicated entirely to custom massages transmitted across LVDS link between two cards interfacing with S/UNI-VORTEX to S/UNI-DUPLEX, or S/UNI-DUPLEX to S/UNI-DUPLEX.

It is assumed that the microprocessor entities on both sides of the connection are running a reliable communications protocol.

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

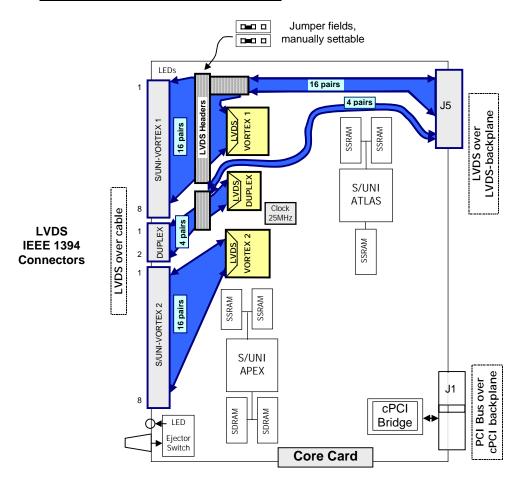

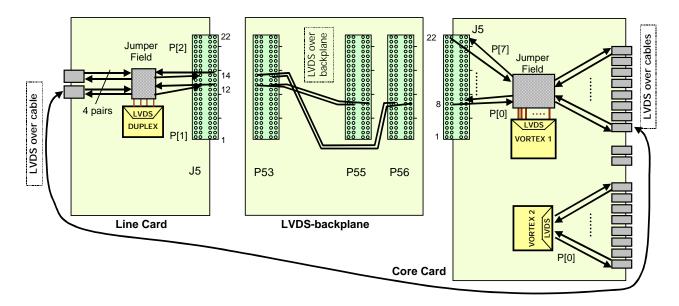

# 2.3.5. Example of LVDS Layout on Core Card

The LVDS lines on the Core Card are run through jumper fields and allow an interface to the backplane or to the front panel connectors. Figure 12 shows components that support LVDS on the Core Card.

Figure 12. LVDS on Core Card

The LVDS interface on the S/UNI-VORTEX-1 and the S/UNI-DUPLEX can be connected to J5 or to front panel IEEE 1394 connectors. S/UNI-VORTEX-2 provides an interface to the front panel only. The total number of LVDS traces running through J5 to the DSLAM backplane is 40. The LVDS traces to the J5 connector are relatively long, and care is taken to avoid crosstalk to and from digital lines. Front plate connectors are FireWire type (IEEE 1394) designed to handle LVDS up to 400 Mb/s.

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## 2.4. 8kHz Interface and System Synchronization

The Reference Design uses an 8 kHz clock as a means of system synchronization (stratum clock). The S/UNI-DUPLEX\_S/UNI-VORTEX pair transports the 8 kHz time reference over the LVDS connection between different hardware entities in the DSLAM system. The synchronization clock is not restricted to 8 kHz; however, the phase lock loop (PLL)—used to remove jitter and chosen for this design—is optimized for 8 kHz.

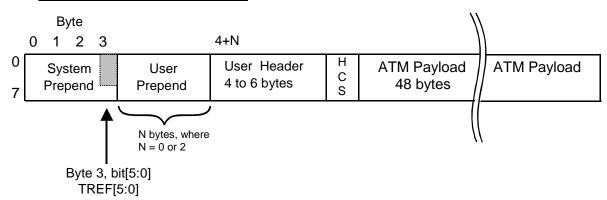

The time reference is encoded in the third byte of the prepend that is attached to a modified ATM cell and transmitted over the serial high-speed LVDS connection. Figure 13 shows the LVDS ATM-like cell.

Figure 13. Prepend Fields

The TREF[5:0] binary value represents the number of high-speed LVDS bytes after byte number 3 (shown above) at which the timing reference (can be 8 kHz) is inferred. An all-ones value indicates no timing mark is associated with this cell.

At the receiver site the inherent jitter is at  $\pm$  one octet. For example, at 200 MHz it is  $\pm$ 40 ns. A phase lock loop (PLL) circuitry is required to filter that jitter. At the receive site the positive edge is timed by a counter starting at byte-3 and counting down value of received TREF[5:0]. When the count-down is at zero (hex 00), the RX8K is toggled high for a short period of time.

The timing channel is not limited to 8 kHz, and any clock frequency lower than the cell rate can be encoded. The encoded timing reference is independent of the serial LVDS link bit rate.

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

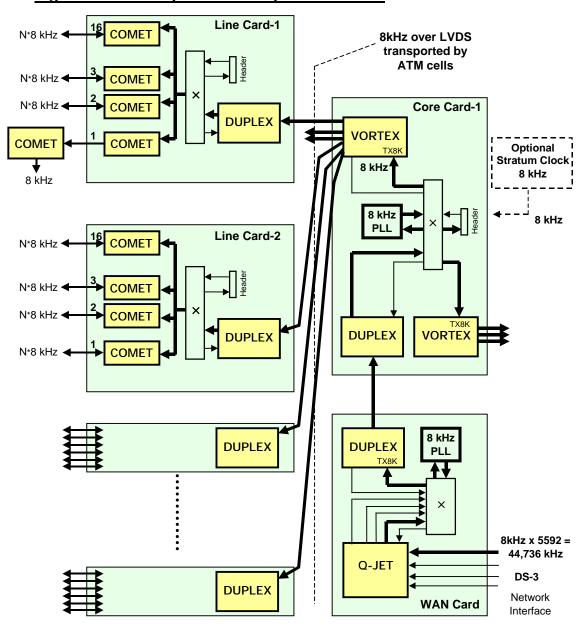

Figure 14 shows an example of the 8 kHz DSLAM network synchronization.

Figure 14. Example of 8kHz Synchronization

A brief description of the circuit is as follows. The DSLAM system can be synchronized to the network interface signal, shown in the lower-right corner of the diagram above, or to the Stratum Clock fed to the Core Card. Let's choose the network interface synchronization path, where the DSLAM entity is synchronized to the DS-3 line that interfaces through the Q-JET. The Q-JET outputs four 8 kHz signals. One of them must go through the 8kHz PLL to get rid

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

of the jitter, before it is fed to the S/UNI-DUPLEX pin TX8K. The S/UNI-DUPLEX encodes the 8 kHz clock into the serial LVDS stream (prepend TREF[5:0]) and sends it over the high-speed LVDS connection to the Core Card. The Core Card runs the clock through the PLL and distributes the signal to all S/UNI-VORTEX multiplexers. Each S/UNI-VORTEX again encodes the 8 kHz clock into prepend and sends it over the LVDS interface to all Line Cards. The Line Cards have no 8 kHz PLLs as the COMETs have a built-in dejittering circuit. The received 8 kHz pulses are distributed to all COMETs. Every DS-1/E1 line interface can be frequency synchronized to the network interface signal at the WAN Card.

The Core Card is equipped with a pair of header connectors that allows the 8 kHz interface (headers accessible on the PCB only) to be tested. In the receive direction, the 8 kHz clock can be derived from the network. In the transmit direction, the Core Card can be a source of the synchronization signal by connecting the Stratum 8 kHz Clock and reprogramming the clock flow on the appropriate cards.

The DSLAM shelf can be synchronized to any DS-1/E1 interface by reversing the flow of the 8 kHz clock from the chosen COMET towards the shelf entities. The switching action on the Line Card and WAN Card is controlled by a local microprocessor, which can communicate with the host CPU through the communication channel over the high-speed LVDS link (not implemented in this Reference Design). The Core Card 8 kHz path is controlled through the cPCI bridge.

The 8 kHz switching is executed on each board with a CPLD device, marked "X" on the block diagram.

The received 8 kHz clock on the S/UNI-VORTEX/S/UNI-DUPLEX pin RX8K is a pulse that lasts for 16 clock cycles on the clock at the LVDS connection. If LVDS is at 200 MHz, then the pulse is  $16 \times 5$  ns = 80 ns long, and repeats at 125 us ( $8 \times 10^{-5}$ ).

The protection switching between two Core Cards performed in our lab showed no adverse effect on the 8 kHz clock phase and frequency synchronization.. Assume that the 8 kHz signal is inserted to the TX8K input on the WAN Card 1 and distributed towards two Core Cards. – see Figure 3 for test circuit. The 8 kHz timing stamp on both high-speed links is encoded within  $\pm$  one octet. The LVDS links are running at the same synchronized clock speed (e.g. 200 MHz). Cells are send on both LVDS links with the same timing. Both Core Cards decode the time stamp within  $\pm$  one octet Both cards run the clock through the 8 kHz PLL and filter out that jitter. At this point, clocks on both Core Cards are phase-aligned with the jitter less than  $\pm$  one octet. Multiple protection switching did not create any noticeable phase jitter. Oscilloscope was not triggered with timing longer

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

than 125 us, and that points to not even a single loss of the time stamp. It is possible that limited number of switching actions did not allow to capture timing loss. The clocks are now fed to the S/UNI-VORTEX devices on each Core Card. The time stamp is received on the Line Card 1 from both Core Cards. The stamps on the high-speed links are aligned again within  $\pm$  one octet. Core Cards protection switching test was performed at PMC-Sierra. A number of protection switching actions did not create any noticeable phase jitter nor detected time stamp loss. The 8 kHz square wave at the Line card is always locked to the source at the WAN Card. If both clocks, one on the WAN-Line Card and other one on the Line Card were observed with an oscilloscope, the clocks were phase locked with minimum jitter, and a visible edge delay due to a signal propagation delay over the DSLAM entity.

Network synchronization and phase-frequency shift can be found in reference documents [5], [10], [11], and [12].

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## 3. REFERENCE DESIGN CARDS

This section presents a block diagram and a brief description for the Core Card, Line Card, and WAN Card.

## 3.1. Core Card

The Core Card is described in detail in the Core Card Reference Design document [1].

## 3.1.1. Block Diagram

The Core Card provides ATM traffic policing, ATM cell traffic management and ATM cell multiplexing. On the downstream side, the Core Card provides an interface through the S/UNI-VORTEX to the Line Cards. On the network side, the Core Card provides an interface through the S/UNI-DUPLEX to a WAN Card. Both interfaces are LVDS with data transfer up to 200 Mb/s.

The DSLAM Reference Design Core Card supports two S/UNI-VORTEX multiplexers, one S/UNI-APEX traffic manager, one S/UNI-ATLAS ATM layer solution device, and one S/UNI-DUPLEX multiplexer.

The LVDS interface to WAN Card and Line Card is accessible from the front panel or from the backplane. A set of headers is used for manual redirection of the interface.

The Core Card has no embedded microprocessor. Program control of the PMC-Sierra devices (VORTEX chipset) is achieved through the PCI bus host processor (CPU card). This is a register read/write and interrupt servicing interface. The cPCI bus does not carry payload data, which makes it easier for the CPU processor to maintain all DSLAM cards through the cPCI bus. However, cells can be entered to the network through the microprocessor interface on each VORTEX chipset device—the preferred gateway through the S/UNI-APEX.

The local bus is run in a multiplexing mode that supports primarily the S/UNI-APEX. Other devices are capable of communicating in that mode as well, with no data burst.

A CPLD is programmed for address and chip select control, and routing an 8 kHz signal.

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

The Core Card is equipped with a micro-switch that is activated by ejector handle action. The host CPU detects the insertion or removal of the card and takes proper action preventing PCI bus corruption.

Figure 15 shows the Core Card block diagram.

Figure 15. Core Card Block Diagram

The Reference Design supports scaled-down DSLAM application; therefore, the size of RAMs supporting the S/UNI-ATLAS may be downsized appropriately. The Core Card is designed to support up to 16 k connections. This requires a total of three 512 KB SSRAM chips associated with the S/UNI-ATLAS. SRAMs operate at 50 MHz.

The S/UNI-APEX RAM size depends on applications and should be calculated according to the S/UNI-APEX data sheet and programmers guide [9]. The Core Card may have assembled oversized RAM due to test purposes, RAM availability and other reasons – check Core Card Reference Design document [1]. Both RAMs operate at 80 MHz.

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

In the downstream direction, the S/UNI-APEX sends data to the S/UNI-VORTEX (and then to the Line Cards) through the Any-PHY interface that supports up to 800 Mbps and allows for 2048 channel addressing (logical PHYs). The data format is an ATM cell with a prepended single address word.

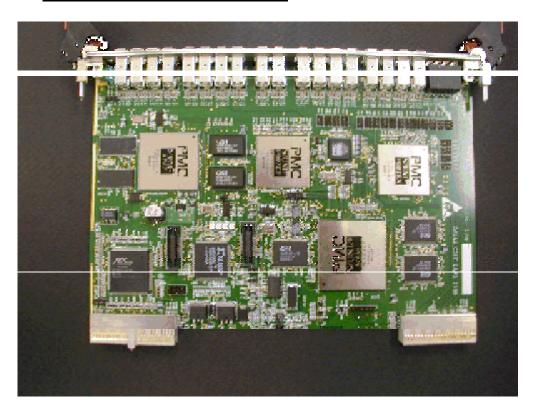

The Core Card picture is shown in Figure 16 below.

Figure 16. Core Card Top View

#### 3.1.2. Core Card Software/Firmware

There is no microprocessor (firmware) dedicated to the VORTEX Chipset control on the card. Power-up and operating functions must be downloaded through the cPCI bridge from the host processor card.

The Core Card has a small serial EPROM (SEEP) for the PCI bridge chip configuration.

A programmable CPLD supports local bus functionality, chip select, interrupts, LED control, and 8 kHz clock routing. The CPLD controls enabling the interrupt line to the PCI bridge.

REFERENCE DESIGN PMC-1990832

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

The host processor card monitors alarm and interrupt signals from the Core Card through the cPCI bridge.

The Core Card can provide bi-directional communication channel for software control to the Line Cards and WAN Cards. That channel may allow temporary or permanent remote reprogramming of the DSLAM entities, if the appropriate hardware and software resides on the WAN or Line Card.

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

# 3.2. WAN Card

This section provides a brief introduction to the WAN Card. The WAN Card is described in detail in the WAN Card Reference Design document [3].

# 3.2.1. Block Diagram

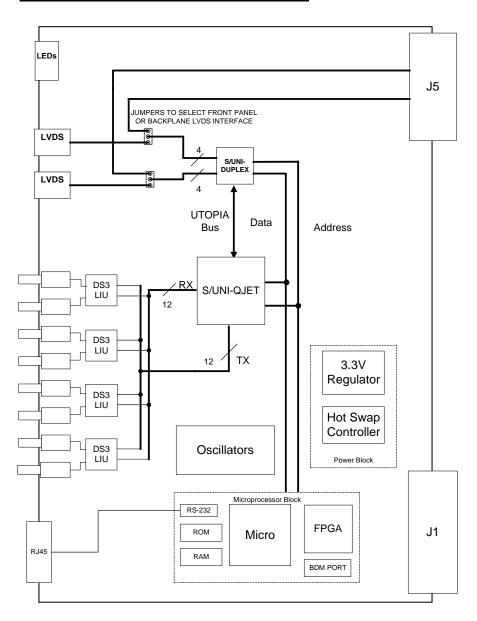

Figure 16 shows the block diagram forthe WAN Card.

Figure 17. WAN Card Block Diagram

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

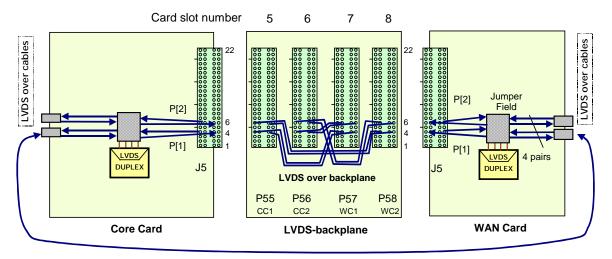

The S/UNI-DUPLEX provides an interface to the LVDS through the front or back connector. The S/UNI-DUPLEX is configured for a UTOPIA L2 bus, and it provides an interface to the S/UNI-QJET. Four DS3 line interfaces are on the network side of the S/UNI-QJET, allowing easy testing and enabling traffic generation. An LIU device is needed for the DS-3 physical interface. Eight SMB connectors allow the DS-3 to communicate over coaxial cable. Front plate also supports the LVDS connectors and the RJ-45 connector for microprocessor serial port.

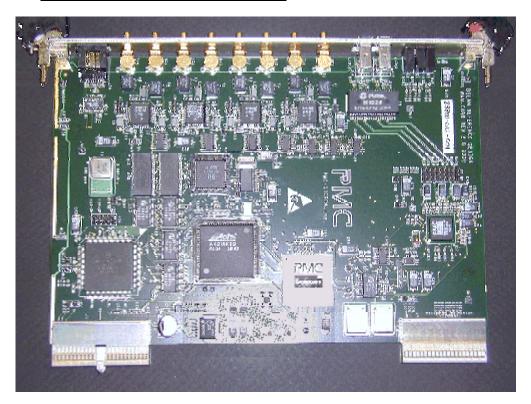

WAN Card picture is shown in Figure 18 below.

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

#### 3.2.2. WAN Card Software/Firmware

The boot-up and the default setup firmware for the VORTEX chipset resides on the WAN Card. Power-up and operating functions are executed by the embedded microprocessor.

The WAN Card is equipped with a push-button RESET switch accessible at the inside of the card, to avoid accidental activation while plugging connectors and other routine card/shelf maintenance. The RESET executes hardware reset to the entire board.

A BDM port on the card, accessible only from inside the shelf, allows the user to develop the software/firmware.

In general, DSLAM entities can be remotely controlled with Inband Communication Channel (ICC) run over high-speed link. Customer needs to implement communications protocol. The ICC communication may allow for remote card reprogramming, and alarm and interrupt servicing. Also, microprocessor re-boot to the card may be communicated through ICC.

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

# 3.3. Line Card

The Line Card is described in detail in the Line Card Reference Design document [2]. Figure 17 shows the Line Card block diagram.

## Figure 19. Line Card

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

The DSLAM Reference Design supports Line Cards with sixteen COMETs. The Line Card provides sixteen DS-1/E1 interfaces to visualize fan-out of the DSLAM user line interface and to use all sixteen data-and-clock interfaces on the S/UNI-DUPLEX. High-speed link ATM cells are demultiplexed with the S/UNI-DUPLEX and addressed to sixteen COMET devices.

On the system side, the S/UNI-DUPLEX provides two serial LVDS interfaces one to the Operating Core Card and the other one to the Standby Core Card. The LVDS can be run through a backplane dedicated (point-to-point) transmission line, or it can be run through an external cable. Both ports on the S/UNI-DUPLEX are jumper configurable, allowing independent routing to the front connector or to the backplane.

The copper loop side on the COMET interfaces with the DS-1 or E1 physical layer through a front plate high-density connector.

A microprocessor and a hot swap circuit compliment the design. The Line Card has no data interface to the cPCI bus. Power is supplied with J1/P1 connectors. The Line Card has no 8 kHz PLL, as each COMET is equipped with a dejittering circuit.

#### 3.3.1. Line Card Software/Firmware

The boot-up and the default setup firmware for the S/UNI-DUPLEX and COMETs resides on the Line Card. Power-up and operating functions are executed by the embedded microprocessor.

The Line Card is equipped with a push-button RESET switch that is accessed from inside the card, to avoid accidental activation while plugging connectors and during other routine card/shelf maintenance. The RESET executes hardware reset to the entire board.

The ICC communication to the Line Card allows for reprogramming, however, that functionality may or may not be implemented with released firmware (see the WAN Card documentation for the latest in-system programmability).

A BDM port on the card, accessible only from inside the shelf, allows the user to develop the software/firmware.

In general, DSLAM entities can be remotely controlled with Inband Communication Channel (ICC) run over high-speed link. Customer needs to implement communications protocol. The ICC communication may allow for remote card reprogramming, and alarm and interrupt servicing. Also, microprocessor re-boot to the card may be communicated through ICC.

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

## 3.4. CPU Card

The CPU card is a stand-alone PC with the following specification:

- Pentium P55C (MMX) 233 MHz

- 512 kB L2 cache RAM

- a maximum of 384 MB RAM

- 3.2MB HD and a floppy DD installed as a sub-assembly (mezzanine) on top of the CPU card

- VGA, keyboard, mouse connectors

- Serial and parallel ports

- 10/100 Mb Ethernet

- cPCI bridge interface supporting 32 and 64 bit architecture

- OS compatibility with MS-DOS, Windows 98, Windows NT and VxWorks

- two-slot wide card

- multiple vendors.

The CPU card is always placed into slot-1 on the cPCI bacplane, marked with a triangle and "1" inside. The card width is equivalent to two cPCI slots, and the card extends into slot-2. The cPCI backplane is the "left-side system slot" type.

The operating system that runs the DSLAM Reference Design shelf is VxWorks.

PMC-Sierra provides software drivers for these individual devices: S/UNI-DUPLEX, S/UNI-VORTEX, S/UNI-APEX, and S/UNI-ATLAS; and a meta-driver for the VORTEX chipset (board driver). The drivers are configured to run on the VxWorks operating system.

## 3.5. LEDs on the Front Panel

The DSLAM cards are equipped with a set of LEDs for status indication mounted visible at the front plate. Core Card has additional LEDs inside the card.

The front panel LEDs on all cards are described in section 4 in this document.

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

# 3.6. Card Hot-Swap

The cPCI shelf operation requires all DSLAM cards to have a mechanism for hotswap ability. The hot swap addresses three major issues:

- Power rail issues supply voltage glitches during card insertion/removal.

The voltage glitch on a power rail may reset other cards (or create data corruption) and/or corrupt the cPCI bus data.

- CPCI interface issues the Core Card is equipped with a hot swap bridge and a pre-biasing circuit, allowing live insertion on the cPCI bus. The WAN Card and Line Card has no cPCI bus interface.

- Software readiness issues the Core Card has working ENUM# line, necessary for software hot swap. The ENUM# line, activated by a microswitch build-in into ejector handle, allows notification to the host processor card about Core Card removal or insertion. A blue led, required by cPCI hot swap standard, is ready to visualize software hot swap action.

Hot swap is advantageous in servicing DSLAM system. It allows removal of a malfunctioning card with minimal interruption to the system.

#### NOTE:

Hot swap software is not implemented in the VORTEX Chipset Driver. The hardware allows easy implementation of that functionality, if required by the customer.

## 3.6.1. Power Rail Hot Swap Control

The DSLAM cards are equipped with serial MOSFET transistors that control an inrush current and voltage spikes when performing a live insertion and removal of the card. The MOSFET transistors are gradually turned on, ramping the Vcc from 0 V to 5 V in about 50 ms. It allows "glitch-free" power rails during card maintenance. The Line Card and WAN Card control +5 V feeding rail. The Core Card controls +5 V and +3.3 V with two separate, very low Rdson MOSFET transistors.

The WAN and Line Cards use hot swap controller LTC1422. The Core Card board Rev. 3 uses LTC1645 – a dual line current sensing device. Both devices provide gate voltage ramp (for MOSFET transistors), and also current sensing for short circuit protection. The LTC1422 has a RESET pin for under-voltage detection. The Core Card board Rev. 3 uses LTC1326 for the RESET control.

Staged pins on the P1 connector that is mounted on the cPCI backplane detect card insertion and removal. The longest pins provide early voltage activating hot

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

swap controller only. The medium length pins mate high current ground and power rails (with no current). The shortest pin, which mates the last or disconnects the first, controls on/off action of the serial MOSFET transistors. The turn off action is abrupt.

#### 3.6.2. PCI Interface

The Core Card provides the means for data corruption free insertion onto the cPCI bus.

The cPCI data lines are pre-polarized with a 1.0 V bias voltage and 15 kohm resistors when the card is inserted (as required by "Hot Swap Recommendations"). The bias voltage is derived from the "early voltage" supplied by the longest pins on the P1 connector. The value of the "1.0 V" is a compromise minimizing a voltage glitch on active data lines, when the just-connected pin is charged to logic low or high. The data lines are held by PCI9054 in high-Z, until the local RESET line de-asserts. The host CPU is notified by the ENUM# line about shelf hardware/software change (some host cards may not be able to detect ENUM# line change).

On removal of the Core Card, the cPCI bridge is notified by the micro-switch in the ejector, and in turn, the bridge notifies the CPU card. The CPU shuts down communication and turns on the blue LED signaling to the operator readiness for card removal. For more information about the hot swap circuit, see the Core Card Reference Design.

The WAN Card and Line Card provide a means of hot swap on the power rails only. The cards do not provide an interface to the PCI data bus. The system can detect card insertion or removal indirectly from the Core Card through the high-speed link status or through the communication channel over the high-speed link.

#### 3.6.3. LVDS Interface

The LVDS interface is generally hot-swap compatible, in a sense that connecting and disconnecting LVDS cables should not cause uncontrolled data corruption on the system side. The S/UNI-DUPLEX and S/UNI-VORTEX are able to discard invalid cells at the high-speed receiver. Cell corruption is expected, triggering the LCD or LOS alarm with a traffic cease in the "received data" direction.

The main issue, with in-system connecting and disconnecting LVDS cables, is possible damage due to an excessive ground loop voltage when the service crew maintains cables or cards. Another related issue is data corruption or electrical

ISSUE 4

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

damage on an established connection due to excessive common mode noise, most likely from 60 Hz noise and the harmonics of AC power.

Ground differences between racks can easily reach single volts, and during a lightning strike it can go to tens of volts (or higher). That voltage, at best, will corrupt data, and may permanently damage the LVDS interface. Grounding problems can be resolved by using high-speed transformers. Lower cost solution is to use serial capacitors, which may help reject 60Hz (and harmonics) noise. Serial capacitors do not reject high frequency common mode voltage. The LVDS data is scrambled to avoid long runs of ones or zeros that can create baseline wander.

The Reference Design cards use transformers coupling on LVDS inputs on the WAN Card and Line Card (optionally, PCB allows serial capacitors). The Core Card uses serial capacitors due to real estate limitations. This allows to minimize 60 Hz ground loops on all cards. Capacitive coupling should be sufficient for the limited length of the LVDS interface in a shelf-to-shelf or rack-to-rack environment. System and facility design and appropriate grounding should prevent excessive common mode voltage between DSLAM entities.

WARNING: Transformers, together with too small value of the serial capacitors on another card, may have low frequency roll-off at a higher frequency, and may cause baseline wander and possible bit errors.

#### 3.7. Power Supply Requirement

The WAN Card and Line Card are designed to operate with +5 V supply only. The +5 V is fed through the J1 connector. The +3.3 V, required to power some circuitry, is derived from +5 V with a linear regulator on each card.

Core Card requires +5V and 3.3V supply. Supply current on +3.3V is in a range of 4 A, and it is not feasible to regulate down from +5V with an on-board linear regulator. The +5 V rail supplies 8 kHz PLL and a +2.5 V linear regulator, which is needed for the S/UNI-APEX core. If 3.3 V PLL is available (or not needed) and +3.3 V to +2.5 V linear regulator is available, then designers can easily eliminate the +5 V rail (from J1/P1 cPCI backplane) and supply Core Card with +3.3 V only.

DSLAM cards shall operate when powered with a standard switching power supply found throughout the PC industry. DSLAM cards or the DSLAM development shelf do not support 48V Telco type of supply rails.

PMC-Sierra, Inc.

REFERENCE DESIGN PMC-1990832

**ISSUE 4**

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

The current was measured on the DSLAM development shelf populated with cards as shown in Figure 5 earlier. Total current for host processor card, two Core Cards, two WAN Cards and two Line Cards is:

+5 V rail ~ 12.0 A

+3.3 V rail ~ 6.5 A

+12 V ~ 0.2 A

-12 V 0 A

With moderate traffic current on +5 V rail goes to 13 A and on +3.3 V to 7.2 A.

The current per DSLAM Card is measured at about:

Line Card +5 V rail ~ 1.8 A

WAN Card +5 V rail ~ 1.7 A

Core Card +5 V rail ~ 0.8 A +3.3 V rail ~ 4.1 A

Total power dissipation on the Core Card board Rev. 3 is estimated at P = (5.25 V \* 0.8 A) + (3.6 V \* 4.1 A) = 19 W. The Core Card requires forced airflow cooling system in enclosed shelves. While the Core Card board Rev. 3 was tested in an open development shelf, no excessive overheating was observed.

Supply current may vary at extreme voltage and temperature corners.

DSLAM REFERENCE DESIGN: SYSTEM DESIGN

#### 4. FRONT PANEL LEDS

DSLAM cards are equipped with rows of LEDs for status indication visible on the front panel. The front panel LEDs for all cards are shown in Figure 20 (in following sections).

## 4.1. Core Card LEDs

Some LED functionality may not be implemented in the current software driver. The following description is the preferred functionality of the LED display.

The basic set of four LEDs provides visual information about power lines and basic condition of microprocessor interface to all components. The basic LEDs are:

- +5 V, green indicates presence of +5 V

- +3.3 V, green indicates presence of +3.3 V