### 2.5V Wide-Range Frequency Clock Driver (60MHz - 200MHz)

#### **Features**

- · Low skew; low jitter PLL clock driver.

- 1 to 10 differential clock distribution (SSTL\_2).

- · Feedback pins for input to output synchronization.

- · PDB for power management.

- Spread spectrum tolerant inputs.

- · Auto-PD when input signal removed.

- · Choice of static phase offset for easy board tuning:

- -XXX = device pattern number for options listed below:

- PCV857-025 0 ps

- PCV857-1300 +50 ps

### **Product Description**

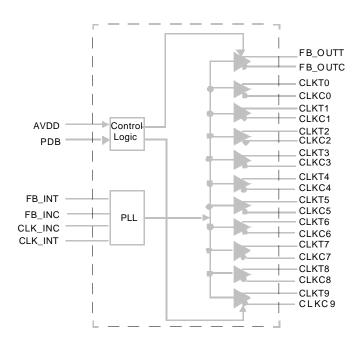

This PLL clock buffer is designed for a  $V_{DD}$  of 2.5V,  $AV_{DD}$  of 2.5V and differential data input and output levels. ASM5CVF857 is a zero-delay buffer that distributes a differential clock input pair (CLK\_INT, CLK\_INC) to ten differential pairs of clock outputs (CLKT[0:9], CLKC[0:9]) and one differential pair feedback clock output (FB\_OUT, FB\_OUTC). The clock outputs are controlled by the input clocks (CLK\_INT, CLKINC), the feedback clocks (FB\_INT, FB\_INC), the 2,5V LVCMOS input (PDB), and the analog power input (AV\_DD). When input (PDB) is low while power is applied, the receivers are disabled, the PLL is turned off, and the differential clock outputs are tri-stated. When  $AV_{DD}$  is grounded, the PLL is turned off and bypassed for test purposes.

When the input frequency is less than the operating frequency of the PLL, approximately 20MHz, the device will enter a low power mode. An input frequency detection circuit on the differential inputs, independent from the input buffers, will detect the low frequency

condition and perform the same low power features as and when the PDB input is low. When the input frequency increases to greater than approximately 20MHz, the PLL will be turned back on, the inputs and outputs will be enabled, and the PLL will obtain phase lock between the feedback clock pair (FB\_INT, FB\_INC) and the input clock pair (CLK\_INT, CLK\_INC).

The PLL in the ASM5CVF857 clock driver uses the input clocks (CLK\_INT, CLKINC) and the feedback clocks (FB\_INT, FB\_INC) to provide high-performance, low-skew, low-jitter output differential clocks (CLKT[0:9], CLKC[0:9]). ASM5CVF857 is also able to track spread spectrum clock (SSC) for reduced EMI.

ASM5CVF857 is characterized for operation from  $0^{\circ}$ C to  $85^{\circ}$ C.

### **Applications**

- DDR Memory Modules / Zero Delay Board Fan Out.

- Provides complete DDR DIMM logic solution with ASM4SSTVF16857, ASM4SSTVF16859 & ASM4SSTVF32852.

## **Specifications**

- Meets PC3200 specification for DDR-I 400 support.

- · Covers all DDRI speed grades.

#### **Switching Characteristics**

- CYCLE-CYCLE jitter: <50ps.</li>

- OUT-OUTPUT skew: <40ps.

- Period jitter: ±30ps.

## **Block Diagram**

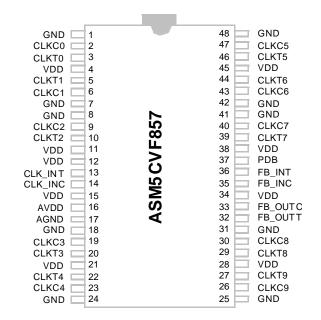

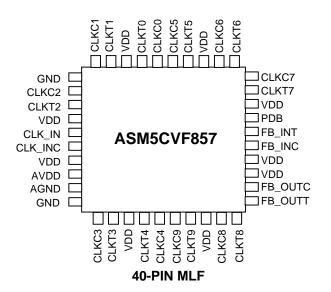

## **Pin Configuration**

rev 1.2

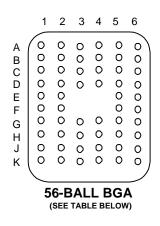

#### **56-BALL BGA**

|   | _1      | 2       | 3   | 4   | 5       | 6       |

|---|---------|---------|-----|-----|---------|---------|

| Α | CLKT0   | CLKC0   | GND | GND | CLKC5   | CLKT5   |

| В | CLKC1   | CLKT1   | VDD | VDD | CLKT6   | CLKC6   |

| С | GND     | GND     | NC  | NC  | GND     | GND     |

| D | CLKT2   | CLKC2   | NC  | NC  | CLKC7   | CLKC7   |

| Е | VDD     | VDD     | NB  | NB  | VDD     | PDB     |

| F | CLK_INT | CLK_INC | NB  | NB  | FB_INC  | FB_INT  |

| G | VDD     | AVDD    | NC  | NC  | FB_OUTC | VDD     |

| Н | AGND    | GND     | NC  | NC  | GND     | FB_OUTT |

| J | CLKC3   | CLKT3   | VDD | VDD | CLKT8   | CLKC8   |

| K | CLKT4   | CLKC4   | GND | GND | CLKC9   | CLKT9   |

# rev 1.2

# **Pin Description**

| Pin Number                           | Pin Name  | Pin<br>Type | Pin Description                                                                                                                                     |

|--------------------------------------|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 4, 11, 12, 15, 21, 28, 34, 38, 45    | VDD       | Р           | Power supply, 2.5V                                                                                                                                  |

| 1, 7, 8, 18, 24, 25, 31, 41, 42, 48  | GND       | Р           | Ground.                                                                                                                                             |

| 16                                   | AVDD      | Р           | Analog power supply, 2.5V.                                                                                                                          |

| 17                                   | AGND      | Р           | Analog ground.                                                                                                                                      |

| 27, 29, 39, 44, 46, 22, 20, 10, 5, 3 | CLKT(9:0) | 0           | "True" clock of differential pair outputs.                                                                                                          |

| 26, 30, 40, 43, 47, 23, 19, 9, 6, 2  | CLKC(9:0) | 0           | "Complementary" clocks of differential pair outputs.                                                                                                |

| 14                                   | CLK_INC   | 1           | "Complementary" reference clock input.                                                                                                              |

| 13                                   | CLK_INT   | -           | "True" reference clock input.                                                                                                                       |

| 33                                   | FB_OUTC   | 0           | "Complementary" feedback output dedicated for external feedback. It switches at the same frequency as the CLK. This output must be wired to FB_INC. |

| 32                                   | FB_OUTT   | 0           | "True" feedback output dedicated for external feedback. It switches at the same frequency as the CLK. This output must be wired to FB_INT.          |

| 36                                   | FB_INT    | -           | "True" feedback input provides feedback signal to the internal PLL for synchronization with CLK_INT to eliminate phase error.                       |

| 35                                   | FB_INC    | I           | "Complementary" feedback input provides signal to the internal PLL for synchronization with CLK_INC to eliminate phase error.                       |

| 37                                   | PDB       | I           | Power down. LVCMOS input.                                                                                                                           |

### rev 1.2

# **Functionality**

| Inputs     |     |         | Outputs |      |      |         | PLL State |              |

|------------|-----|---------|---------|------|------|---------|-----------|--------------|

| AVDD       | PDB | CLK_INT | CLK_INC | CLKT | CLKC | FB_OUTT | FB_OUTC   |              |

| GND        | Н   | L       | п       | L    | Н    | L       | Н         | Bypassed/Off |

| GND        | Н   | Н       | L       | Н    | L    | Н       | L         | Bypassed/Off |

| 2.5V (nom) | L   | L       | Н       | Z    | Z    | Z       | Z         | off          |

| 2.5V (nom) | L   | Н       | L       | Z    | Z    | Z       | Z         | off          |

| 2.5V (nom) | Н   | L       | Н       | L    | Н    | L       | Н         | on           |

| 2.5V (nom) | Н   | Н       | L       | Н    | L    | Н       | L         | on           |

| 2.5V (nom) | Х   | <20     | MHz     | Z    | Z    | Z       | Z         | off          |

# **Absolute Maximum Ratings**

| Parameter                     | Min       | Max       | Unit |

|-------------------------------|-----------|-----------|------|

| Supply voltage (VDD and AVDD) | -0.5      | 3.6       | V    |

| Logic Inputs                  | GND - 0.5 | VDD + 0.5 | V    |

| Ambient Operating Temperature | 0         | 85        | ûC   |

| Storage Temperature           | -65       | 150       | ûC   |

These are stress ratings only and functional operation is not implied. Exposure to absolute maximum ratings for prolonged periods may affect device reliability.

### rev 1.2

# **Electrical Characteristics - Input/Supply/Common Output Parameters**

$T_A$  = 0°76C to 85°C. Supply voltage AV<sub>DD</sub> and V<sub>DD</sub>=2.5V ± 0.2V (unless otherwise stated).

| Parameter                   | Symbol            | Conditions                                         | Min                  | Тур | Max  | Units |

|-----------------------------|-------------------|----------------------------------------------------|----------------------|-----|------|-------|

| Input high current          | I <sub>IH</sub>   | $V_{I} = V_{DD}$ or GND                            | 5                    |     |      | μΑ    |

| Input low current           | I <sub>IL</sub>   | $V_{I} = V_{DD}$ or GND                            |                      |     | 5    | μΑ    |

| Operating supply            | I <sub>DDQ</sub>  | $C_L = 0pF, R_L = 120\Omega, F_{CLK\_IN} = 200MHz$ |                      |     | 310  | mA    |

| current                     | I <sub>DDPD</sub> | PDB = GND, FCLK_IN=0MHz                            |                      | 100 | 200  | μΑ    |

| Supply Current on AVDD      | I <sub>ADD</sub>  | F <sub>CLK_IN</sub> = 200MHz                       |                      | 9   | 12   | mA    |

| Input clamp voltage         | Vık               | $V_{DDQ}$ =2.3 $V I_{IN}$ = -18 $mA$               |                      |     | -1.2 | V     |

| High-level output           | V <sub>OH</sub>   | Ι <sub>ΟΗ</sub> = -100μΑ                           | V <sub>DD</sub> -0.1 |     |      | ٧     |

| voltage                     | VOH               | I <sub>OH</sub> = -12mA                            | 1.7                  |     |      | V     |

| Low-level output            | V <sub>OL</sub>   | I <sub>OL</sub> = 100μA                            |                      |     | 0.1  | V     |

| voltage                     | VOL               | I <sub>OL</sub> = 12mA                             |                      |     | 0.6  | V     |

| Input capacitance*          | C <sub>IN</sub>   | $V_{I} = GND \text{ or } V_{DD}$                   | 2                    |     | 3.5  | pF    |

| Input capacitance variation | $C_{I(\Delta)}$   | $V_{OUT} = GND \text{ or } V_{DD}$                 | -0.25                |     | 0.25 | pF    |

<sup>\*</sup> Guaranteed by design at 200MHz; not 100% tested in production.

rev 1.2

Recommended Operating Conditions

$T_A = 0$ °C to 85°C. Supply voltage AV<sub>DD</sub> and V<sub>DD</sub>=2.5V  $\pm$  0.2V (unless otherwise stated).

| Parameter**                                    | Symbol            | Conditions                           | Min                       | Тур | Max                       | Unit |

|------------------------------------------------|-------------------|--------------------------------------|---------------------------|-----|---------------------------|------|

| Supply Voltage                                 | $V_{DD}, A_{VDD}$ |                                      | 2.3                       | 2.5 | 2.7                       | V    |

| Low level input voltage                        | V <sub>IL</sub>   | CLK_INT, CLK_INC, FB_INT, FB_INC     |                           | 0.4 | V <sub>DD</sub> /2 - 0.18 | ٧    |

| High level input                               | V <sub>IH</sub>   | CLK_INT, CLK_INC, FB_INT, FB_INC     | V <sub>DD</sub> /2 + 0.18 | 2.1 |                           | V    |

| voltage                                        |                   | PDB                                  | 1.7                       |     | V <sub>DD</sub> + 0.3     | ٧    |

| DC input signal voltage <sup>#</sup>           | V <sub>IN</sub>   |                                      | -0.3                      |     | V <sub>DD</sub> + 0.3     | V    |

| Differential input                             | V <sub>ID</sub>   | DC: CLK_INT, CLK_INC, FB_INT, FB_INC | 0.36                      |     | V <sub>DD</sub> + 0.6     | ٧    |

| signal voltage <sup>\$</sup>                   |                   | AC: CLK_INT, CLK_INC, FB_INT, FB_INC | 0.7                       |     | V <sub>DD</sub> + 0.6     | ٧    |

| Output differential cross voltage <sup>®</sup> | V <sub>OX</sub>   |                                      | V <sub>DD</sub> /2 - 0.15 |     | V <sub>DD</sub> /2 + 0.15 | ٧    |

| Input differential cross voltage               | V <sub>IX</sub>   |                                      | V <sub>DD</sub> /2 - 0.2  |     | V <sub>DD</sub> /2 + 0.2  | ٧    |

| High-level output current                      | I <sub>OH</sub>   |                                      |                           |     | -12                       | mA   |

| Low-level output current                       | I <sub>OL</sub>   |                                      |                           |     | 12                        | mA   |

| Operating free-air temperature                 | T <sub>A</sub>    |                                      | 0                         |     | 85                        | °C   |

<sup>\*\*:</sup> Unused inputs must be held high or low to prevent them from floating.

<sup>#:</sup> DC input signal voltage specifies the allowable DC execution of differential

<sup>\$:</sup> Differential inputs signal voltages specify the differential voltage [VTR-VCP] required for switching where VTR is the true input level and VCT is the complementary input level.

<sup>@:</sup> Differential cross-point voltage is expected to track variations of V<sub>DD</sub> and is the voltage at which the differential signal must be crossing.

rev 1.2 Timing Requirements\*\*

| Parameter                   | Symbol              | Conditions  | Min | Max | Units |

|-----------------------------|---------------------|-------------|-----|-----|-------|

| Operating clock frequency   | freq <sub>op</sub>  | 2.5V ± 0.2V | 60  | 220 | MHz   |

| Application Frequency Range | freq <sub>app</sub> | 2.5V ± 0.2V | 95  | 220 | MHz   |

| Input clock duty cycle      | d <sub>tin</sub>    |             | 40  | 60  | %     |

| CLK stabilization           | T <sub>STAB</sub>   |             |     | 100 | μs    |

## **Switching Characteristics\*\***

| Parameter                                | Symbol                              | Conditions                               | Min       | Тур      | Max        | Units    |

|------------------------------------------|-------------------------------------|------------------------------------------|-----------|----------|------------|----------|

| Low-to-high level propagation delay time | t <sub>PLH</sub> *                  | CLK_IN to any output                     |           | 3.5      |            | ns       |

| High-to-low level propagation delay time | t <sub>PHL</sub> *                  | CLK_IN to any output                     |           | 3.5      |            | ns       |

| Output enable time                       | t <sub>en</sub>                     | PDB to any output                        |           | 3        |            | ns       |

| Output disable time                      | t <sub>dis</sub>                    | PDB to any output                        |           | 3        |            | ns       |

| Period Jitter                            | t <sub>jit(per)</sub>               | 100MHz to 200MHz                         | -30       |          | 30         | ps       |

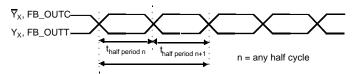

| Half-period jitter                       | t <sub>jit(hper)</sub>              | 100MHz to 200MHz                         | -75       |          | 75         | ps       |

| Input clock slew rate                    | t <sub>sl(I)</sub>                  |                                          | 1         |          | 4          | v/ns     |

| Output clock slew rate                   | t <sub>sl(o)</sub>                  | 100/133/167/200 MHz                      | 1         |          | 2          | v/ns     |

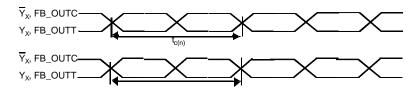

| Cycle-to-cycle jitter                    | t <sub>cyc</sub> -t <sub>cyc</sub>  | 100 MHz to 200MHz                        | -50       |          | 50         | ps       |

| Static phase offset                      | t <sub>(phase error)</sub> #        |                                          | -50       | 0        | 50         | ps       |

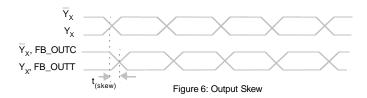

| Output-to-output skew                    | t <sub>skew</sub>                   |                                          |           | 40       | 60         | ps       |

| The PLL on the ASM5CVF857 is capable     |                                     | the above parameters whiling parameters. | e support | ting SSC | synthesize | ers with |

|                                          | SSC modulation                      | on frequency                             | 30.00     |          | 50.00      | kHz      |

|                                          | SSC clock input frequency deviation |                                          | 0.00      |          | -0.50      | %        |

|                                          | PLL loop bandwidth                  |                                          | 2         |          |            | MHz      |

|                                          | Phase angle                         |                                          |           | -0.031   | 0          |          |

<sup>#:</sup> Static phase offset does not include jitter.

Note: While the pulse skew is almost constant over frequency, the duty cycle error increases at higher frequencies. This

is due to the formula: duty cycle =  $t_{WH}/tC$  where the cycle ( $t_C$ ) decreases as the frequency goes up.

Note: Switching characteristics guaranteed for application frequency range.

<sup>\*\*</sup>  $T_A = 0 - 85$ °C. Supply voltage AV<sub>DD</sub>,  $V_{DD}$ =2.5V ± 0.2V (unless otherwise stated).

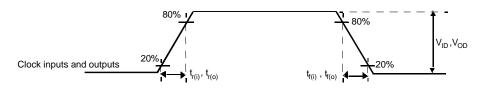

#### **Parameter Measurement Information**

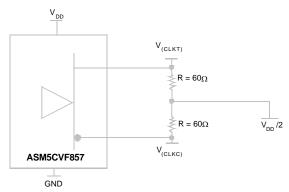

Figure 1: IBIS Model Output Load

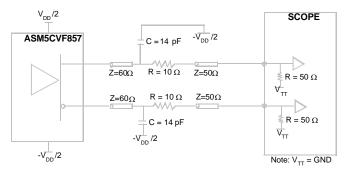

Figure 2: Output Load Test Circuit

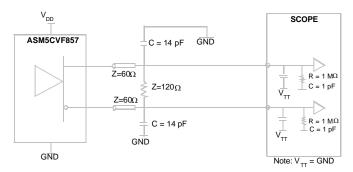

Figure 3: Output Load Test Circuit for Crossing Point

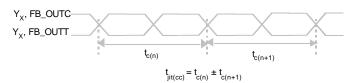

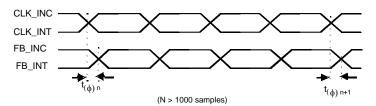

Figure 4: Cycle-to-Cycle Jitter Period

Figure 5: Static Phase Offset

fo= average input frequency measured at CLK\_INT/CLK\_INC

Figure 7: Period Jitter

$f_0$ = average input frequency measured at CLK\_INT/CLK\_INC

Figure 8: Half-Period Jitter

Figure 9: Input and Output Slew rates

rev 1.2

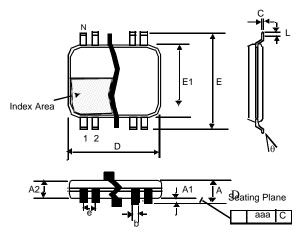

Package Dimensions (6.10mm (240 mil) body, 0.50mm (0.020 mil) pitch TSSOP)

| Symbol | Dimensio       | ns (mm) | Dimensions (inches) |       |  |

|--------|----------------|---------|---------------------|-------|--|

|        | Min            | Max     | Min                 | Max   |  |

| Α      | -              | 1.20    | -                   | 0.047 |  |

| A1     | 0.05           | 0.15    | 0.002               | 0.006 |  |

| A2     | 0.80           | 1.05    | 0.32                | 0.041 |  |

| b      | 0.17           | 0.27    | 0.007               | 0.011 |  |

| С      | 0.09           | 0.20    | 0.0035              | 0.008 |  |

| D      |                | See Va  | riations            |       |  |

| Е      | 8.10 E         | Basic   | 0.319 Basic         |       |  |

| E1     | 6.00           | 6.20    | 0.236               | 0.244 |  |

| е      | 0.50 E         | Basic   | 0.20 Basic          |       |  |

| L      | 0.45           | 0.75    | 0.018               | 0.030 |  |

| N      | See Variations |         |                     |       |  |

| θ      | 0°             | 8°      | 0°                  | 8°    |  |

| aaa    | -              | 0.10    | -                   | 0.004 |  |

|    | D (N  | <b>ЛМ</b> ) | D(i   | nch)  |

|----|-------|-------------|-------|-------|

|    | Min   | Max         | Min   | Max   |

| 48 | 12.40 | 12.60       | 0.488 | 0.496 |

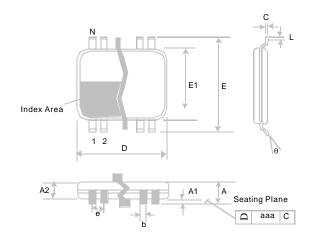

# Package Dimensions (4.40mm (1713 mil) body, 0.40 mm (16 mil) pitch TVSOP)

| Symbol | Dimensi        | ons (mm)  | Dimensions (inches) |         |  |

|--------|----------------|-----------|---------------------|---------|--|

|        | Min            | Max       | Min                 | Max     |  |

| Α      | -              | 1.20      | -                   | 0.047   |  |

| A1     | 0.05           | 0.15      | 0.002               | 0.006   |  |

| A2     | 0.80           | 1.05      | 0.32                | 0.041   |  |

| b      | 0.17           | 0.27      | 0.007               | 0.011   |  |

| С      | 0.09           | 0.20      | 0.0035              | 0.008   |  |

| D      |                | See Varia | ations              |         |  |

| E      | 8.10           | Basic     | 0.319 Basic         |         |  |

| E1     | 6.00           | 6.20      | 0.236               | 0.244   |  |

| е      | 0.50           | Basic     | 0.20                | ) Basic |  |

| L      | 0.45           | 0.75      | 0.018               | 0.030   |  |

| N      | See Variations |           |                     |         |  |

| θ      | 0°             | 8°        | 0°                  | 8°      |  |

| aaa    | -              | 0.10      | -                   | 0.004   |  |

| N  | D (N  | /М)   | D(i   | nch)  |

|----|-------|-------|-------|-------|

|    | Min   | Max   | Min   | Max   |

| 48 | 12.40 | 12.60 | 0.488 | 0.496 |

## rev 1.2

# **Ordering Codes**

| Ordering Number | Marking    | Package Type                 | Quantity Per Reel | Temperature |

|-----------------|------------|------------------------------|-------------------|-------------|

| ASM5CVF857-48TT | AS5CVF857T | 48-pin TSSOP, tube           |                   | 0°C to 70°C |

| ASM5CVF857-48TR | AS5CVF857T | 48-pin TSSOP, tape & reel    | 2500              | 0°C to 70°C |

| ASM5CVF857-48VT | AS5CVF857V | 48-pin TVSOP, tube           |                   | 0°C to 70°C |

| ASM5CVF857-48VR | AS5CVF857V | 48-pin TVSOP, tape & reel    | 2500              | 0°C to 70°C |

| ASM5CVF857-56BT | AS5CVF857B | 56-pin Ball BGA, tube        |                   | 0°C to 70°C |

| ASM5CVF857-56BR | AS5CVF857B | 56-pin Ball BGA, tape & reel | 2500              | 0°C to 70°C |

| ASM5CVF857-40QT | AS5CVF857M | 40-pin QFN, tube             |                   | 0°C to 70°C |

| ASM5CVF857-40QR | AS5CVF857M | 40-pin QFN, tape & reel      | 2500              | 0°C to 70°C |

rev 1.2

Alliance Semiconductor Corporation 2595, Augustine Drive, Santa Clara, CA 95054 Tel# 408-855-4900 Fax: 408-855-4999

rax: 408-855-499 www.alsc.com Copyright © Alliance Semiconductor All Rights Reserved Advance Information Part Number: ASM5CVF857 Document Version: v1.1

© Copyright 2003 Alliance Semiconductor Corporation. All rights reserved. Our three-point logo, our name and Intelliwatt are trademarks or registered trademarks of Alliance. All other brand and product names may be the trademarks of their respective companies. Alliance reserves the right to make changes to this document and its products at any time without notice. Alliance assumes no responsibility for any errors that may appear in this document. The data contained herein represents Alliance's best data and/or estimates at the time of issuance. Alliance reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. Alliance does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of Alliance products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to in Alliance's Terms and Conditions of Sale (which are available from Alliance). All sales of Alliance products are made exclusively according to Alliance's Terms and Conditions of Sale. The purchase of products from Alliance does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not authorize its products for use as critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result in significant injury to the user, and the inclusion of Alliance products in such life-supporting systems implies that the manufacturer assumes all risk of such use and agrees to indemnify Alliance against all claims arising from such use.